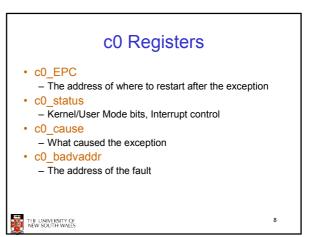

| C                                                                                                         | :0 Re   | gis  | ter | S                          |                  |                              |    |

|-----------------------------------------------------------------------------------------------------------|---------|------|-----|----------------------------|------------------|------------------------------|----|

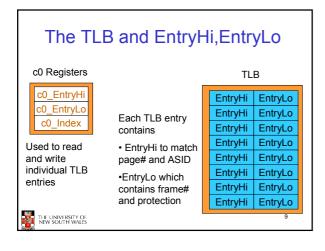

| 31                                                                                                        | 12      | 11   |     |                            | 6                | 5                            | 0  |

| VPN                                                                                                       |         | ASID |     |                            |                  | 0                            |    |

| EntryHi Register (TLB key fields)                                                                         | 12      | 11   | 10  | 9                          | 8                | 7                            | 0  |

| PFN<br>EntryLo Register (TLB data fields)                                                                 |         | N    | D   | V                          | G                | 0                            |    |

| <ul> <li>N = Not cacheabl</li> <li>D = Dirty = Write</li> <li>G = Global (ignor<br/>in lookup)</li> </ul> | protect | • (  |     | 3 entri<br>sed vi<br>ocess | a soft<br>or 0 r | ware th<br>egisters<br>tryLo |    |

| THE UNIVERSITY OF<br>NEW SOUTH WALES                                                                      |         |      |     |                            |                  |                              | 10 |

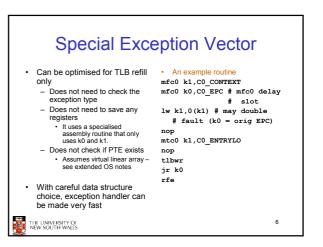

### Cooprocessor 0 registers on a refill exception

### $\textbf{c0}.\textbf{EPC} \leftarrow \textbf{PC}$

$\begin{array}{l} \text{c0.cause.ExcCode} \leftarrow \text{TLBL} \text{ ; if read fault} \\ \text{c0.cause.ExcCode} \leftarrow \text{TLBS} \text{ ; if write fault} \\ \text{c0.BadVaddr} \leftarrow \text{faulting address} \\ \text{c0.EntryHi.VPN} \leftarrow \text{faulting address} \\ \text{c0.status} \leftarrow \text{kernel mode, interrupts disabled.} \\ \text{c0.PC} \leftarrow 0x8000\ 0000 \end{array}$

THE UNIVERSITY OF NEW SOUTH WALES

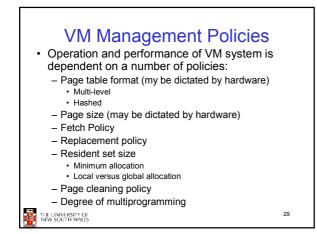

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

<section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

13

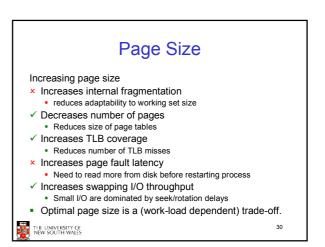

| Hopoyavoll/Multico | 512 words (48-bit)             |  |

|--------------------|--------------------------------|--|

| Honeywell/Multics  | 1K words (36-bit)              |  |

| IBM 370/XA         | 4K bytes                       |  |

| DEC VAX            | 512 bytes                      |  |

| IBM AS/400         | 512 bytes                      |  |

| Intel Pentium      | 4K and 4M bytes                |  |

| ARM                | 4K and 64K bytes               |  |

| MIPS R4000         | 4k – 16M bytes in powers of 4  |  |

| DEC Alpha          | 8K - 4M bytes in powers of 8   |  |

| UltraSPARC         | 8K – 4M bytes in powers of 8   |  |

| PowerPC            | 4K bytes + "blocks"            |  |

| Intel IA-64        | 4K – 256M bytes in powers of 4 |  |

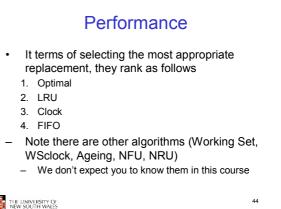

# Least Recently Used (LRU) Toss the least recently used page Assumes that page that has not been referenced for a long time is unlikely to be referenced in the near future Will work if locality holds Implementation requires a time stamp to be kept for

- Implementation requires a time stamp to be kept to each page, updated on every reference

Impossible to implement efficiently

- Most practical algorithms are approximations of LRU

39

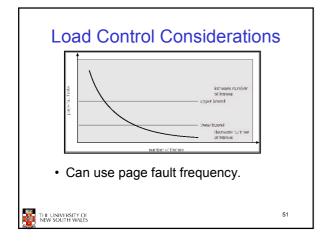

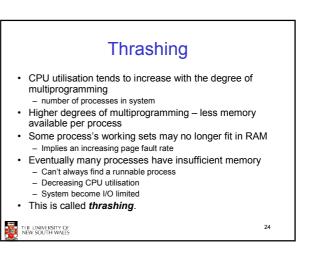

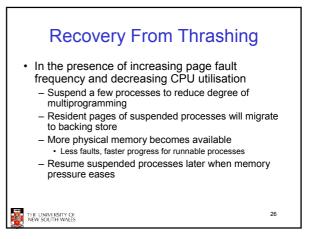

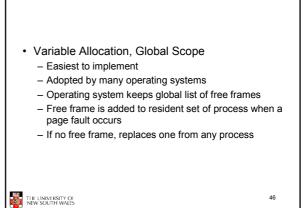

## Load Control (Degree of multiprogramming)

Determines the number of runnable processes

#### Controlled by: – Admission control

Only let new process's threads enter ready state if enough memory is available

### Suspension: Move all threads of some process into a special suspended state

Swap complete process image of suspended process to disk

50

Trade-off

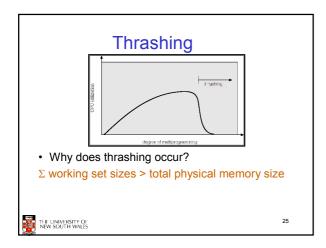

Too many processes will lead to thrashing

- Too few will lead to to idle CPU or excessive swapping

THE UNIVERSITY OF NEW SOUTH WALES

•