#### **COMP 3221**

### **Microprocessors and Embedded Systems**

**Lectures 28: Exceptions & Interrupts - II**

http://www.cse.unsw.edu.au/~cs3221

October, 2003 Saeid Nooshabadi

saeid@unsw.edu.au

Saeid Nooshabadi

#### **Overview**

- Instruction Set Support for Exceptions

- °Role of O/S in Handling Exceptions

- Prioritized Exceptions

- °Re-entrant Exception Routine

COMP3221 lec28-exception-II.2

Saeid Nooshabadi

Reset

**SWI**

**Data Abort**

Reserved

**IRO**

FIO

Prefetch Abort

0x00000004 Undefined Instr

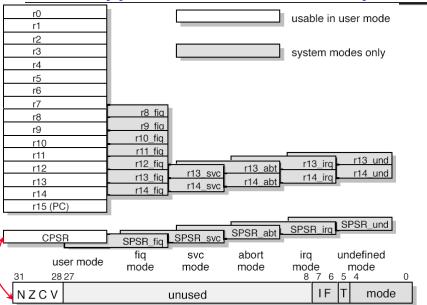

#### **Review: Support for ARM Modes of Operations**

#### **Review: Exception Handling and the Vector Table**

0x00000000

800000008

0x000000C

0x00000010

0x00000014

0x0000018

0x0000001C

- When an exception occurs, the core:

- Copies CPSR into SPSR <mode>

- Sets appropriate CPSR bits

- Interrupt disable flags if appropriate.

- Maps in appropriate banked registers

- Stores the "return address" in LR\_<mode>

- Sets PC to vector address

- Single instruction stored at these locations should be a branch to a handler

- o To return, exception handler needs to:

- Restore CPSR from SPSR <mode>

- Restore PC from LR\_<mode> via movs pc, 1r or subs pc 1r, #4

### **Review: Privileged vs User Mode**

- ° Privileged Modes vs. User Mode: OS can provide security and fairness

- °swi: provides a way for a programmer to avoid having to know details of each I/O device.

- °To be acceptable, Exception handler must:

- service all Exceptions (no drops)

- service by priority

- make all users believe that no Exception has occurred

COMP3221 lec28-exception-II.5

Saeid Nooshabadi

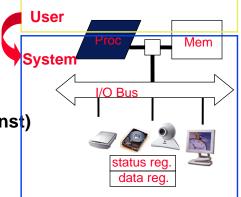

#### **Review: OS: I/O Requirements**

- °The OS must be able to prevent:

- The user program from communicating with the I/O device directly

- °If user programs could perform I/O directly:

- No protection to the shared I/O resources

- °3 types of communication are required:

- The OS must be able to give commands to the I/O devices

- The I/O device notify OS when the I/O device has completed an operation or an error

- Data transfers between memory and I/O device

COMP3221 lec28-exception-II.6

Saeid Nooshabadi

## **Review: Crossing the System Boundary**

System loads user program into memory and 'gives' it use of the processor

- °Switch back

- swi

- request service

- I/O

- exception (und. Inst)

- Interrupt

## Instruction Set Support for OS (#1/2)

- ° How to turn off interrupts during Exception routine?

- ° Bits in CPSR determines whether or not interrupts disabled:

- Interrupt Request bit (I) (1 ⇒ disabled, 0 ⇒ enabled)

- Once an exception occurs (I) bit sets to to 1 automatically

- Return from exception restores the original value

- <u>Fast Interrupt Request bit (F)</u> only gets disabled if an fast Interrupt occurs

| 31 28 | 27 8   | 7  | 6 | 5 | 4    | 0_ |

|-------|--------|----|---|---|------|----|

| NZCV  | unused | ΙF | = | Т | mode |    |

#### **Instruction Set Support for OS (#2/2)**

- °How to prevent user program from turning off interrupts (forever)?

- \* Interrupt Request bit (I) and Fast Interrupt Request bit (F) bits can only be changed from the privileged modes

COMP3221 lec28-exception-II.9

Saeid Nooshabadi

#### **Multiple Simultaneous Exceptions/Interrupts**

°Problem: What if Data Abort exception and an I/O interrupt (printer ready, for example) come in both at the same time?

### °Options:

- drop any conflicting interrupts/ exceptions: unrealistic, they may be important

- simultaneously handle multiple interrupts exceptions: unrealistic, may not be able to synchronize them (such as with multiple I/O interrupts)

- queue them for later handling: sounds good

COMP3221 lec28-exception-II.10 Saeid Nooshabadi

# **Exceptions Prioritization in ARM**

| Exception Type               | Priority<br>(1=High, 6=Low) |

|------------------------------|-----------------------------|

| Reset                        | 1                           |

| Data Abort                   | 2                           |

| Fast Interrupt (FIQ)         | 3                           |

| Interrupt (IRQ)              | 4                           |

| Prefetch Abort               | 5                           |

| Software Interrupt (SW       | l) 6                        |

| <b>Undefined Instruction</b> | 6                           |

## FIQ Priority

- °Placing the Data Abort exception above the FIQ exception in the priority list ensures that the Data Abort is actually registered before the FIQ is handled.

- °The Data Abort handler is entered first but control is then passed immediately to the FIQ handler.

- °Once the FIQ has been handled, control returns to the Data Abort Handler.

- This means that the data transfer error does not escape detection as it would if the FIQ were handled first.

COMP3221 lec28-exception-II.11 Saeid Nooshabadi COMP3221 lec28-exception-II.12 Saeid Nooshabadi

#### **Hardware support for FIQ**

- ° Extra register set r12\_fiq r8\_fiq in FIQ bank would mean that they don't need to be saved.

- ° That means faster processing

- ° FIQ vector address at 0x0000001C is the last vector, and therefore can start executing immediately without a branch instruction

| 0x00000000                | Reset                  |

|---------------------------|------------------------|

| 0x00000004                | <b>Undefined Instr</b> |

| 0x00000008                | SWI                    |

| 0x000000C                 | Prefetch Abort         |

| 0x00000010                | Data Abort             |

| 0x00000014                | Reserved               |

| 0x00000018                | IRQ                    |

| 0x0000001C                | _                      |

| COMP3221 lec28-exception- |                        |

Saeid Nooshabadi

### **ARM Support for Preempting Exceptions**

- ° ARM Architecture Support to simplify software:

- An Exception Process sets IRQ bits (disables it).

- No further IRQ interrupt is possible

- However, No exception can disable FIQ interrupt

- ° If an FIQ interrupt comes while servicing an exception

- Take FIQ immediately

- Return to interrupted exception code as soon as no more FIQ Interrupt

- State information for the preempted exception are saved on banked registers and as well as some internal registers

#### **Preempting Exceptions by Interrupts**

- Ouestion: Suppose we're dealing with a computer running a nuclear facility. What if we're handling an Floating Point Divide by 0 Exception and a Nuclear Meltdown Imminent interrupt comes in?

- ° Answer: We need to categorize and allow some interrupts preempt other Exceptions so we can handle them in order of urgency: emergency vs. luxury.

COMP3221 lec28-exception-II.14

## **Reading Material**

- °Experiment 5 Documentation

- Steve Furber: ARM System On-Chip;

2nd Ed, Addison-Wesley, 2000, ISBN:

0-201-67519-6. Chapter 5.

- ARM Architecture Reference Manual

2<sup>nd</sup> Ed, Addison-Wesley, 2001, ISBN: 0 201-73719-1, Part A, Exceptions,

chapter A2 Section 6

COMP3221 lec28-exception-II.15 Saeid Nooshabadi COMP3221 lec28-exception-II.16 Saeid Nooshabadi

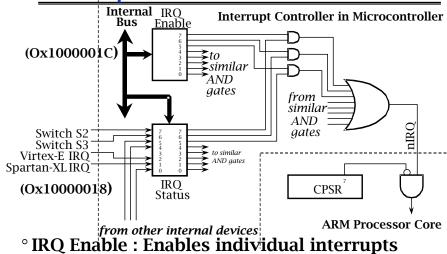

#### So Many Devices One FIQ/IRQ

- ° Two interrupt request signals FIQ and IRQ never enough for all of the I/O devices

- ° Need a mechanism to attach multiple devices to the same IRQ pin.

- Solution: Use Interrupt Controller to attach multiple devices to the same IRQ pin.

- Interrupt Controller controls how multiple peripherals can interrupt the ARM processor. Essentially, the interrupt controller acts as a large AND-OR gate

- In the event of an IRQ a combination of hardware and software techniques are required to detect the sources of interrupt and provide a system of priority and queuing.

COMP3221 lec28-exception-II.17

Saeid Nooshabadi

Saeid Nooshabadi

IRO

ARM

Processor

Core

CPSR 7

### **Interrupt Controller in DSLMU/Komodo**

- ° IRQ Status: Indicates rasing interrupt.

- ° Prioritization: in software

Saeid Nooshabadi

### DSLMU/Komodo IRQ Status/Enable Regs

| Bit | Mode | Function                                     |

|-----|------|----------------------------------------------|

| 7   | R/W  | Push-button switch S2 on the Expansion Board |

| 6   | R/W  | Push-button switch S3 on the Expansion Board |

| 5   | R/W  | Serial port transmitter ready                |

| 4   | R/W  | Serial port receiver ready                   |

| 3   | _    | (Reserved)                                   |

| 2   | R/W  | Xilinx Virtex-E interrupt request            |

| 1   | R/W  | Xilinx Spartan-XL interrupt request          |

| 0   | R/W  | Timer Compare interrupt request              |

IRO status reg. address = 0x10000018

IRQ Enable reg. address = 0x1000001C COMP3221 lec28-exception-ll.19

### **IRQ Interrupt Levels in ARM?**

°What are they?

- °It depends what the ARM chip is inside of: differ by app: GameBoy, Digital Set top Box, Digital Answering Machine, Digital Satellite Decoder, Pocket PC, Mobile **Phone**

- ARM architecture and Interrupt controller enables priorities for different I/O events

## **Improving Data Transfer Performance**

- °Thus far: OS give commands to I/O, I/O device notify OS when the I/O device completed operation or an error

- °What about data transfer to I/O device?

- Processor busy doing loads/stores between memory and I/O Data Register

- °Ideal: specify the block of memory to be transferred, be notified on completion?

- Direct Memory Access (DMA): a simple computer transfers a block of data to/from memory and I/O. interrupting upon done

COMP3221 lec28-exception-II.21

Saeid Nooshabadi

#### **Example: FIQ Code for DMA controller**

°DMA code from Disk Device to Memory

```

.data

Count:

.word 4096

.space 4096

Start:

.text

Initial: ldr a1, =Count

ldr a1, [a1]

; No. chars

ldr a2, =Start ; next char

ldr a3, DiskControl

Wait:

tst a3,1

; select Ready

; spinwait

beg Wait

ldrb a4, DiskData; get byte

strb a4, [a2], #1; transfer,

: Start++

a1, a1,#1

subs

: Count--

;next char

bne

Wait

DMA "computer" in parallel with CPU

COMP3221 lec28-exception-II.22

```

## **Re-entrant Interrupt Routine?**

- ° Prioritization and queuing of interrupts attached to IRQ Interrupt controller requires one interrupt preempting another interrupt (reentrant interrupts)

- All exceptions set IRQ disable interrupt bit (I)

- FIQ can interrupt IRQ and other exceptions

- ° FIQ sets FIQ disable interrupt bit (F) as well

- Objective of the second of

- ° Interrupt service Routine needs to save:

- Return address on lr irg for the pre-empted IRQ handler on IRQ Mode Stack

- all registers that it is going to use on IRQ Mode Stack

- Reset the IRQ disable bit

- ° Same thing for FIQ

Saeid Nooshabadi

## **Pre-empting Other Exceptions by IRQ?**

- °All exceptions set IRQ disable interrupt bit (I)

- FIQ can interrupt IRQ and other exceptions

- \*How allow IRQ interrupts to interrupt other exceptions (other than IRQ and FIQ exceptions)?

- Interrupt service Routine needs to save:

- all registers that it is going to use on IRQ Mode Stack

- Reset the IRQ disable bit

#### **IRQ Controller Support for Queuing and Priority**

### °IRQ Controller Support to simplify software:

- An Interrupt Process cannot be preempted by Exception <u>at same</u> or lower <u>"level"</u>

- When an interrupt is handled, take the highest priority interrupt on the queue

- If a higher priority interrupt comes in while servicing a lower priority one

- Preempt the lower priority one and take the higher priority one

- current priority value is pushed onto a first-in lastout stack and the current priority is updated to the higher priority.

- Return to interrupted code as soon as no more Interrupts at a higher level

- On return the current interrupt level is updated with the last stored interrupt level from the stack.

#### **Things to Remember**

- ° Privileged Mode v. User Mode: OS can provide security and fairness

- Exceptions prioritization in the case of multiple concurrent exceptions.

- °Multiple devices can be connected to single IRQ interrupt via an Interrupt Controller.

- °Re-entrant Interrupt: One interrupt preempting another interrupt.

- Prioritization and queuing of interrupts in hardware or software is required for this to work.

COMP3221 lec28-exception-II.26

Saeid Nooshabadi