#### **Overview**

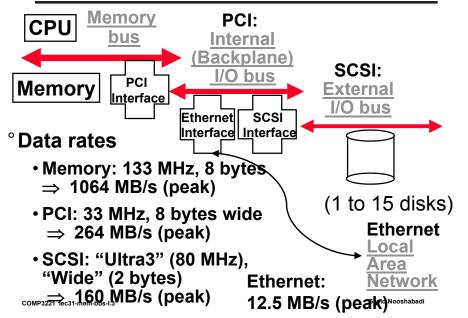

## **Review: Buses in a PC: Connect a few devices**

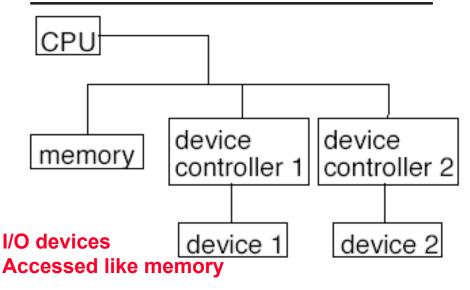

# **Review: Computers with Memory Mapped I/O**

COMP3221 lec31-mem-bus-l.4

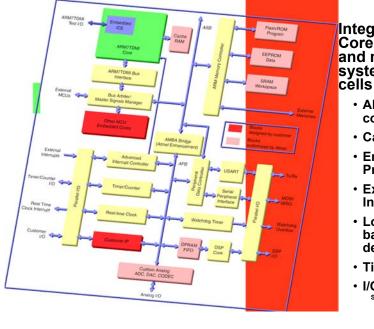

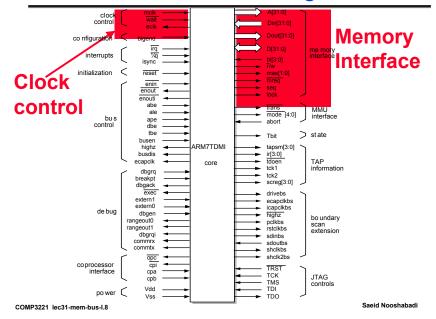

#### **Big Picture: A System on a Chip**

Integration of Core Processor and many subsystem microcells

- ARM7TDMI core

- Cache RAM

- Embedded Co-Processors

- External Mem Interface

- Low bandwidth I/O devices

- Timers

- I/O ports Saeid Nooshabadi

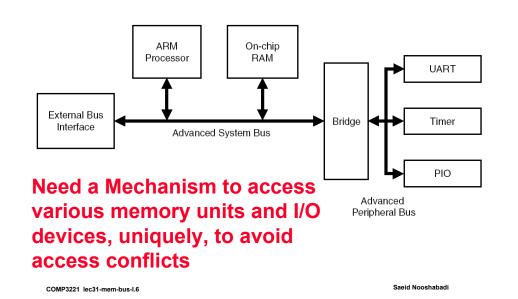

# **ARM System Architecture**

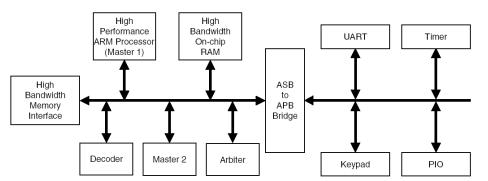

#### **ARM System Architecture with Multiple Masters**

Need a Mechanism to allow various Processing units to access the Memory Bus without causing conflict

COMP3221 lec31-mem-bus-I.7

Saeid Nooshabadi

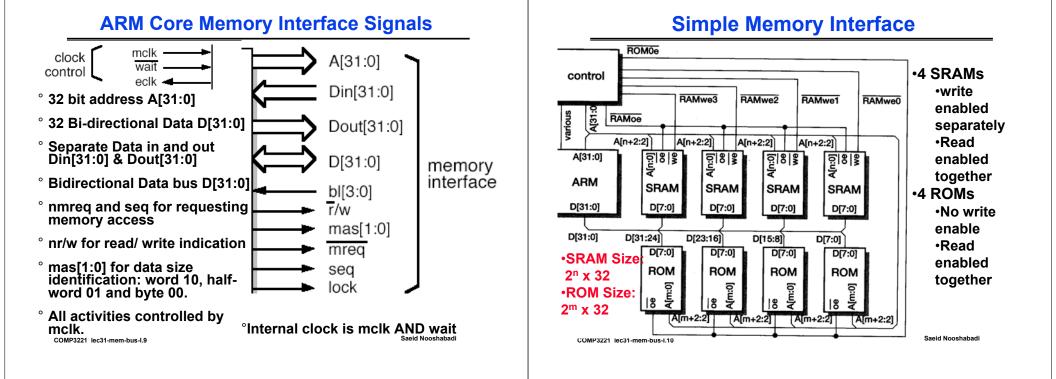

#### **ARM Core Interface Signals**

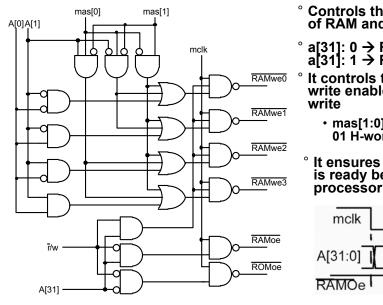

### **Simple Memory Decoder Control**

- ° Controls the Activation of RAM and ROM

- a[31]:  $0 \rightarrow ROM$ a 31:  $1 \rightarrow RAM$

- It controls the byte write enables during

- mas[1:0]: 00 Byte, 01 H-word, 10 Word

- ° It ensures that data is ready before processor continues.

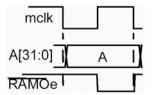

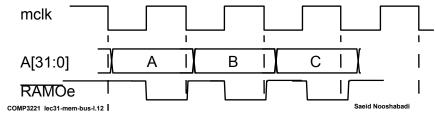

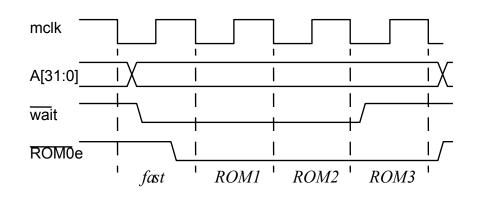

#### SRAM/ROM Memory Timing

<sup>°</sup>Address should be stable during the falling edge

#### °SRAM is fast, ROM is slow

- ROM needs more time. Slows the system

- Solutions?

- Slow down the MCLK clock; loose performance

- Use Wait states; more complex control

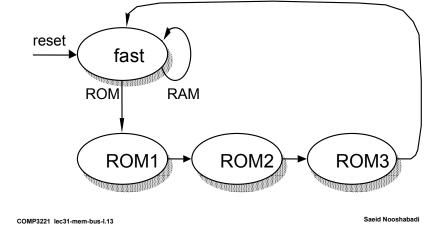

### **ROM Wait Control State Transition**

# °ROM access requires 4 clock cycles

#### °RAM access is fast

# Timing Diagram for for ROM Wait States

COMP3221 lec31-mem-bus-l.14

Saeid Nooshabadi

# **Improving Performance**

- <sup>°</sup> Processor internal operations cycles do not need access to memory

- Mem. Access is much slower than internal operations.

**Operations can**

- Use wait states for mem Accesses Internal

- ° mreq = 1 internal operation

° mreg = 0 memory access reset decode RAM RAM RAM RAM RAM ROM1 ROM2 ROM3 Saeid Nooshabadi

#### **DRAM Interface**

#### <sup>°</sup> Dynamic RAM Features:

- much cheaper than SRAM

- more capacity than SRAM

- slower than SRAM

### °Widely used in Computer Systems

#### **DRAM Organisation**

#### °Two dimensional matrix

- <sup>°</sup>Bits are accesses by:

- Accepting row and column addresses down the same multiplexed address bus ras First Row address is presented and

#### decodei array of latch latched by ras memorv signal cells • Next column<sub>A[n:0]</sub> address is presented and latched by cas latch mux signal

cas

#### COMP3221 lec31-mem-bus-l.17

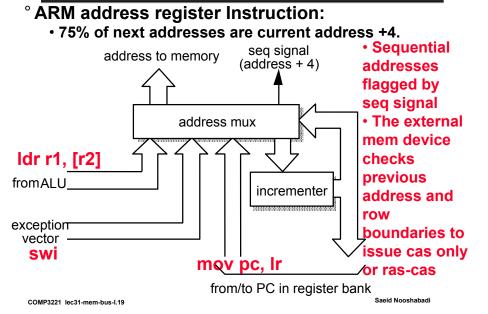

### **ARM Solution to cas-only Access**

Data out

# Making DRAM Access Fast

- Accessing data in the same row using cas-only access is 2 3 times faster

- cas-only access does not activate the cell matrix

- If next accesses is within the same row, a new column address may be presented just by applying a cas-only access.

- <sup>°</sup> Fact: Most processor addresses are sequential (75%)

- <sup>°</sup> If we had a way of knowing that that the next address is sequential with respect with the current address (current address + 4), then we could only assert cas and make DRAM access fast

#### ° Difficulty?

• Detecting early in memory access cycle that the next address is in the same row.

COMP3221 lec31-mem-bus-I.18

Saeid Nooshabad

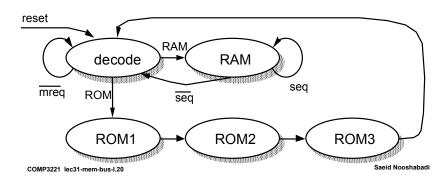

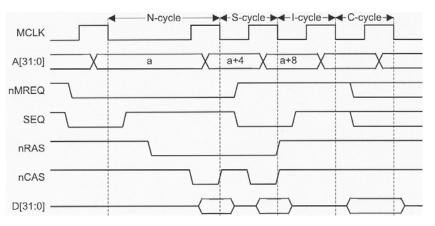

### **Revised State Transition Diagram**

- ° seg = 1: sequential address

- ° seg = 0: non-sequential

- ° mreg = 1 internal operation

- ° mreg = 0 memory access

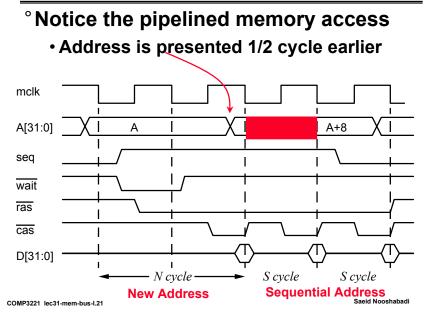

### **DRAM Timing Diagram**

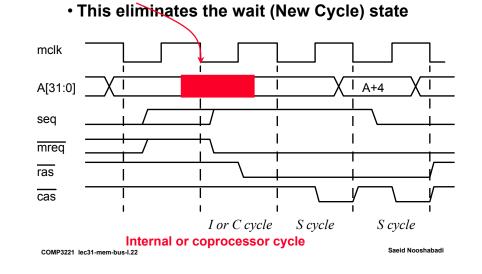

## **DRAM Timing Diagram after an Internal Cycle**

# ° During internal operations cycles, a memory access cycle can be set up in advance.

### **Memory Access Timing Summary**

#### °Notice the pipelined memory access

•Address is presented 1/2 cycle earlier

COMP3221 lec31-mem-bus-I.23

Saeid Nooshabadi

#### **Reading Material**

<sup>°</sup> Steve Furber: ARM System On-Chip; 2nd Ed, Addison-Wesley, 2000, ISBN: 0-201-67519-6. Chapter 8.

#### Conclusion

- <sup>°</sup> Memory interfacing can degrade performance

- °Can improve performance by increasing the clock frequency and allocating differing clock cycles for each memory access type

- ° cas-only accesses in DRAM are 2 to 3 times faster than ras cas accesses.

COMP3221 lec31-mem-bus-l.25

Saeid Nooshabadi