#### **Outline**

**COMP 3221**

**Microprocessors and Embedded Systems**

Lectures 33: Cache Memory - I

#### http://www.cse.unsw.edu.au/~cs3221

### October, 2003

# Saeid Nooshabadi

## saeid@unsw.edu.au

COMP3221 lec33-Cache-I.1Some of the slides are adopted from David Patterson (UCB) Saeid Nooshabadi

#### <sup>°</sup>Memory Hierarchy

- °On-Chip SRAM

- <sup>°</sup>Direct-Mapped Cache

COMP3221 lec33-Cache-I.2

Saeid Nooshabadi

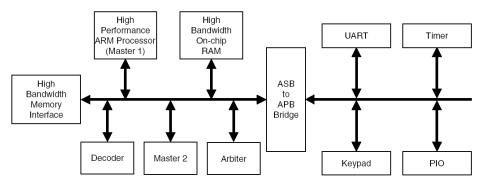

# **Review: ARM System Architecture**

Fast on-Chip RAM External Lower Speed SRAM, Slower DRAM, Much Slower Flash-ROM

### Memory Hierarchy (#1/5)

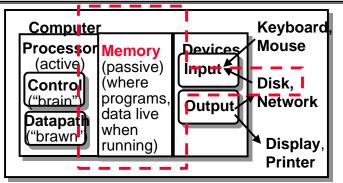

#### ° Processor

- executes programs

- runs on order of nanoseconds to picoseconds

- needs to access code and data for programs: where are these?

#### °Disk

- HUGE capacity (virtually limitless)

- VERY slow: runs on order of milliseconds

- so how do we account for this gap?

COMP3221 lec33-Cache-I.3

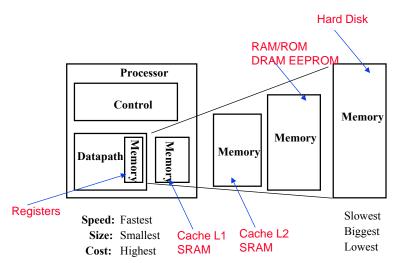

#### Memory Hierarchy (#2/5) Memory Hierarchy (#3/5) Processor <sup>°</sup>Memory (DRAM) Increasing **Higher** smaller than disk (not limitless capacity) Distance from Proc., Levels in Level 1 contains subset of data on disk: basically Decreasing portions of programs that are currently memory Level 2 cost / MB being run hierarchy Level 3 much faster than disk: memory accesses don't slow down processor quite as much Lower . . . • Problem: memory is still too slow Level n (hundreds of nanoseconds) Solution: add more layers Size of memory at each level - On-chip Memory - On-chip Caches Saeid Nooshabadi Saeid Nooshabadi COMP3221 lec33-Cache-L5 COMP3221 lec33-Cache-I.6 Memory Hierarchy (#4/5) Memory Hierarchy (#5/5)

If level is closer to Processor, it must be:

smaller

- Smalle

- faster

- subset of all lower levels (contains most recently used data)

- contain at least all the data in all higher levels

- <sup>°</sup>Lowest Level (usually disk) contains all available data

### **Memory Hierarchy**

#### °Purpose:

COMP3221 lec33-Cache-L9

• Faster access to large memory from processor

#### Memory Hierarchy Analogy: Library (#1/2)

- ° You're writing an assignment paper (Processor) at a table in the Library

- °Library is equivalent to disk

- essentially limitless capacity

- very slow to retrieve a book

#### °Table is memory

- smaller capacity: means you must return book when table fills up

- easier and faster to find a book there once you've already retrieved it

COMP3221 lec33-Cache-I.10

Saeid Nooshabadi

# Memory Hierarchy Analogy: Library (#2/2)

# <sup>o</sup>Open books on table are on-chip memory/<u>cache</u>

- smaller capacity: can have very few open books fit on table; again, when table fills up, you must close a book

- much, much faster to retrieve data

- °Illusion created: whole library open on the tabletop

- Keep as many recently used books open on table as possible since likely to use again

- Also keep as many books on table as possible, since faster than going to library shelves

## **Memory Hierarchy Basis**

- <sup>°</sup>Disk contains everything.

- <sup>o</sup>When Processor needs something, bring it into to all higher levels of memory.

- <sup>°</sup>On-chip Memory/Cache contains copies of data in memory that are being used.

- <sup>°</sup>Memory contains copies of data on disk that are being used.

- <sup>o</sup>Entire idea is based on <u>Temporal</u> <u>Locality</u>: if we use it now, we'll want to use it again soon (a Big Idea)

Saeid Nooshabadi

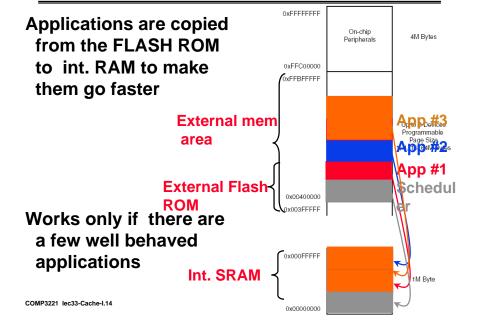

#### **On Chip SRAM Memory**

- °Provides fast (zero wait state access to program and data)

- ° It occupies a portion of address space.

- <sup>o</sup>Requires explicit management by the programmers.

- Part of the program has to copy itself from slow external slow memory (eg flash-rom), into the internal on-chip ram and start executing from there

- Works well for limited number of programs where, the program behaviour and space requirement is well defined.

COMP3221 lec33-Cache-I.13

#### A Case for Cache

# °On-Chip SRAM requires explicit management by the programmer

- Possible for an embedded system with small number of well defined programs

- Not possible for a general purpose processor with many programs, where the application mix cannot be determined in advanced

- Explicit memory management become difficult

#### <sup>o</sup>We need a mechanism where the copying from the slow external RAM to Int. memory is automated by hardware (Cache!)

#### **DSLMU on-Chip RAM**

#### Cache Design

<sup>°</sup>How do we organize cache?

- <sup>o</sup> Where does each memory address map to? (Remember that cache is subset of memory, so multiple memory addresses map to the same cache location.) (Books from many shelves are on the same table)

- <sup>o</sup> How do we know which elements are in cache?

- <sup>°</sup>How do we quickly locate them?

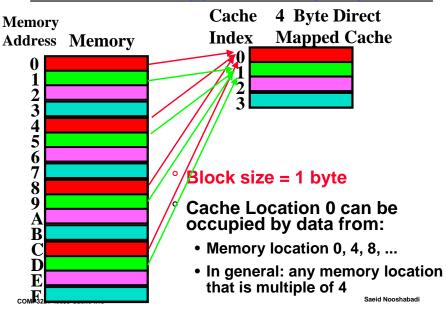

#### Direct-Mapped Cache (#1/2)

- <sup>o</sup> In a <u>direct-mapped cache</u>, each memory address is associated with one possible <u>block</u> within the cache

- Therefore, we only need to look in a single location in the cache for the data to see if it exists in the cache

- Block is the unit of transfer between cache and memory

#### **Direct-Mapped Cache (#2/2)**

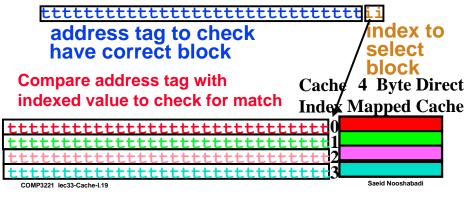

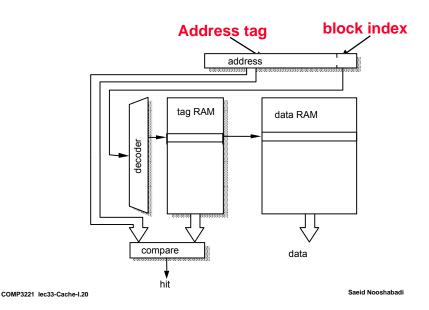

#### **Issues with Direct-Mapped**

Saeid Nooshabadi

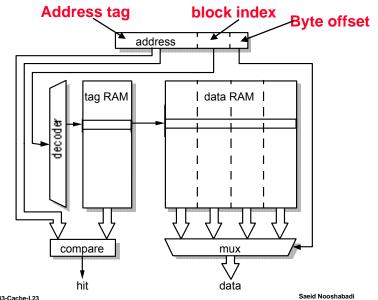

° Since multiple memory addresses map to same cache index, how do we tell which one is in there?

° Store the address information along with the data in the cache

#### Address from the processor

COMP3221 lec33-Cache-I.17

#### **Direct-Mapped with 1 Byte Blocks Example**

#### **Reading Material**

Steve Furber: ARM System On-Chip; 2nd Ed, Addison-Wesley, 2000, ISBN: 0-201-67519-6. Chapter 10.

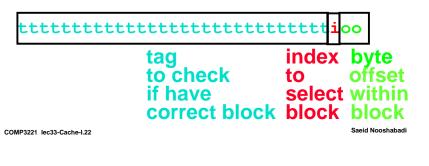

#### Issues with Direct-Mapped with Larger Blocks

- <sup>o</sup> Since multiple memory blocks map to same cache index, how do we tell which one is in there?

- <sup>°</sup>How do we select the bytes in the block?

- <sup>o</sup>Result: divide memory address into three fields

COMP3221 lec33-Cache-I.21

Saeid Nooshabadi

# **Direct-Mapped with Larger Blocks Example**

#### Direct-Mapped Cache Terminology

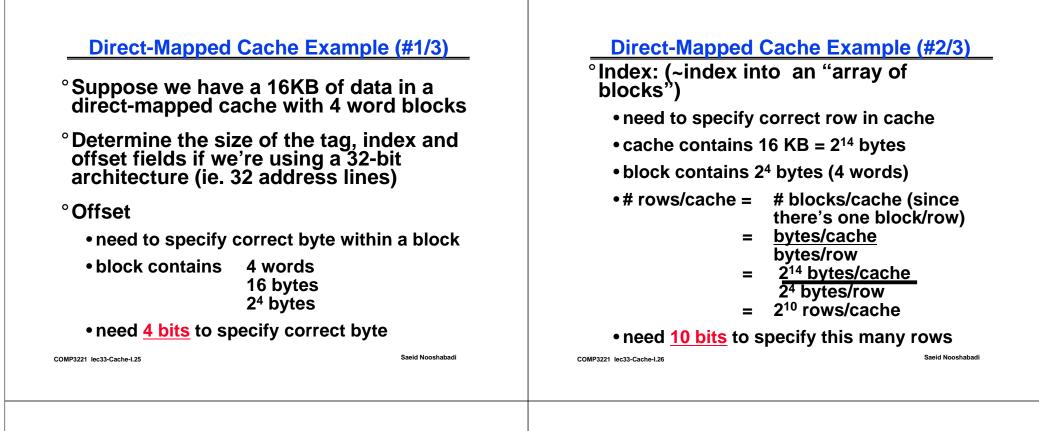

- °All fields are read as unsigned integers.

- <sup>o</sup>Index: specifies the cache index (which "row" or "line" of the cache we should look in)

- °Offset: once we've found correct block, specifies which byte within the block we want

- Tag: the remaining bits after offset and index are determined; these are used to distinguish between all the memory addresses that map to the same location

COMP3221 lec33-Cache-I.24

# Direct-Mapped Cache Example (#3/3)

°Tag: use remaining bits as tag

- tag length = mem addr length

- offset - index

- = 32 4 10 bits

- = 18 bits

• so tag is leftmost 18 bits of memory address

#### °Why not full 32 bit address as tag?

- All bytes within block need same address (-4b)

- Index must be same for every address within a block, so its redundant in tag check, thus can leave off to save memory (- 10 bits in this

#### **Things to Remember**

<sup>°</sup>We would like to have the capacity of disk at the speed of the processor: unfortunately this is not feasible.

- °So we create a memory hierarchy:

- each successively higher level contains "most used" data from next lower level

- exploits temporal locality

- <sup>°</sup>Locality of reference is a Big Idea