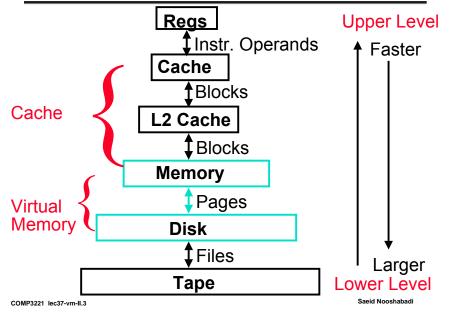

### **Review: Memory Hierarchy**

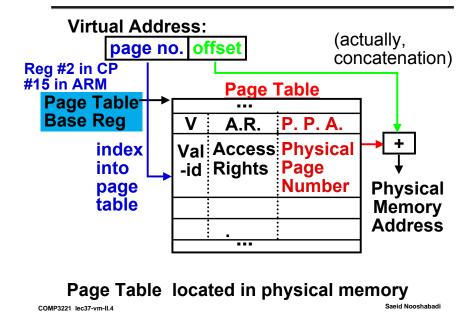

### Review: Address Mapping: Page Table

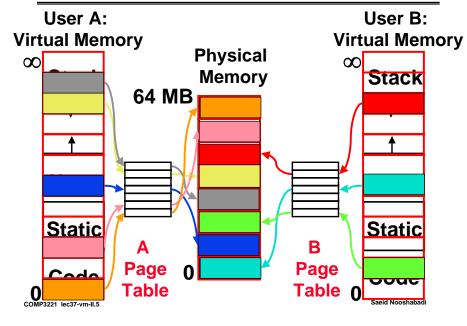

### **Paging/Virtual Memory for Multiple Pocesses**

### Analogy

- <sup>o</sup> Book title like virtual address (ARM System On-Chip)

- <sup>o</sup> Library of Congress call number like (QA76.5.F8643 2000) physical address

- ° Card (or online-page) catalogue like page table, indicating mapping from book title to call number

- <sup>o</sup> On card (or online-page) info for book, indicating in local library vs. in another branch like valid bit indicating in main memory vs. on disk

- On card (or online-page), available for 2-hour in library use (vs. 2-week checkout) like access rights

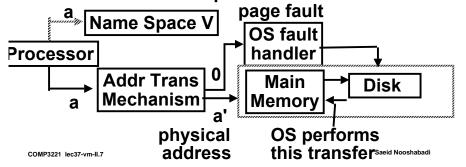

#### Address Map, Mathematically Speaking

V =  $\{0, 1, ..., n - 1\}$  virtual page address space (n > m)

$M = \{0, 1, ..., m - 1\}$  physical page address space MAP: V --> M U  $\{\theta\}$  page address mapping function

MAP(a) = a' if data at virtual address  $\underline{a}$ is present in physical address  $\underline{a'}$  and  $\underline{a'} = \theta$  if data at virtual address a is not present in M

### **Comparing the 2 Levels of Hierarchy**

- <sup>o</sup>Cache Version Virtual Memory vers.

- <sup>°</sup>Block or Line Page

- ° Miss

COMP3221 lec37-ym-ll.6

- Page Fault

- °Block Size: 32-64B Page Size: 4K-8KB

- Placement: Fully Associative Direct Mapped, N-way Set Associative

- <sup>°</sup>Replacement: LRU or Random

- Least Recently Used (LRU)

- ° Write Thru or Back Write Back

COMP3221 lec37-vm-ll.8

#### **Notes on Page Table**

- °Solves Fragmentation problem: all chunks same size, so all holes can be used

- °OS must reserve "<u>Swap Space</u>" on disk for each process

- °To grow a process, ask Operating System

- If unused pages, OS uses them first

- If not, OS swaps some old pages to disk

- (Least Recently Used to pick pages to swap)

- ° Each process has its own Page Table

- ° Will add details, but Page Table is essence of Virtual Memory COMP3221 lec37-ym-ll.9

### Virtual Memory Problem #1

### °Not enough physical memory!

- Only, say, 64 MB of physical memory

- N processes, each 4GB of virtual memory!

- Could have 1K virtual pages/physical page!

- ° Spatial Locality to the rescue

- Each page is 4 KB, lots of nearby references

- No matter how big program is, at any time only accessing a few pages

- "<u>Working Set</u>": recently used pages

COMP3221 lec37-vm-ll.10

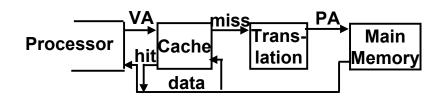

# Virtual Address and a Cache (#1/2)

- Cache operates on Virtual addresses.

- ARM Strategy

- •The advantage: If in cache the translation is not required.

•Disadvantage: Several copies of the the same physical memory location may be present in several cache blocks. (Synonyms problem). Gives rise to some complications!

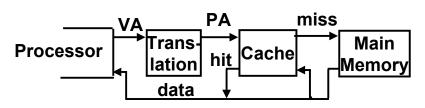

# Virtual Address and a Cache (#2/2)

Cache typically operates on physical addresses on most other systems.

• Address Translation (Page Table access) is another memory access for each program memory access!

Accessing memory for Page Table to get Physical address →(Slow Operation)

Need to fix this!

COMP3221 lec37-vm-II.12

| Reading Material                                                                                                              | Virtual Memory Problem #2                                                                                                           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <ul> <li>Steve Furber: ARM System On-Chip; 2nd<br/>Ed, Addison-Wesley, 2000, ISBN: 0-201-<br/>67519-6. Chapter 10.</li> </ul> | ° <u>Map every address ⇒ 1 extra memory</u><br>accesses for every memory access                                                     |  |  |  |

|                                                                                                                               | <sup>o</sup> Observation: since locality in pages of<br>data, must be locality in <u>virtual</u><br><u>addresses</u> of those pages |  |  |  |

|                                                                                                                               | <sup>o</sup> Why not use a cache of virtual to<br>physical address translations to make<br>translation fast? (small is fast)        |  |  |  |

|                                                                                                                               | <sup>o</sup> For historical reasons, this cache is<br>called a <u>Translation Lookaside Buffer</u> ,<br>or <u>TLB</u>               |  |  |  |

| COMP3221 lec37-vm-ll.13 Saeid Nooshabadi                                                                                      | COMP3221 lec37-vm-ll.14 Saeid Nooshabadi                                                                                            |  |  |  |

### Typical TLB Format

| Virtual<br>Address | Physical<br>Address | Dirty | Ref | Valid | Access<br>Rights |

|--------------------|---------------------|-------|-----|-------|------------------|

|                    |                     |       |     |       |                  |

- TLB just a cache on the page table mappings

- TLB access time comparable to cache (much less than main memory access time)

- <u>Ref</u>: Used to help calculate LRU on replacement

- Dirty: since use write back, need to know whether or not to write page to disk when replaced

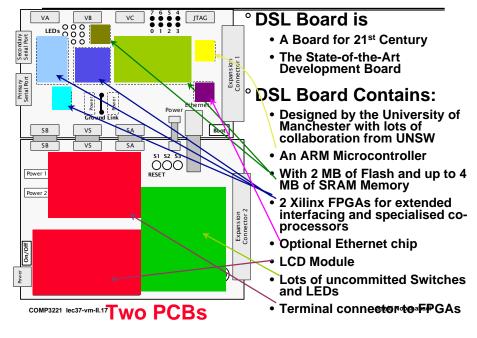

#### °PROJECTS IN DIGITAL HARDWARE DESIGN FOR 4<sup>th</sup> Year

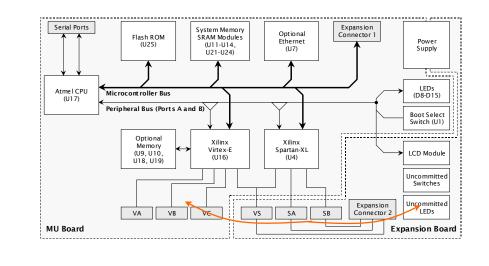

#### **Digital Systems Laboratory Hardware**

### **DSLMU Hardware Block Diagram**

COMP3221 lec37-vm-II.18

### Projects with Digital Systems Lab Board

- <sup>°</sup> Project 1: Design of a Vector Floating Point Co-Processor for ARM Core:

- <sup>°</sup> Aim: The Aim of this project is to built Floating Point Vector Processor On the Vertex FPGA.

- <sup>o</sup> Degree of Difficulty: Hard, and Challenging

- <sup>o</sup> Ability: Number Representation, Digital System Design, DSP

#### **Projects with Digital Systems Board**

- Project 2: Design of a Fixed Point DSP for ARM Core:

- Aim: The Aim of this project is to built DSP Optimised Processor (Single Cycle MAC Processor/ Distributed Arithmetic) On the Vertex FPGA.

- Degree of Difficulty: Hard, and Challenging

- Ability: Number Representation, Digital System Design, DSP

COMP3221 lec37-vm-II.20

#### **Projects with Digital Systems Board**

- Project 3: Development of a Simple Multi tasking Operating System

- <sup>°</sup> Aim: The Aim of this project is Development of a Simple Multi tasking Operating System with Simple Virtual Memory Protection for on-board program monitoring and debugging.

- Degree of Difficulty: Moderate, and some Challenges

- Ability: Software Development, Basic Operating Systems

- Application: Our Undergraduate/Post Graduate Teaching

- Advantage: Make yourself Immortal!

COMP3221 lec37-vm-II.21

Saeid Nooshabadi

## **Projects with Digital Systems Board**

- Project 4: Interfacing GNU debugging tool with on-board emulator (Komodo)

- Aim: The Aim of this project is to Interface GNU debugging tool with on-board emulator program to facilitate source-level debugging and monitoring.

- Degree of Difficulty: Moderate to Hard with some Challenges

- Ability: Software Development, Basic Operating Systems

- Application: Our Undergraduate/Post Graduate Teaching

- ocomp322 Advantage: Make yourself Immortal! Saeid Nooshabadi

# Projects with Digital Systems Board

- Project 5: Porting of uCliux to DSL Board

- Aim: The Aim of this project is to port real-time Operating System uClinx to DSL Board.

- Degree of Difficulty: Hard, and Challenging

- Ability: Software Development, Basic Operating Systems

<sup>o</sup> Start: http://www.uclinux.org<sub>saeid Nooshabadi</sub>

# **Projects with Digital Systems Board**

- Project 6: Design of an embedded Internet enabled device for remote control and monitoring

- <sup>°</sup> Aim: The aim of this project is to design an embedded interface device using programmbale microcontrollers and FPGAs, to wireless devices in one hand and modem/lan on the other hand. The unit collects the data through the wireless picodevices and in turn transfers the data via modem or lan to a remote server via TCP/IP stacks. It should also be possible to control the picodevices remotely. The challenge is to build the various software layers, on a realtime operating system like eCos to do the task.

- <sup>9</sup> Degree of Difficulty: Hard, and Challenging

- <sup>°</sup> Ability: Software Development, Basic Operating Systems, basic Hardware Interfacing

COMP3221 lec37-vm-II.24

#### **Projects with Digital Systems Board**

- Project 7: Design of an embedded Internet enabled device for remote control and monitoring

- <sup>°</sup> Aim: The aim of this project is to design an embedded interface device using programmable microcontrollers and FPGAs, to control and monitor the viewing of cable TV channels. This embedded unit controls a TV tuner, in a real time fashion, based on the control information it receives remotely. The unit is connected to the internet via a cable modem. It can be controlled and monitored via a remote device (a PC). The challenge is to build the various software layers, on a realtime operating system like eCos to do the task.

- ° Degree of Difficulty: Hard, and Challenging

- ° Ability: Software Development, Basic Operating Systems, basic Hardware Interfacing COMP3221 lec37-vm-II.25

#### **Projects with Digital Systems Board**

- ° Project 8: PS/2 and USB Controller For DSL Board

- Aim: The aim of this project is to design an PS/2 and USB Controller using the on-board FPGA chips.

- ° Degree of Difficulty: Hard, and Challenging

- Ability: Hardware Development, Basic

Software development

COMP3221 lec37-vm-II.26

**Projects with Digital Systems Board**

- Project 9: Frame Grabber Device for CMOS Digital Camera

- Aim: The aim of this project is to build a high resolution web camera using a Kodak KAC-1310 CMOS image sensor. The pixel data would buffered in SRAM /SDRAM, compressed and uploaded through the Internet interface for display on a PC.

- ° Degree of Difficulty: Very Hard, and Challenging

- ° Ability: DSP, Hardware Development, Basic Software development Said Nooshabadi

### Projects with Digital Systems Board

- <sup>°</sup> Project 10: Audio Signal Processing

- Aim: The aim of this project is interface a codec to a DSP Audio Signal Processor/ Compressor built on the on-Board FPGAs

- Degree of Difficulty: Moderate to Hard, and Challenging

- Ability: DSP, Hardware Development, Basic Software development

#### Things to Remember (#1/2)

- <sup>o</sup> Apply Principle of Locality Recursively

- <sup>°</sup>Reduce Miss Penalty? add a (L2) cache

- <sup>°</sup>Manage memory to disk? Treat as cache

- Included protection as bonus, now critical

- Use <u>Page Table</u> of mappings vs. tag/data in cache

- <sup>°</sup>Virtual memory to Physical Memory Translation too slow?

- Add a cache of Virtual to Physical Address Translations, called a <u>TLB</u>

#### Things to Remember (#2/2)

- Virtual Memory allows protected sharing of memory between processes with less swapping to disk, less fragmentation than always swap or base/bound

- <sup>o</sup> Spatial Locality means Working Set of Pages is all that must be in memory for process to run fairly well

COMP3221 lec37-vm-II.30

Saeid Nooshabadi

#### **Things to Remember**

- <sup>o</sup> Spatial Locality means Working Set of Pages is all that must be in memory for process to run fairly well

- °Virtual memory to Physical Memory Translation too slow?

- Add a cache of Virtual to Physical Address Translations, called a <u>TLB</u>

- TLB to reduce performance cost of VM

COMP3221 lec37-ym-ll.29