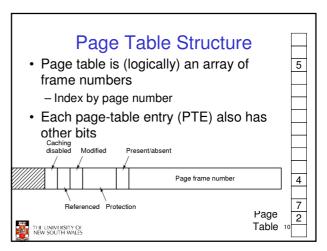

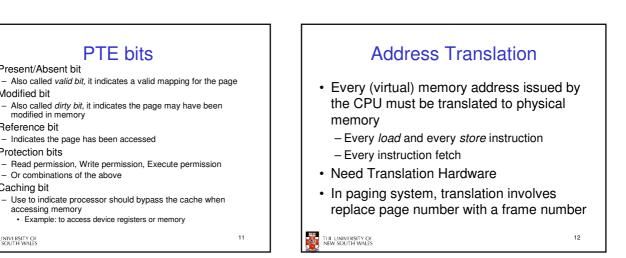

· Present/Absent bit

Modified bit

Reference bit

Protection bits

Caching bit

THE UNIVERSITY OF NEW SOUTH WALES

accessing memory

THE UNIVERSITY OF NEW SOUTH WALES

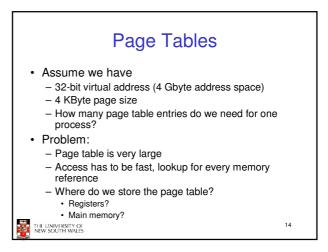

## 21

24

20

THE UNIVERSITY OF NEW SOUTH WALES

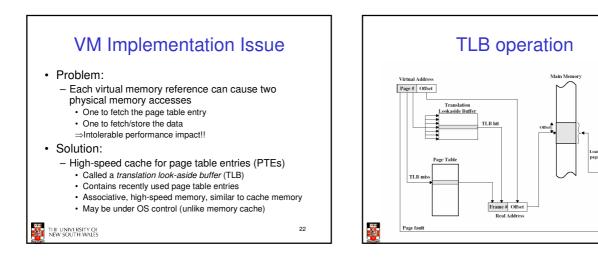

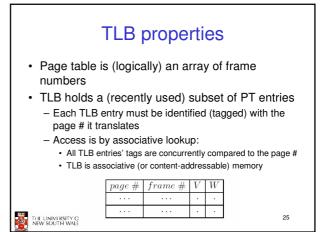

## Translation Lookaside BufferGiven a virtual address, processor examines the

- TLB

- If matching PTE found (*TLB hit*), the address is translated

- Otherwise (*TLB miss*), the page number is used to index the process's page table

- If PT contains a valid entry, reload TLB and restart

- Otherwise, (page fault) check if page is on disk

- If on disk, swap it in

- · Otherwise, allocate a new page or raise an exception

THE UNIVERSITY OF NEW SOUTH WALES

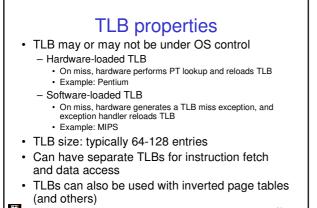

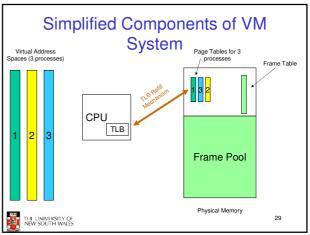

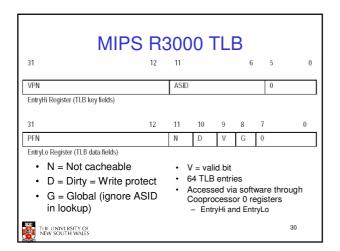

## TLB and context switching TLB is a shared piece of hardware Page tables are per-process (address space) TLB entries are *process-specific*On context switch need to *flush* the TLB (invalidate all entries) high context-switching overhead (Intel x86) or tag entries with *address-space ID* (ASID) called a *tagged TLB*used (in some form) on all modern architectures TLB entry: ASID, page #, frame #, valid and write-protect bits

27

THE UNIVERSITY OF NEW SOUTH WALES

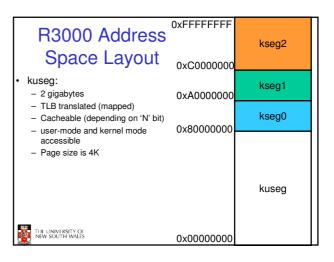

| R3000 Address OxFFFFFFF<br>Space Layout OxC000000                      |                 |            | kseg2           |

|------------------------------------------------------------------------|-----------------|------------|-----------------|

| <ul> <li>Switching processes<br/>switches the translation 0</li> </ul> |                 | 0xA0000000 | kseg1           |

| (page table) for kuseg 0x8000000                                       |                 | kseg0      |                 |

| Proc 1<br>kuseg                                                        | Proc 2<br>kuseg | 0×0000000  | Proc 3<br>kuseg |

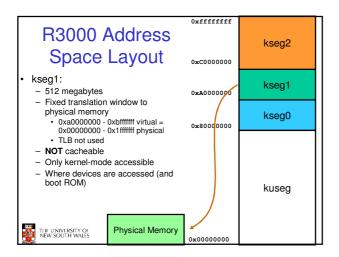

| R3000 Address<br>Space Layout                                                                                     | 0xffffffff<br>0xC0000000 | kseg2 |

|-------------------------------------------------------------------------------------------------------------------|--------------------------|-------|

| <ul> <li>kseg2:</li> <li>– 1024 megabytes</li> </ul>                                                              | 0xA0000000               | kseg1 |

| <ul> <li>TLB translated (mapped)</li> <li>Cacheable</li> <li>Depending on the 'N'-bit</li> </ul>                  | 0x80000000               | kseg0 |

| <ul> <li>Only kernel-mode accessible</li> <li>Can be used to store the virtual linear array page table</li> </ul> |                          | kuseg |

|                                                                                                                   | 0x00000000               |       |