- Interrupt disabling?

- · Syscalls?

- Processor Instructions?

THE UNIVERSITY OF NEW SOUTH WALES

The problem

add: lw r0, (r1) add r0, r0, 1 sw r0, (r1)

## THE UNIVERSITY OF NEW SOUTH WALLS

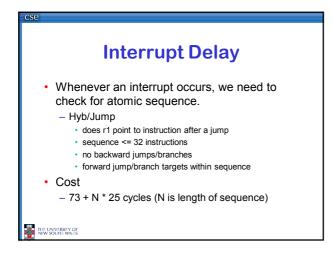

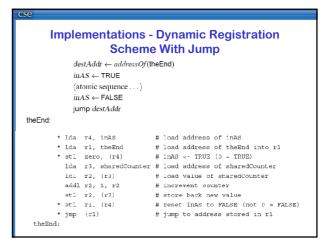

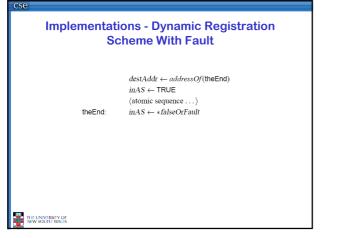

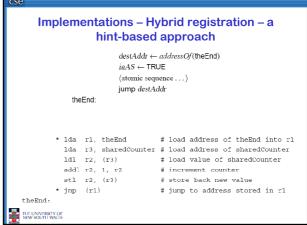

Controlled fault Computed Jump - Dummy instruction at end of each - Every sequence uses a computed jump at sequences the end NOP for normal case · Normal sequence simply jmp to next instruction Fault for interrupt case · Interrupted sequence jumps to interrupt handler - Example is read from (in)accessible page · Adds a jump to every sequence - Only good for user-kernel privilege changes - Still adds an extra instruction THE UNIVERSITY OF NEW SOLITH WALLS THE UNIVERSITY OF NEW SOUTH WALES

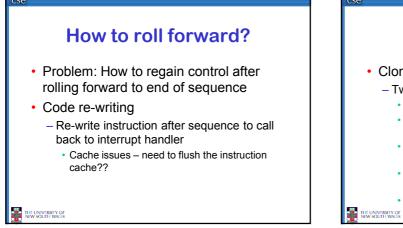

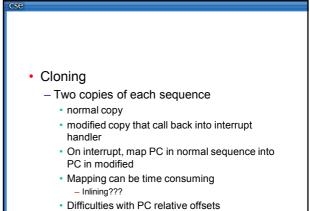

## Limiting Duration of Roll forward

Watchdog

THE UNIVERSITY OF NEW SOUTH WALES

|   | Results     |           |            |            |                |      |      |

|---|-------------|-----------|------------|------------|----------------|------|------|

| [ |             | DEC Alpha |            |            | HP PA-RISC 1.1 |      |      |

|   | Technique   | NULL      | LIFO       | FIFO       | NULL           | LIFO | FIFO |

| [ | sigprocmask | 1682      | 3045       | 3363       | 1787           | 3578 | 3590 |

|   | Dyn/Fault   | 13        | 27         | 24         | 12             | 24   | 27   |

|   | Dyn/Jump    | 9         | 16         | 13         | 11             | 21   | 27   |

|   | Hyb/Jump    | 6         | 5          | 6          | 5              | 8    | 12   |

|   | DI          | 4         | 3          | 4          | 4              | 5    | 12   |

|   | CIPL        | 4         | 5          | 6          | 14             | 24   | 29   |

|   | splx        | 44        | 89         | 88         | 30             | 63   | 73   |

|   | PALcode     | $\geq 13$ | $\geq 13$  | $\geq 13$  | n/a            | n/a  | n/a  |

|   | LL/STC      | n/a       | $\geq 118$ | $\geq 118$ | n/a            | n/a  | n/a  |

- CIPL set interrupt priority level

- SPLx same as CIPL with function call

- PALcode special Alpha processor call

- LL/SC load link store conditional