# Page Tables Revisited \*\*THEUNIVERSITY OF THE UNIVERSITY OF THE UN

# **Learning Outcomes**

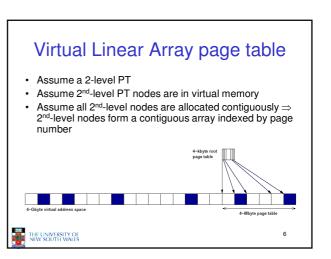

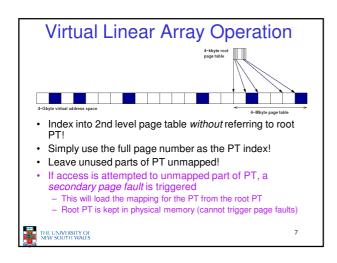

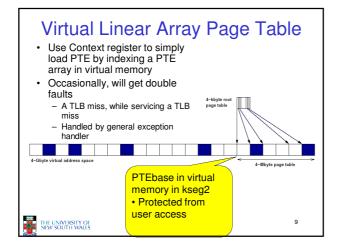

- An understanding of virtual linear array page tables, and their use on the MIPS R3000.

- Exposure to alternative page table structures beyond two-level and inverted page tables.

2

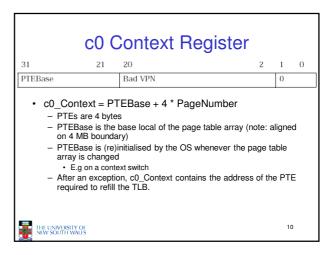

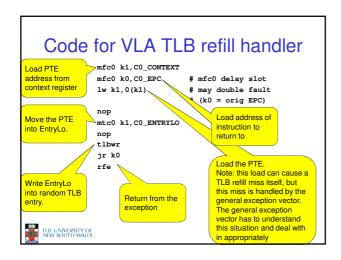

### R3000 TLB Refill Can be optimised for TLB refill An example routine mfc0 k1,C0\_CONTEXT Does not need to check the exception type mfc0 k0,C0\_EPC # mfc0 delay # slot lw k1,0(k1) # may double # fault (k0 = orig EPC) Does not need to save any registers It uses a specialised nop mtc0 k1,C0\_ENTRYLO assembly routine that only uses k0 and k1. Does not check if PTE exists nop Assumes virtual linear array – see extended OS notes tlbwr jr k0 With careful data structure choice, exception handler can be made very fast THE UNIVERSITY OF NEW SOUTH WALES

## **Trends**

- · Operating systems

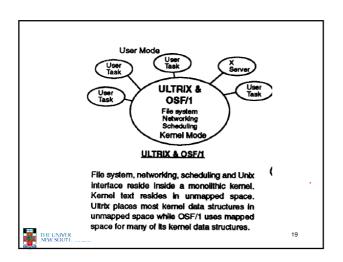

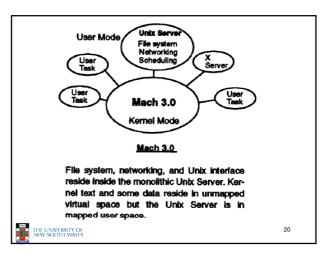

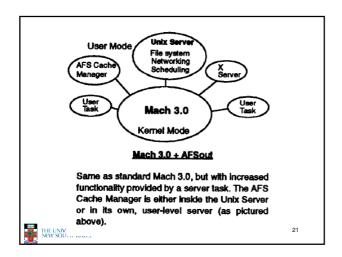

- moving functionality into user processes

- making greater use of virtual memory for mapping data structures held within the kernel.

- · RAM is increasing

- TLB capacity is relatively static

- · Statement:

- Trends place greater stress upon the TLB by increasing miss rates and hence, decreasing overall system performance.

- True/False? How to evaluate?

13

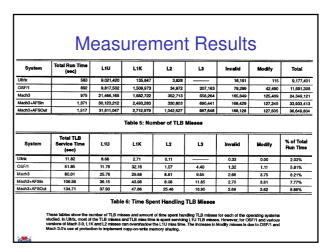

| ILB Miss Type  Ultrix  OSF/1  Mach 3.0  U 16 20 20  20  K 333 355 294  494 511 407  354 286  ddily 375 436 499  rakd 336 277 267  Table 3: Costs for Different TLB Miss Types  Itable shows the number of machine cycles (at 60 ns/cycle) required for different types of TLB misses. To determine these costs. Morst used to collect a 128K-entry histogram of timings for each type of misseparate TLB miss types into the six categories described below. Not Ultrix does not have L3 misses because it implements a 2-level page.  TLB miss on a level 1 were PTE.  TLB miss on a level 1 were PTE.  TLB miss on a level 1 were PTE.  TLB miss on a level 1 were level.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 komel miss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K 333 355 294  494 511 407  — 354 286  cdity 375 436 499  alad 336 277 267  Table 3: Costs for Different TLB Miss Types  table shows the number of mechanic cycles (at 60 na/cycle) required fice different types of TLB misses. To determine these costs, Morest separate TLB miss types into the six categories described below. No Ultric does not have L3 misses because it implements a 2-level pag.  TLB miss on a level 1 user PTE.  TLB miss on a level 1 year PTE.  TLB miss on a level 2 PTE. This can only occur after miss on a level 1 user PTE.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 spTE. Can occur after either level 2 miss or a level 1 series on sevel 2 pTE. The miss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 494 511 407                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Table 3: Costs for Different TLB Miss Types  table 3: Costs for Different TLB Miss Types  table 3: Costs for Different TLB Miss Types  table shows the number of machine cycles (at 60 ns/cycle) required for different types of TLB misses. To determine these costs, Morst used to collect a 128K-ently histogram of timings for each type of misseparate TLB miss types into the six categories described below. Not Ultrik does not have 1.3 misses because it Implements a 2-level pag. b.  TLB miss on a level 1 user PTE.  TLB miss on level 2 PTE. This can only occur after miss on a level 1 user PTE.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 strend miss.  Ifly A page protection violation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Addity 375 436 499  Add 336 277 267  Table 3: Costs for Different TLB Miss Types  Itable shows the number of mechine cycles (at 60 net/cycle) required (cs. different types of TLB missas. To determine these costs, Monet used to collect a 128K-ently beforgare of timely expensed to 128K-ently before the security page.  TLB miss on a level 1 user PTE.  TLB miss on a level 2 PTE. This can only occur after miss on a level 1 user PTE.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 twent miss.  If y A page protection violation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 3: Costs for Different TLB Miss Types  I table shows the number of machine cycles (at 60 ns/cycle) required (so different types of TLB misses. To determine these costs, Morst used to colled a 128/c-enty histogram of timings for each type of ris separate TLB miss types into the six categories described below. Not Ultrik does not have 13 misses because it implements a 2-level pag.  TLB miss on a level 1 user PTE.  TLB miss on a level 1 TLB. This can only occur after miss on a level 1 user PTE.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 sPTE. Can occur after either level 2 miss or a level 1 twent miss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 3: Costs for Different TLB Miss Types  table shows the number of machine cycles (at 60 ns/cycle) required for different types of TLB misses. To determine these costs, Morsts used to collect a 128K-entry histogram of timings for each type of misseparate TLB miss types into the six categories described below. Not Ultrix does not have 13 misses because it Implements a 2-level page.  TLB miss on a level 1 user PTE.  TLB miss on level 2 PTE. This can only occur after miss on a level 1 user PTE.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 page TTE. Can occur after either level 2 miss or a level 1 kmell miss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| table shows the number of mechine cycles (at 60 na/cycle) required for different types of TLB misses. To determine these costs, Morsis determines a 28K-ent type of the second of the se |

| miss on a level 1 user PTE.  TLB miss on a level 3 PTE. Can occur after either level 2 miss or a level 1 kemel miss.  A page protection violation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| level 2 miss or a level 1 kernel miss.  A page protection violation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ., ., ., ., ., ., ., ., ., ., ., ., ., .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ilid An access to an page marked as invalid (page fault).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Note the TLB miss costs

What is expected to be the common case?

3

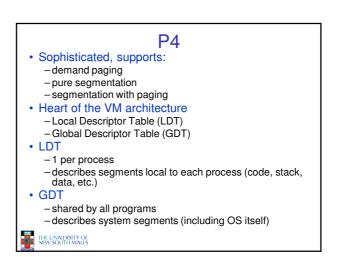

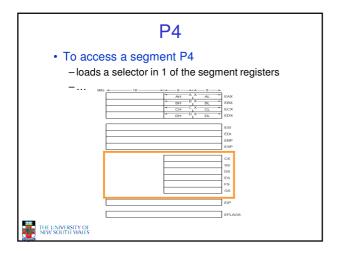

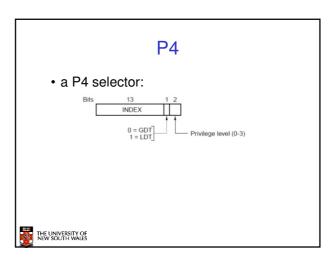

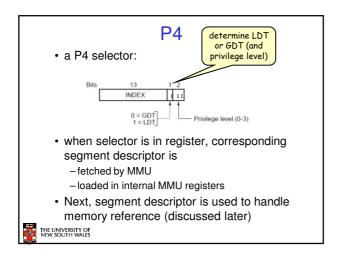

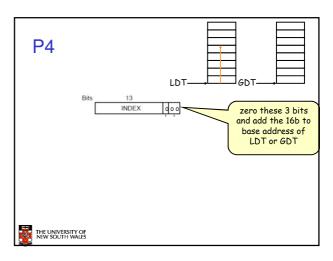

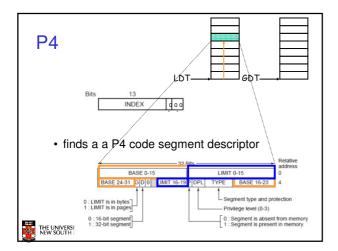

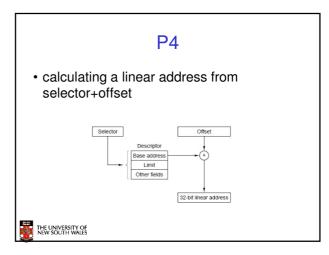

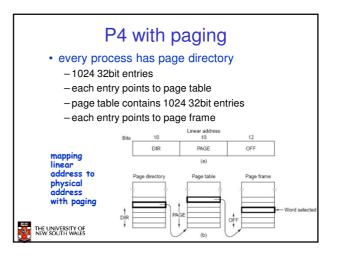

P4

• Many OSs:

-BASE=0

-LIMIT=MAX

• → no segmentation at all