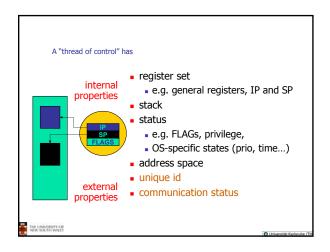

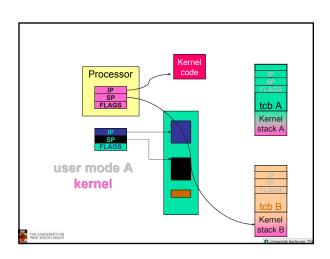

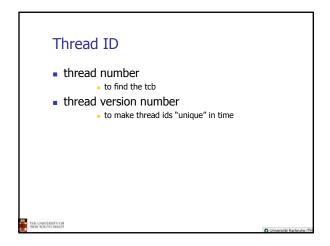

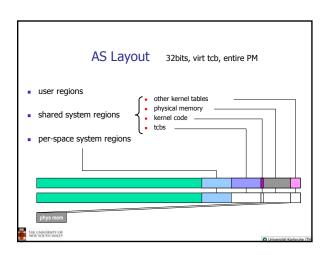

## Fundamental Abstractions A thread is an independent flow of control inside an address space. Threads are identified by unique identifiers and communicate via IPC. Threads are characterized by a set of registers, including at least an instruction pointer, a stack pointer and a state information. A thread's state also includes the address space in which the thread currently executes.

THE UNIVERSITY OF NEW SOUTH WALES

Construction Conclusions (1)

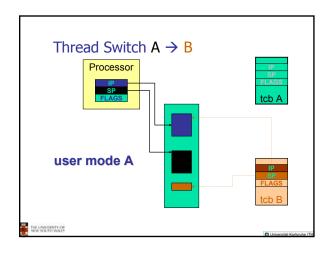

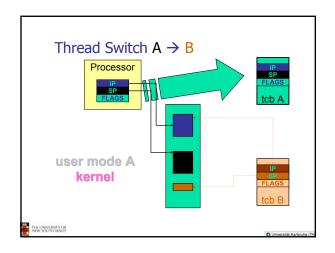

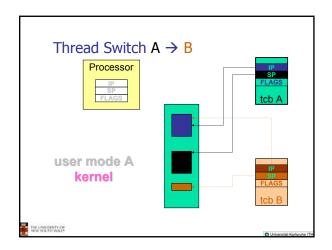

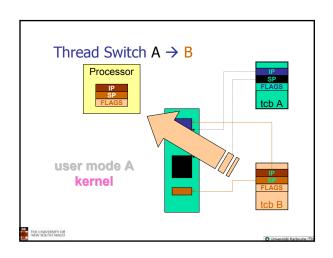

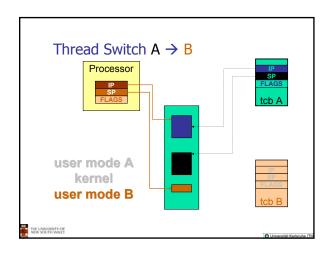

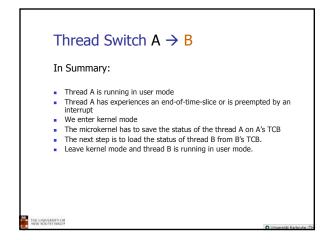

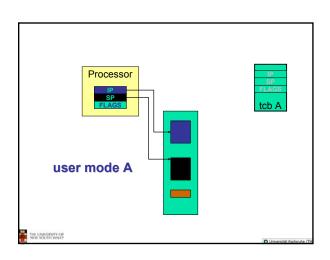

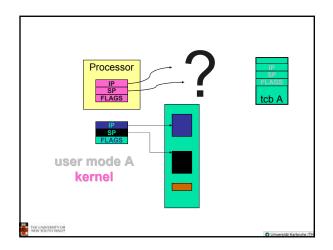

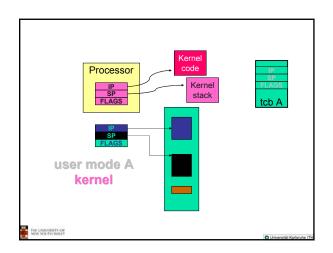

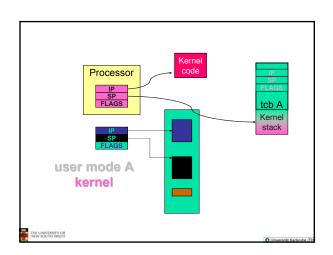

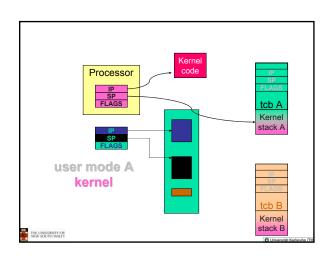

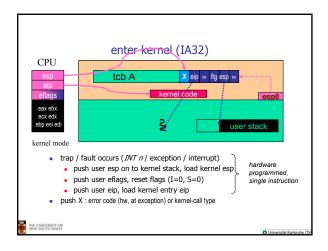

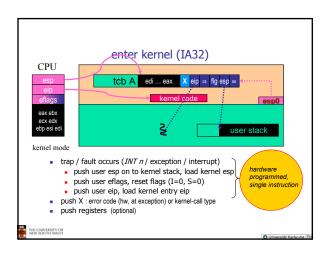

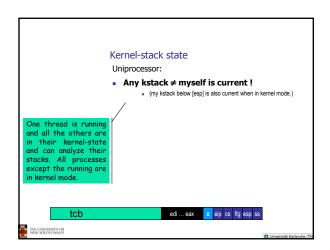

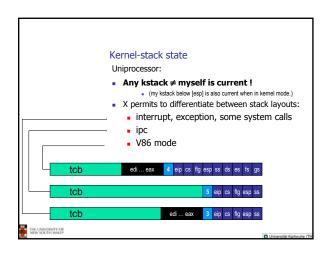

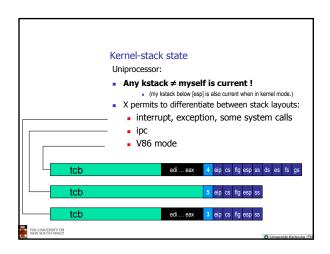

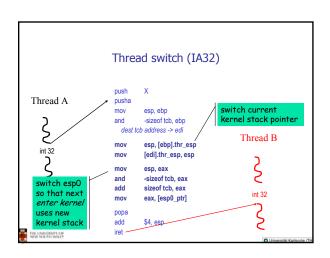

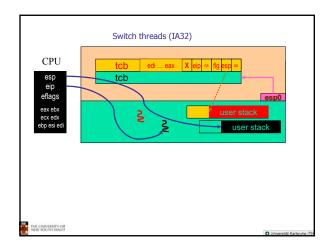

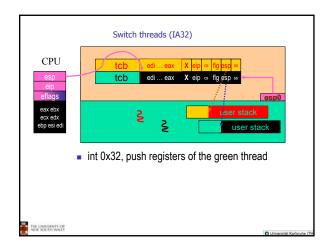

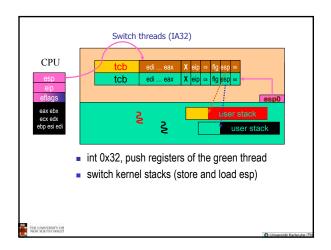

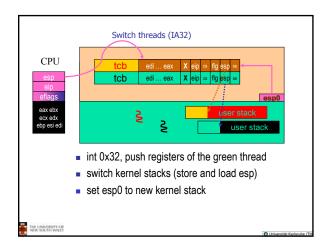

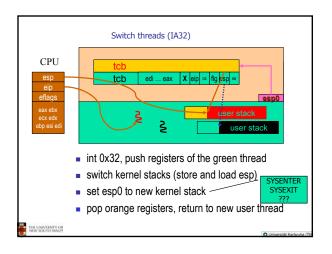

Thread state must be saved / restored on thread switch.

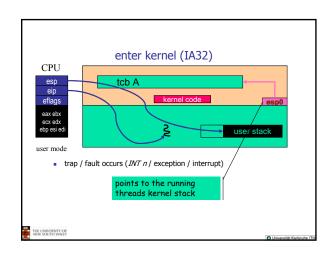

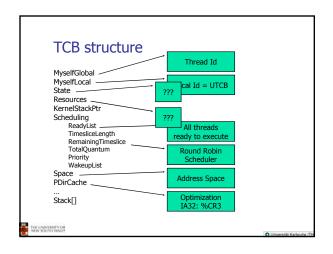

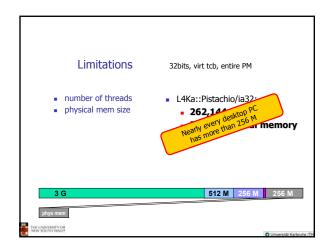

We need a thread control block (tcb) per thread.

Tcbs must be kernel objects.

Tcbs implement threads.

Tcbs implement threads.

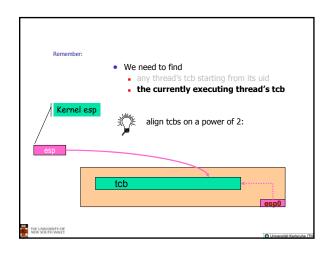

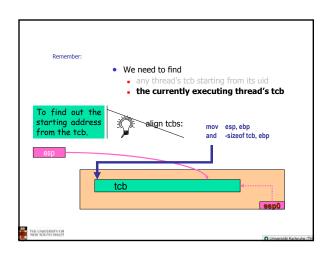

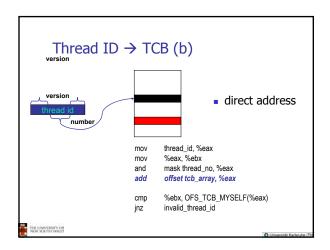

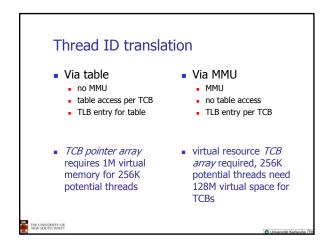

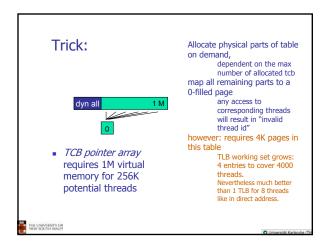

We need to find

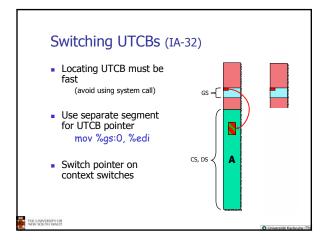

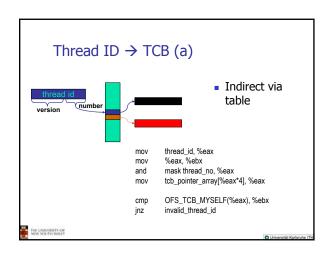

any thread's tcb starting from its uid

the currently executing thread's tcb (per processor)

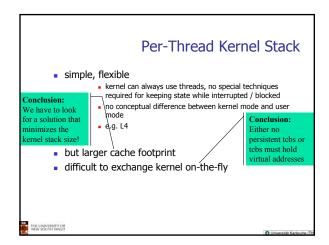

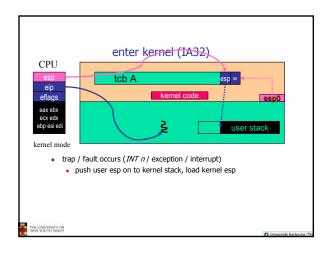

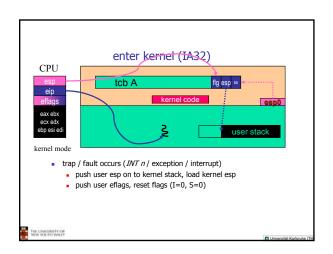

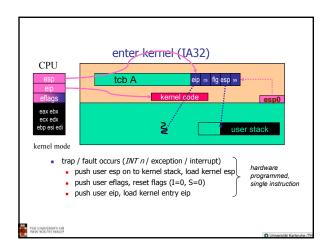

## Per-Thread Kernel Stack Processes Model

- A thread's kernel state is implicitly encoded in the kernel activation stack

- If the thread must block inkernel, we can simply switch from the current stack, to another threads stack until thread is resumed

- Resuming is simply switching back to the original stack

- Preemption is easy

- no conceptual difference between kernel mode and user mode

- example(arg1, arg2) {

Pl(arg1, arg2);

if (need\_to\_block) {

thread\_block();

P2(arg2);

} else {

P3();

}

/\* return control to user \*/

return SUCCESS;

}

Olim

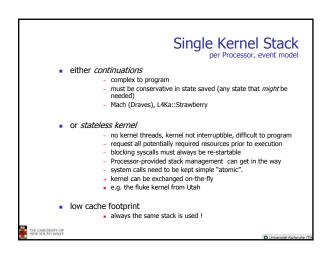

## Single Kernel Stack "Event" or "Interrupt" Model

- How does use a single kernel stack to support many threads?

- Issue: How are system calls that block handled?

- ⇒ either *continuations*

- Draves et al. Using Continuations to Implement Thread Management and Communication in Operating Systems. Proc. 13th SOSP

- ⇒ or stateless kernel (interrupt model)

- Ford et al. Interface and Execution Models in the Fluke Kernel. Proc 3rd OSDI

THE UNIVERSITY OF

C Universität Karlsouhe

### Continuations

- State required to resume a blocked thread is explicitly saved in a TCB

State required to resume a example (arg1, arg2);

p1(arg1, arg2);

if (need\_to\_block)

- A function pointerVariables

- Stack can be discarded and reused to support new thread

```

Pl(arg1, arg2);

if (need_to_block) {

save_context_in_TCB;

thread_block(example_continue);

/* NOT REACHED */

} else {

P3();

}

```

thread\_syscall\_return(SUCCESS);

}

example\_continue() {

recover\_context\_from\_TCB;

P2(recovered arg2);

thread\_syscall\_return(SUCCESS);

THE UNIVERSITY OF NEW SOUTH WALES

THE UNIVERSITY OF NEW SOUTH WALES

niversität Karlsovhe (TH

### Stateless Kernel

- System calls can not block within the kernel

- If syscall must block (resource unavailable)

- Modify user-state such that syscall is restarted when resources become available

- Stack content is discarded

- Preemption within kernel difficult to achieve.

- ⇒ Must (partially) roll syscall back to (a) restart point

- Avoid page faults within kernel code

- ⇒ Syscall arguments in registers

- Page fault during roll-back to restart (due to a page fault) is fatal.

THE UNIVERSITY OF NEW SOUTH WALES

O Universität Karlsruh

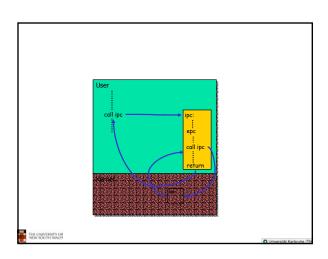

## IPC examples – Per thread stack

```

msg_send_rcv(msg, option,

send_size, rcv_size, ...) {

rc = msg_send(msg, option,

send_size, ...);

if (rc != SUCCESS)

return rc;

rc = msg_rcv(msg, option, rcv_size, ...);

Block inside msg_rcv if

no message available

```

### **IPC** examples - Continuations

```

IPC Examples — stateless kernel

msg_send_rcv(cur_thread) {

rc = msg_send(cur_thread);

if (rc != SUCCESS)

return rc;

set_pc(cur_thread, msg_rcv_entry);

rc = msg_rcv(cur_thread)

if (rc != SUCCESS)

return rc;

return rc;

return success;

}

Set user-level PC

to restart msg_rcv

only

```

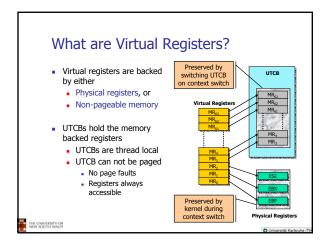

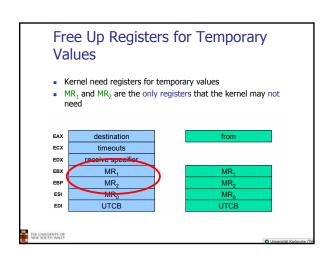

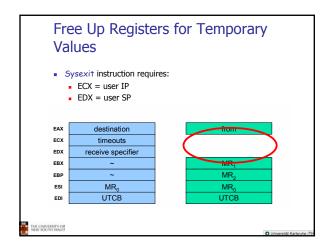

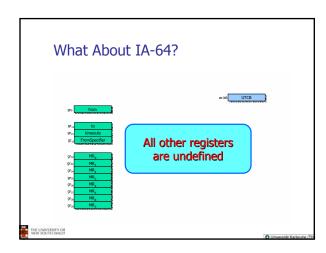

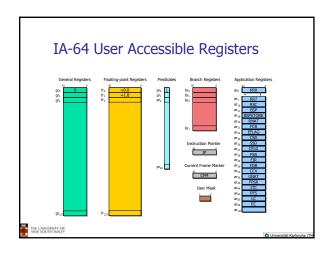

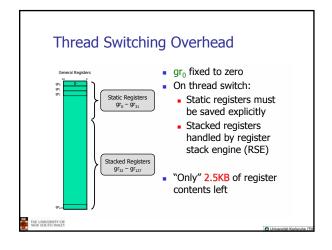

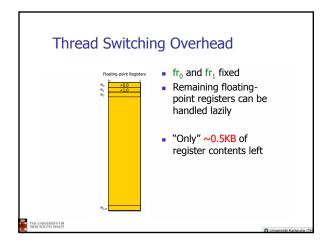

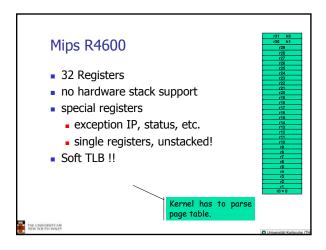

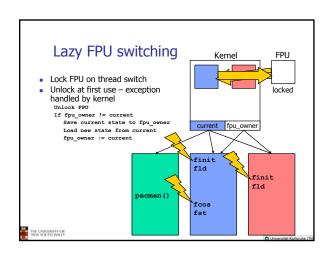

# Thread Switching Overhead All registers must be saved on context switches More than 3.2KB of register contents Certain optimizations made possible by hardware

FPU Context Switching

Strict switching

Thread switch:

Store current thread's FPU state

Load new thread's FPU state

Load new thread's FPU state

Extremely expensive

IA-32's full SSE2 state is 512 Bytes

IA-64's floating point state is ~1.5KB

May not even be required

Threads do not always use FPU

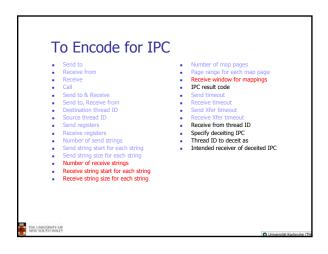

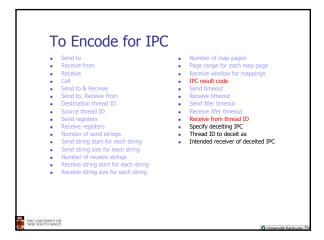

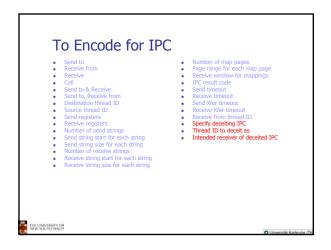

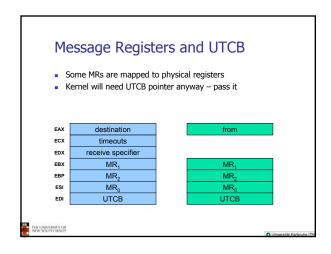

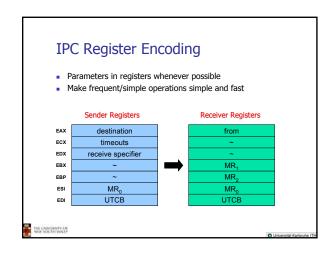

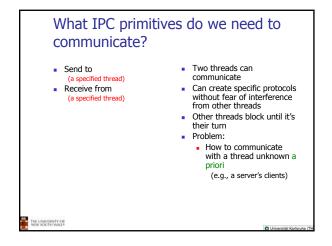

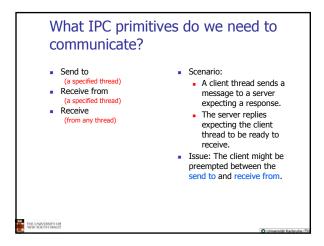

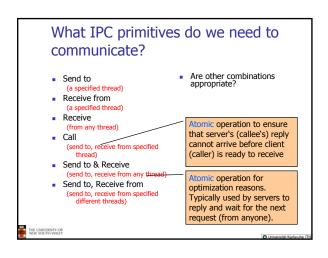

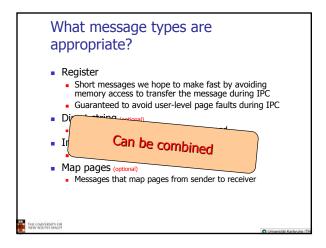

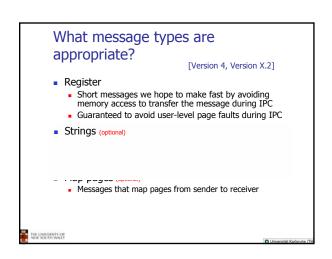

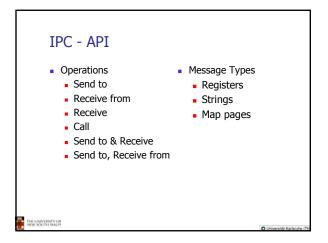

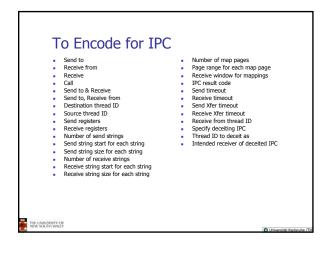

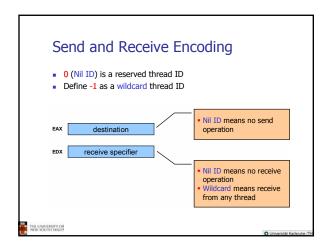

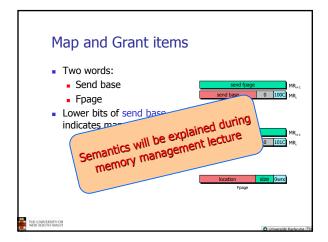

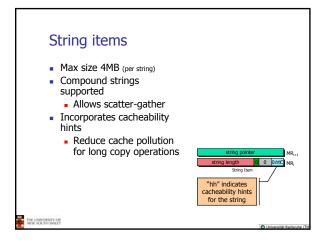

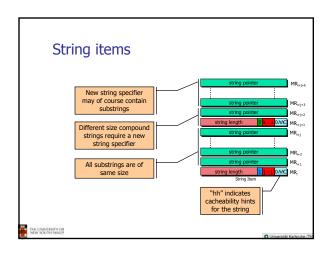

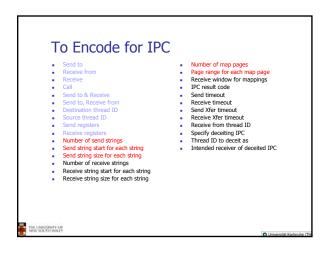

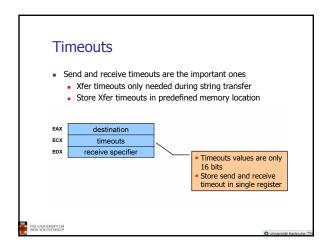

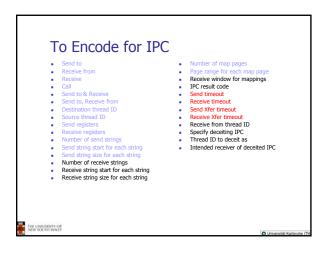

# To Encode for IPC Send to Receive from Receive Call Send to & Receive Send to & Receive Send to Receive from Destination thread ID Source thread ID Send registers Receive registers Receive registers Send string start for each string Send string start for each string Receive string start for each string

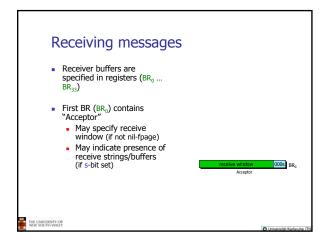

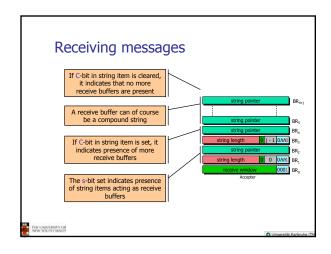

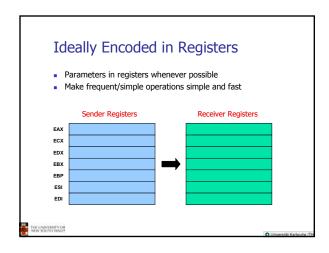

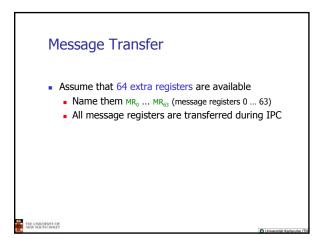

# String Receival Assume that 34 extra registers are available Name them BR<sub>0</sub> ... BR<sub>33</sub> (buffer registers 0 ... 33) Buffer registers specify Receive strings Receive window for mappings