# Reconfiguration Control Networks for FPGA-based Space Applications

Zhuoran Zhao

A thesis in fulfillment of the requirements for the degree of

Masters by Research

School of Computer Science and Engineering

Faculty of Engineering

The University of New South Wales

November 2016

#### THE UNIVERSITY OF NEW SOUTH WALES Thesis/Dissertation Sheet

Surname or Family name: Zhao

First name: **Zhuoran** Other name/s:

Abreviation for degree as given in the University calendar: Masters by Research

School: School of Computer Science and Engineering

Faculty: Faculty of Engineering

Title: Reconfiguration Control Networks for FPGA-based Space Applications

Abstract

Space processing applications deployed on SRAM-based Field Programmable Gate Arrays (FPGAs) are vulnerable to radiationinduced Single Event Upsets (SEUs). To efficiently mitigate configuration memory upsets, Triple Modular Redundancy (TMR) with Module-based Error Recovery (MER) has been proposed. TMR-MER systems rely on a Reconfiguration Control Network (RCN) to aggregate reconfiguration requests from voters that are distributed across the device to a central Reconfiguration Controller (RC), which performs partial reconfiguration on an affected module. This thesis focuses on the choice and impact of these RCNs on the system's reliability and performance.

This thesis evaluates the suitability, utilization and performance of a token ring network in fulfilling the requirements of an RCN as the number of network connections is increased. As RCNs are not limited to a ring, we then carry out a comprehensive study and comparison of four possible RCN topologies, namely, a star, a bus, a token ring and an ICAP-based readback approach, with respect to their utilization, latency and SEU sensitivity as the network capacity increases. We evaluate these networks by implementing them on synthetic layouts as well as an experimental payload based on a Xilinx Artix-7 device and by injecting faults into these implementations. We show that of the RCN topologies studied, the ICAP-based approach is the most reliable, despite having the highest latency, while the star network also proves to be a strong contender due to its high performance.

In our study, we found the reliability of TMR-MER to be significantly less than that of TMR-S unless the RCN was also triplicated and recovered. To more effectively localize errors in RCNs or other triplicated sub-components, this thesis proposes a fine-grained module error recovery scheme that without additional system hardware can localize and correct errors that classic MER fails to identify. We evaluate our proposal via a fault-injection campaign on a Xilinx Artix-7 application circuit and compare the reliability, the recovery latency and the energy cost of repairing errors, of our proposed method with those of a conventional MER approach and with periodic and on-demand blind scrubbing. We find the reliability of our proposal to be the highest and the energy expenditure to be the lowest amongst those methods considered.

The thesis concludes with directions for further study.

#### Declaration relating to disposition of project thesis/dissertation

I hereby grant to the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or in part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all property rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstracts International (this is applicable to doctoral theses only).

#### Signature **Zhuoran Zhao**

Witness Oliver Diessel

Date Nov. 16, 2016

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years must be made in writing. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

FOR OFFICE USE ONLY

Date of completion of requirements for Award

#### **Originality Statement**

I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.

**Zhuoran Zhao** Nov. 30, 2016

#### **Copyright Statement**

I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only).

I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation.

**Zhuoran Zhao** Nov. 30, 2016

#### Authenticity Statement

I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.

**Zhuoran Zhao** Nov. 30, 2016

## Abstract

Space processing applications deployed on SRAM-based Field Programmable Gate Arrays (FPGAs) are vulnerable to radiation-induced Single Event Upsets (SEUs). To efficiently mitigate configuration memory upsets, Triple Modular Redundancy (TMR) with Module-based Error Recovery (MER) has been proposed. TMR-MER systems rely on a Reconfiguration Control Network (RCN) to aggregate reconfiguration requests from voters that are distributed across the device to a central Reconfiguration Controller (RC), which performs partial reconfiguration on an affected module. This thesis focuses on the choice and impact of these RCNs on the system's reliability and performance.

This thesis evaluates the suitability, utilization and performance of a token ring network in fulfilling the requirements of an RCN as the number of network connections is increased. As RCNs are not limited to a ring, we then carry out a comprehensive study and comparison of four possible RCN topologies, namely, a star, a bus, a token ring and an ICAP-based readback approach, with respect to their utilization, latency and SEU sensitivity as the network capacity increases. We evaluate these networks by implementing them on synthetic layouts as well as an experimental payload based on a Xilinx Artix-7 device and by injecting faults into these implementations. We show that of the RCN topologies studied, the ICAP-based approach is the most reliable, despite having the highest latency, while the star network also proves to be a strong contender due to its high performance.

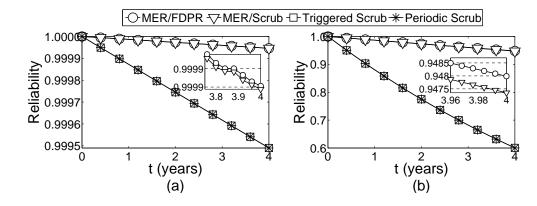

In our study, we found the reliability of TMR-MER to be significantly less than that of TMR-S unless the RCN was also triplicated and recovered. To more effectively localize errors in RCNs or other triplicated sub-components, this thesis proposes a fine-grained module error recovery scheme that without additional system hardware can localize and correct errors that classic MER fails to identify. We evaluate our proposal via a fault-injection campaign on a Xilinx Artix-7 application circuit and compare the reliability, the recovery latency and the energy cost of repairing errors, of our proposed method with those of a conventional MER approach and with periodic and on-demand blind scrubbing. We find the reliability of our proposal to be the highest and the energy expenditure to be the lowest amongst those methods considered.

The thesis concludes with directions for further study.

## Acknowledgements

First of all, I would like to thank my supervisor, Assoc. Prof. Oliver Diessel, for continuously pushing me towards finishing this work. Thank you for your patience and timely feedback, as well as your effort in correcting my language errors and intellectualizing my direction whenever I lost my way.

I would also thank his colleague, Dr Ediz Cetin, who helps me on discussing my research, reviewing my papers, and most importantly, cheering me up when I was defeated by life. I would like to thank my co-supervisor, Dr Guo Hui, who was always willing to listen to my complaints. I thank all of my fellows in the Reconfigurable System Group for their help throughout my study.

Lastly, special thanks to my parents who support and understand all of my self-willed decisions, and kindly listen to my whispers about the hardship of life and work.

# Abbreviations

- ASIC Application-Specific Integrated Circuit

- **BAQ** Block Adaptive Quantizer

- **BST** Binary Search Tree

- **CLB** Configurable Logic Block

- COTS Commercial, Off-The-Shelf

- **CRC** Cyclic Redundancy Check

- **DICE** Dual Interlocked storage Cell

- **DMA** Direct Memory Access

- **DPR** Dynamic Partial Reconfiguration

- $\mathbf{DUT}$  Design-Under-Test

- $\mathbf{ECC}\xspace$  Error Correcting Code

- ${\bf FDPR}\,$  Fine-grained Dynamic Partial Reconfiguration

**FF** Flip-Flop

- **FIR** Finite Impulse Response

- FPGA Field Programmable Gate Array

- **FSM** Finite State Machine

- GEO Geostationary Earth Orbit

- **ICAP** Internal Configuration Access Port

- **IP** Intellectual Property

- **ITAR** International Traffic in Arms Regulations

- ${\bf LEO}\,$  Low Earth Orbit

- ${\bf LUT}$  Look-Up-Table

- MTTR Mean Time To Recovery

- $\mathbf{NC}$  Network Controller

- ${\bf NI}\,$  Network Interface

- **NRE** None-Recurring Engineering

- **PIP** Programmable Interconnection Point

- $\mathbf{RC}$  Reconfiguration Controller

- **RCN** Reconfiguration Control Network

- Rdone Reconfiguration done

- **RReq** Reconfiguration Request

- **RRhdr** Reconfiguration Request header

- **RUSH** Rapid recovery from SEUs in Reconfigurable Hardware

- ${\bf SD}\,$  Standard Deviation

- SEL Single Event Latchup

- ${\bf SET}$  Single Event Transient

- **SEU** Single Event Upset

- **SEM** Soft Error Mitigation

- SerDes Serializer/Deserializer

- **SM** Switch Matrix

- SoC System-on-Chip

- SOI Silicon-On-Insulator

- SR Shift Register

- **TID** Total Ionizing Dose

- **TMR** Triple Modular Redundancy

- **TMR-MER** Triple Modular Redundancy with Module-based configuration memory Error Recovery

- TMR-S Triple Modular Redundancy with configuration memory error Scrubbing

- **VLSI** Very Large Scale Integration

# Contents

| 1 | Intr | oduction                                | 1 |

|---|------|-----------------------------------------|---|

|   | 1.1  | Contributions                           | 2 |

|   | 1.2  | Publications                            | 3 |

|   | 1.3  | Thesis Outline                          | 4 |

| 2 | Bac  | kground                                 | 6 |

|   | 2.1  | Why FPGAs in Space                      | 6 |

|   | 2.2  | Challenges for Deploying FPGAs in Space | 7 |

|   |      | 2.2.1 Radiation Effects                 | 7 |

|   |      | 2.2.2 Radiation-hardening               | 8 |

|   |      | 2.2.3 Upsets in SRAM-based FPGA         | 1 |

|   | 2.3  | Mitigating Upsets on SRAM-based FPGAs 1 | 3 |

|   |      | 2.3.1 Triple Modular Redundancy         | 3 |

|   |      | 2.3.2 Dynamic Partial Reconfiguration   | 4 |

|   |      | 2.3.3 Configuration Memory Scrubbing    | 4 |

|   |      | 2.3.4 Module-based Error Recovery       | 5 |

|   | 2.4  | Discussion                              | 0 |

| 3 | Tok | en Rir | ng Network                            | <b>21</b> |

|---|-----|--------|---------------------------------------|-----------|

|   | 3.1 | Token  | Ring Network Review                   | 21        |

|   | 3.2 | Revise | ed Token Ring Network Design          | 22        |

|   |     | 3.2.1  | The Implementation                    | 24        |

|   |     | 3.2.2  | Experimental Analysis                 | 25        |

|   | 3.3 | Simpli | ified Token Ring Network Design       | 28        |

|   |     | 3.3.1  | Network Interfaces Architecture       | 29        |

|   |     | 3.3.2  | Experimental Evaluation               | 29        |

|   | 3.4 | Discus | ssion                                 | 31        |

| 4 | Rec | onfigu | ration Control Network                | 32        |

| т |     | 0      | Survey                                |           |

|   | 4.1 |        | u u u u u u u u u u u u u u u u u u u |           |

|   | 4.2 | Optim  | nized RCNs for Comparison             | 35        |

|   |     | 4.2.1  | Star Network                          | 36        |

|   |     | 4.2.2  | Bus                                   | 37        |

|   |     | 4.2.3  | Token Ring Network                    | 37        |

|   |     | 4.2.4  | ICAP-based Voter Checking             | 38        |

|   |     | 4.2.5  | RCN latency                           | 39        |

|   |     | 4.2.6  | Synchronization Support               | 40        |

|   | 4.3 | Exper  | imental Evaluation                    | 40        |

|   |     | 4.3.1  | Synthetic Experiment                  | 41        |

|   |     | 4.3.2  | RUSH Experiment                       | 42        |

|   |     | 4.3.3  | Fault Injection Methodology           | 42        |

|   | 4.4 | Result | зв                                    | 45        |

|   |     | 4.4.1  | Implementation Results                | 45        |

|   |     | 4.4.2  | Fault Injection Results               | 46        |

|   | 4.5  | Discus  | sion                                           | 47 |

|---|------|---------|------------------------------------------------|----|

| 5 | Fine | e-grain | ed Module-based Error Detection and Correction | 48 |

|   | 5.1  | Fine-g  | rained Error Detection Strategy                | 49 |

|   |      | 5.1.1   | Fully-triplicated Circuit Model                | 49 |

|   |      | 5.1.2   | Persistent Errors                              | 51 |

|   |      | 5.1.3   | Repair Strategy                                | 52 |

|   |      | 5.1.4   | Triggered Scrub                                | 54 |

|   |      | 5.1.5   | MER with Scrubbing (MER/Scrub)                 | 55 |

|   | 5.2  | Fine-g  | rained Dynamic Reconfiguration                 | 55 |

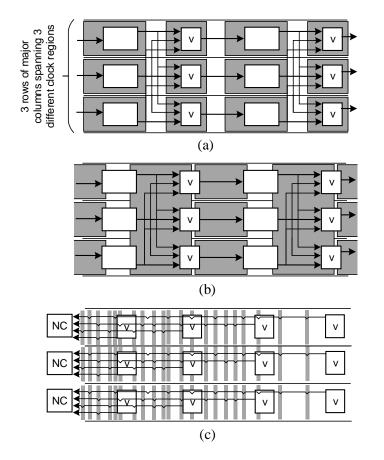

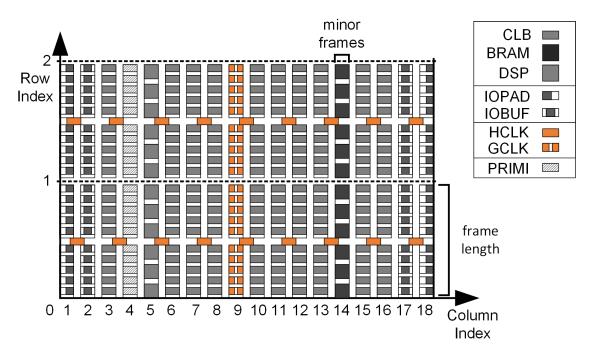

|   |      | 5.2.1   | Major Columns                                  | 56 |

|   |      | 5.2.2   | Configuration Memory Boundaries                | 56 |

|   |      | 5.2.3   | Floorplanning                                  | 57 |

|   |      | 5.2.4   | Dynamic Repair Bitstream Composition           | 58 |

|   | 5.3  | Exper   | imental Evaluation                             | 59 |

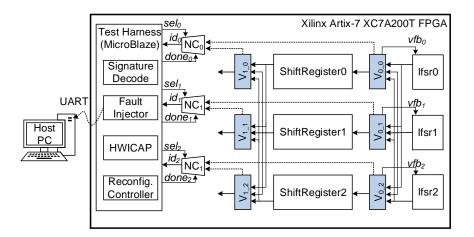

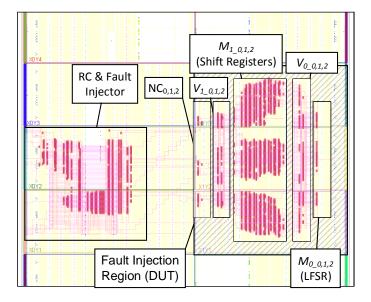

|   |      | 5.3.1   | Experimental Setup                             | 59 |

|   |      | 5.3.2   | Results                                        | 62 |

|   |      | 5.3.3   | Frames, MTTR & Energy                          | 65 |

|   |      | 5.3.4   | Reliability                                    | 65 |

|   | 5.4  | Discus  | sion                                           | 67 |

| 6 | Con  | clusio  | n                                              | 68 |

|   | 6.1  | Conclu  | lding Remarks                                  | 68 |

|   | 6.2  | Future  | e Work                                         | 70 |

| Appen  | dix A                                         | 73 |

|--------|-----------------------------------------------|----|

| A.1    | 7-Series Device Model                         | 73 |

| A.2    | Frame Addressing                              | 74 |

| A.3    | Frame Address Conversion                      | 74 |

| A.4    | Special Major Column Frames                   | 75 |

| A.5    | Artix-7 XC7A200T Device Parameters            | 75 |

| Appen  | dix B                                         | 77 |

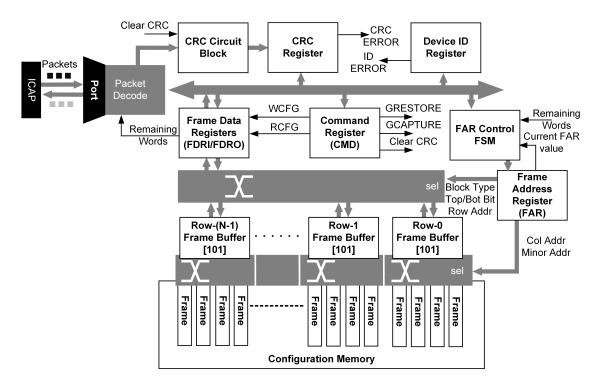

| B.1    | Overview of Internal Configuration Facilities | 77 |

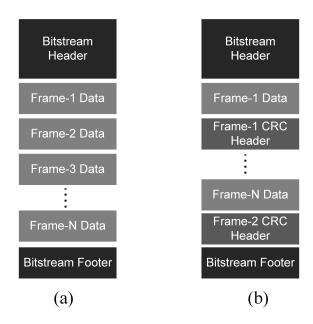

| B.2    | Full Bitstream Composition                    | 78 |

| B.3    | Advanced Dynamic Reconfiguration Operations   | 79 |

|        | B.3.1 Single Frame Write/Read                 | 80 |

|        | B.3.2 Serial Frame Write/Read                 | 81 |

| Refere | nces                                          | 82 |

# List of Figures

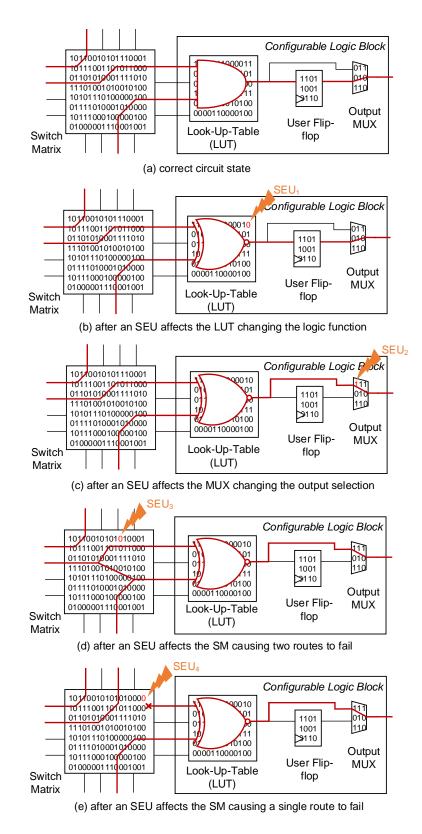

| 2.1 | An example of SEU effects on different types of logic cells [45–47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

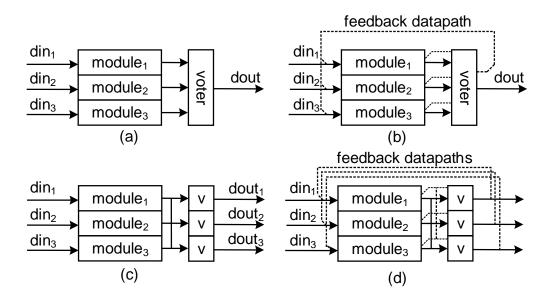

| 2.2 | Triple Modular Redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13 |

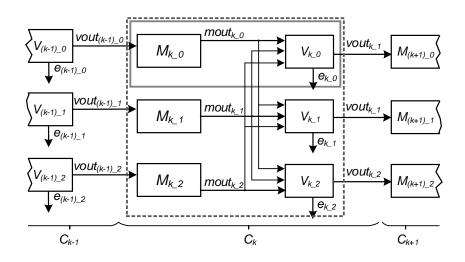

| 2.3 | TMR-MER Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18 |

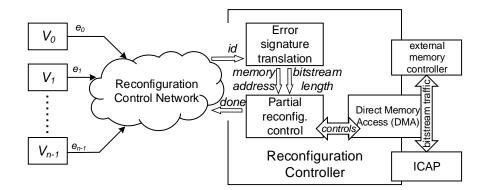

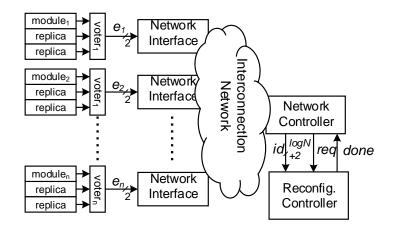

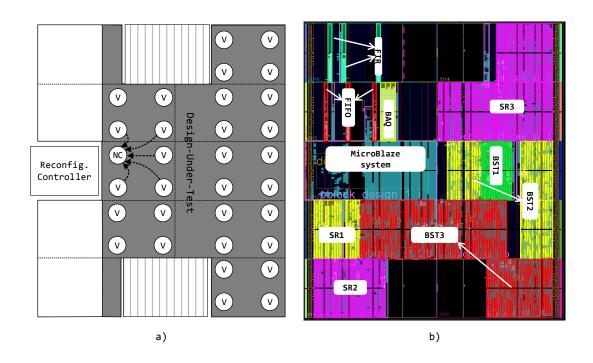

| 2.4 | Reconfiguration Control Network (RCN) & Reconfiguration Controller (RC) for TMR-MER Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

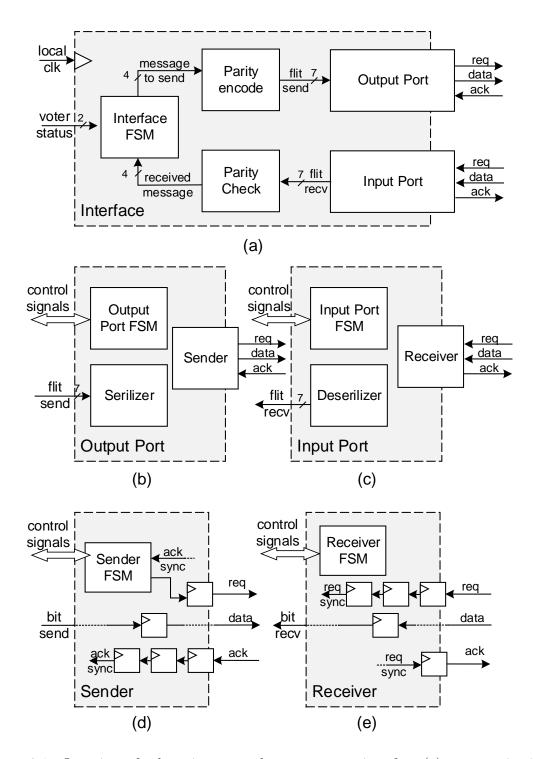

| 3.1 | Overview of token ring network components: interface (a), communication ports (b) (c), and transceivers (d) (e) [13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 |

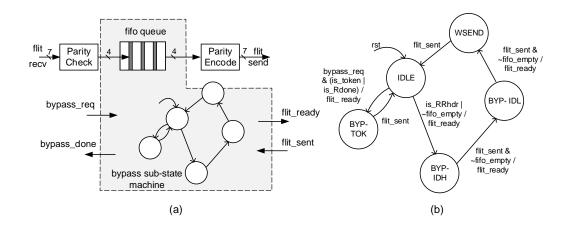

| 3.2 | Bypass sub-state machine design: (a) block overview; (b) sub-state machine design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24 |

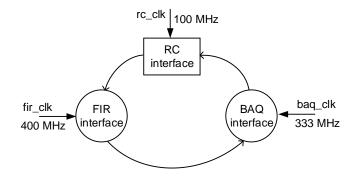

| 3.3 | System layout [13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

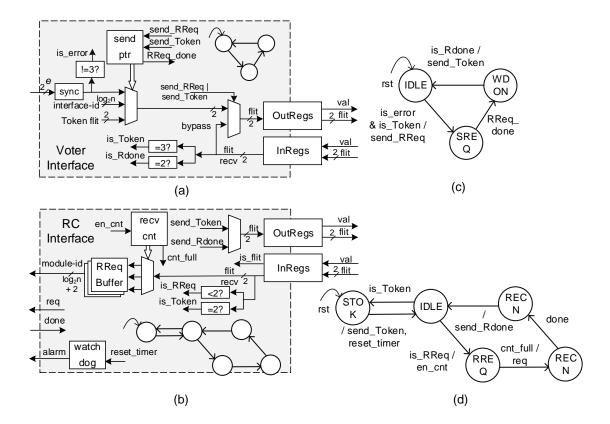

| 3.4 | Architecture of network interface (a) for voters and (b) for the RC, as well as the details of their state machine designs (c) and (d). $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28 |

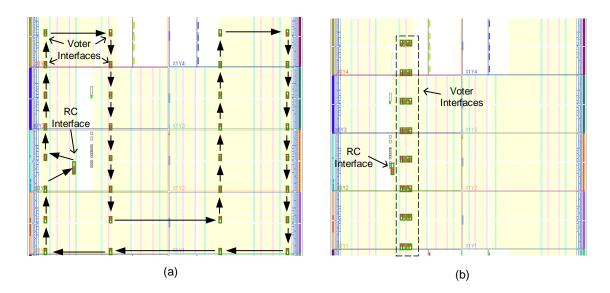

| 3.5 | Experiment 32-node layouts: (a) scattered layout and (b) compact layout $% \left( {\left( {{{\bf{b}}} \right)_{i}} \right)_{i}} \right)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

| 4.1 | Sub-components of an RCN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36 |

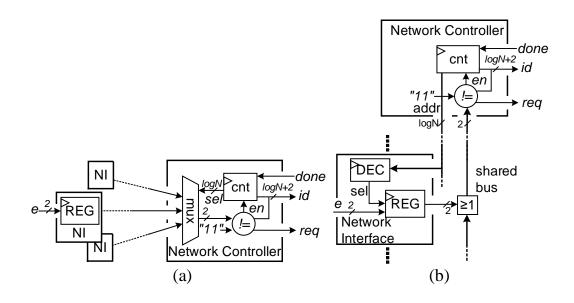

| 4.2 | The architecture of a star network (a) and of a bus (b) $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\h$ | 37 |

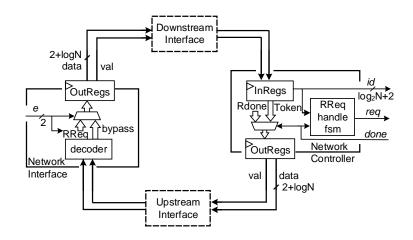

| 4.3 | The architecture of a token ring network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |

| 4.4 | (a) Synthetic layout of a 31-voter design and (b) RUSH floorplan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41 |

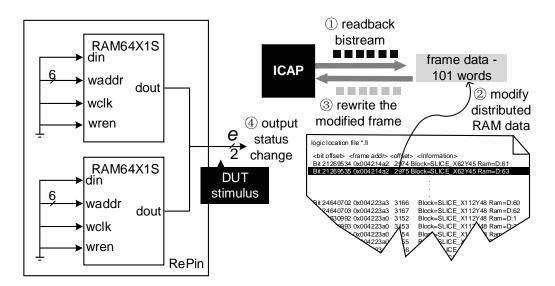

| 4.5 | RePin architecture for input stimulus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

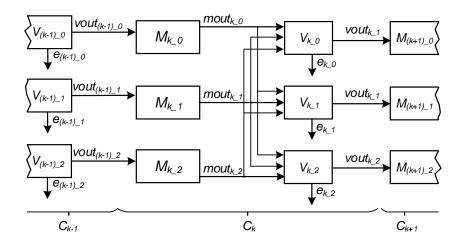

| 5.1 | Target TMR Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50 |

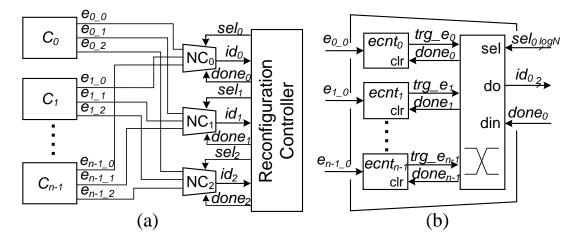

| 5.2 | (a) Triplicated Star-type RCN, (b) Elaborated NC logic                                                          | 50 |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

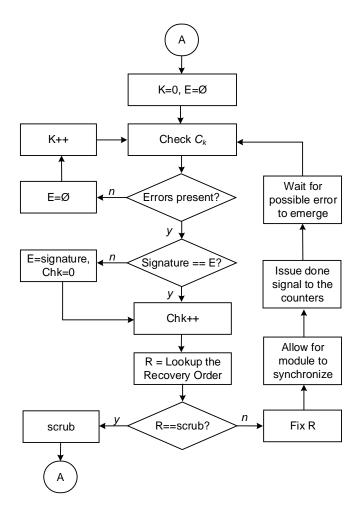

| 5.3 | Repair Flow                                                                                                     | 53 |

| 5.4 | One possible floor<br>planing (a) logic, (b) intra-component nets, (c) RCN                                      | 57 |

| 5.5 | Experimental Setup                                                                                              | 60 |

| 5.6 | Floorplanning of the test harness, and test circuit in three clock regions on the right-hand side of the device | 61 |

| 5.7 | Reliability Results: (a) $\lambda_{bit} = 8.41E - 12$ (LEO), (b) $\lambda_{bit} = 2.66E - 10$ (GEO)             | 66 |

| A.1 | Device Model                                                                                                    | 73 |

| B.1 | Overview of Configuration Facilities                                                                            | 78 |

| B.2 | Composition of bitstream formats: (a) Normal full bitstream (b) Bitstream with single frame CRC check feature   | 79 |

# List of Tables

| 2.1 | Overview of FPGA Parameters & Radiation Immunity                                                                                                              | 10 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Overview of Re-synchronization Approaches                                                                                                                     | 17 |

| 3.1 | Utilization Result                                                                                                                                            | 26 |

| 3.2 | Token Ring Network Performance Comparison                                                                                                                     | 27 |

| 3.3 | Token Ring Network Performance with 8, 16, 32 and 64 Nodes $\ldots$                                                                                           | 27 |

| 3.4 | Utilization Result                                                                                                                                            | 29 |

| 3.5 | Maximum Clock Speed and Routing Utilization Results                                                                                                           | 30 |

| 3.6 | Simplified Token Ring Network Performance Results for 32 Voters $\ . \ . \ .$ .                                                                               | 31 |

| 4.1 | Results of mapping four RCNs to Xilinx Artix-7 XC7A200TFBG-484                                                                                                | 44 |

| 4.2 | Number of critical bits detected from 1 million random fault injections performed in the four types of network with different number of voters over 5 trials. | 46 |

| 4.3 | Comparison between fault injection results and essential bit results                                                                                          | 47 |

| 5.1 | Recovery Sequence                                                                                                                                             | 54 |

| 5.2 | Block Sub-component Area & Recovery Time                                                                                                                      | 62 |

| 5.3 | Net Sub-component Area & Recovery Time                                                                                                                        | 63 |

| 5.4 | Fault Injection Result                                                                                                                                        | 64 |

| 5.5 | Frames, MTTR and Energy Result                                                                                                                                | 65 |

5.6 Sub-component Critical Bits Summary Using Proposed Recovery Sequence 66

### Chapter 1

### Introduction

Digital systems for space have traditionally been implemented using radiation-hardened devices. In recent years, interest has grown in using Commercial, Off-The-Shelf (COTS) SRAM-based Field Programmable Gate Arrays (FPGAs), particularly for low-cost Low Earth Orbit (LEO) applications, to reduce the cost and to enhance the flexibility and performance of these systems. These applications commonly rely on Triple Modular Redundancy (TMR) to mask the effects of radiation-induced Single Event Upsets (SEUs) in the application circuits, in which user data that is stored in flip-flops may become corrupted by ionizing radiation [1]. The configuration memory of these devices, which constitute 90% of the device resources, are also susceptible to radiation-induced corruption. The errors in the configuration memory may result in changes to the circuit state and the implemented circuit itself. Due to the accumulation of errors in the configuration memory, the triplication of the circuit's application may fail when more than two modules of the TMR component fail.

Two approaches have emerged in the literature to deal with this problem. Configuration memory scrubbing (TMR-S) periodically scans the entire device and corrects configuration memory errors by rewriting the memory frames containing them [2]. While scrubbing occurs periodically, whether or not errors are present, substantial time and energy are wasted on overwriting frames that are correct. With the decreasing feature size of CMOS transistors, upsets occur more readily in the configuration memory, but scrub cycles take more time due to the increased device capacity. Module-based error recovery (TMR-MER), on the other hand, reconfigures the frames of a TMR module when an error in its configuration memory is detected. This approach relies upon repeated detection of an error by the same TMR voter to trigger a reconfiguration of the module presenting the error [3].

Both methods are based on Dynamic Partial Reconfiguration (DPR), which facilitates the dynamic reading and writing of the configuration memory without interruptions.

There are a number of TMR-MER systems that have been reported in the literature, e.g. [3–11]. Most of these systems rely upon a dedicated Reconfiguration Control Network (RCN) to relay error requests from the voters in the system to a central Reconfiguration Controller (RC) [12]. The performance and reliability of the RCN are important for a few reasons. Firstly, the latency of the RCN has a direct impact on the Mean Time To Recovery (MTTR) from errors in the system, and the sooner the module is recovered, the lower the likelihood that the protection provided by TMR fails. On the other hand, the RCN is often implemented as a non-redundant component in the system, whereby it introduces a single point of failure that can greatly compromise system reliability. Therefore, in this thesis, we focus our attention on the design of an RCN for high performance and low resource utilization so as to reduce its sensitivity to upsets. We investigate possible network topologies for implementing an RCN and compare their area, performance, and upset vulnerability with a view to establishing the best solution for a given operating environment.

To achieve high system reliability, it is also possible to triplicate the RCN and to detect whether or not an RCN is corrupted due to SEUs. The triplication of the RCN generates a set of error reports which we refer to as an error signature, and as shown in this thesis, when errors manifest in different components, such as modules, voters, RCN components, and other interconnection routes, different error signatures are generated. In order to localize these errors, the thesis demonstrates how the triplicated RCNs contribute to improving the precision and robustness of the TMR-MER technique. However, the error recovery of RCN components is complicated by the conventional design flow of TMR-MER not supporting the recovery of non-block oriented components. The interconnection routes of the RCN cannot therefore be recovered using this method. Whereas the work presented in [12] triggers a scrub cycle when a configuration error is detected in the RCN, this thesis proposes a fine-grained dynamic partial reconfiguration (FDPR) design flow that enables recovering routing components without resorting to scrubbing.

#### **1.1** Contributions

The work described in this thesis aims to discover improved RCN designs with respect to utilization and performance, to demonstrate how triplicated RCNs contribute to localizing errors, and to describe how a corrupted RCN is recovered other than by scrubbing the

device. The key contributions of this thesis are:

- To study and explore the Token Ring Network design proposed in [13] for the purpose of reconfiguration control with the aim of evaluating its utilization and performance as the number of network connections is increased;

- To carry out a comprehensive study and comparison of four alternative and realistic RCN topologies, namely, a star network, a bus, a token ring network and an ICAP-based readback approach, as proposed in the literature — the networks are compared in terms of logic and routing utilization, latency and SEU sensitivity as the network capacity increases — and to choose the best approach from among the interconnection methods studied;

- To demonstrate how the RCN is triplicated to enhance reliability; to explain how the response to the triplicated error requests should be prioritized; and to describe a fine-grained method for dynamically reconfiguring an incorrect RCN component;

- To further evaluate this fine-grained method and to compare the reliability, latency and energy cost of correcting configuration memory errors using the proposed approach with (1) an equivalent TMR-MER system that resorts to complete scrubbing of the device when errors are detected outside the TMR modules, (2) on-demand scrubbing of the device when any SEU is detected in the system, and (3) periodic scrubbing of the device as a fault prevention and correction strategy.

#### 1.2 Publications

- D. Agiakatsikas, N. T. Nguyen, Z. Zhao, T. Wu, E. Cetin, O. Diessel, and L. Gong, "Reconfiguration Control Networks for TMR Systems with Module-based Recovery," in 2016 IEEE 24rd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM). IEEE, 2016, pp. 88–91 [12]

- N. T. Nguyen, D. Agiakatsikas, Z. Zhao, T. Wu, E. Cetin, O. Diessel, and L. Gong, "Reconfiguration Control Networks for TMR Systems with Module-based Recovery," Submitted to Special Issue on Reconfigurable Computing and FPGA Technology, Journal of Parallel and Distributed Computing [14]

- Z. Zhao, D. Agiakatsikas, N. T. Nguyen, E. Cetin, and O. Diessel, "Fine-grained Module-based Error Recovery in FPGA-based TMR Systems," Accepted to 2016 International Conference on Field-Programmable Technology (FPT) [15]

My contribution towards developing the first and the second publications [12, 14] involves the investigation of four possible RCN architectures, including star networks, buses, a token ring network and an ICAP-based approach, as described in the literature; the redesign of these network topologies for evaluation; implementation of the four networks in a checkerboard-like synthetic layout and on the RUSH experimental payload [16]; and the setup of the fault injection campaign.

In the third publication [15], my contribution includes proposing the fine-grained modulebased error detection and recovery scheme that enhances the error localization and reconfigurability of the TMR-MER technique; to demonstrate the advantages of the proposed method using a test circuit; a fault injection campaign in order to identify the critical bits of different components and to record error signatures caused by these errors; and lastly, to compare the reliability, latency and energy cost of correcting configuration memory errors using the proposed approach, with those of the three more conventional approaches previously mentioned.

#### **1.3** Thesis Outline

The thesis is organized as follows. Chapter 2 provides motivation for the use of Commercial, Off-The-Shelf (COTS) SRAM-based FPGAs to the development of low-cost satellite systems. Chapter 2 also explains the radiation challenges and how radiation experiments prove that COTS FPGAs can be an alternative to radiation-hardened devices. We then summarize the advantages of the rapid SEU mitigation approach — TMR-MER over the traditional TMR-S.

Chapter 3 explains the early explorations on the Token Ring Network design [13] and evaluates its performance and utilization as the network size scales up. Thereafter, we propose an optimized alternative that has higher performance and lower resource utilization, when compared with the original design.

Chapter 4 investigates possible RCN topologies from the literature and proposes four network architectures based on the star topology, a bus, a token ring network and using the in-built FPGA configuration network (ICAP) for evaluation. We compare the latency, utilization, and upset sensitivity of the four alternatives by mapping them to a synthetic layout and to the RUSH experimental payload [16], as well as by injecting faults into each network.

Chapter 5 presents a fine-grained module-based error detection and correction approach based on triplicated RCNs, which improves the precision of the error detection of the TMR-MER technique and enhances its error correction capabilities in order to avoid resorting to scrubbing. We evaluate our method by implementing it on a typical application circuit, and via a fault injection campaign, we identify the critical bits of the various system components and validate the error correction ability in order to evaluate its reliability, latency and energy consumption. We also compare our results with those of more conventional approaches.

The last chapter concludes the thesis and outlines future research based on the work described in this thesis.

The thesis has two appendices. Appendix A includes an overview of the Xilinx 7-Series device configuration architecture, as discovered through our experiments, and describes the correlation between hardware resources and configuration memory frames, while Appendix B presents an overview of the configuration port facilities of 7-Series devices in order to explain how configuration memory frames are accessed using the internal registers to achieve high performance.

### Chapter 2

### Background

This chapter summarizes the research context including a summary of the benefits when Commercial Off-The-Shelf (COTS) Field Programmable Gate Arrays (FPGAs) are deployed in satellite applications, the radiation challenges in space, and the reasons why COTS FPGAs can be considered to be a feasible alternative to radiation-hardened FP-GAs.

#### 2.1 Why FPGAs in Space

FPGAs are Very-Large-Scale Integrated (VLSI) devices that are designed to be reprogrammed for user-specified functions after their manufacture. Typical user circuits range from merely simple logic gates, wires or buses to complex microprocessors and Systems-on-Chip (SoCs). A potentially important application area is implementing satellite payload applications. Compared with its alternative technology, Application-Specific Integrated Circuit (ASIC) devices, FPGAs have several advantages.

• Low Non-Recurring Engineering (NRE) costs. The hardware platforms for space missions are often built for specific purposes that have never been developed before, and most of which need to be heavily customized. The small market size, stringent development cycle and energy budget create significant NRE costs that cannot be offset [17]. FPGAs provide ideal hardware platforms that can be programmed to adapt their internal hardware resources to the type of logic circuit required. Compared with FPGAs, ASICs that also have prefabricated logic resources, have to be

re-fabricated for each application, which results in a long prototyping cycle and high development risk [18].

- Suitable for onboard processing applications. Remote sensing payloads require increasingly high data rates to reduce the amount of raw data that is to be sent for ground-based processing, but the radio link is low bandwidth and often unavailable [17, 19]. Under these conditions, FPGAs are widely used for low-level signal processing and compression applications [20].

- Field-upgradeable. FPGAs can be reprogrammed without having to be retrieved. The circuit implemented by FPGAs can be reconfigured remotely, and allows for in-orbit hardware upgrades. Ground-based communication stations can upload new configuration files for the FPGA on the satellite throughout its lifetime [21].

- Dynamically reconfigurable. State-of-the-art FPGAs allow dynamic hardware changes on part of its logic [22]. In dynamic hardware designs, the reconfigurable function blocks are only loaded when they are needed, which significantly reduces the power consumption and allows the hardware design space to be explored more completely [23].

#### 2.2 Challenges for Deploying FPGAs in Space

Space FPGAs need to be able to deal with three aspects of harsh environment conditions. These devices must survive the high mechanical and acoustic vibration during the rocket launch, and withstand high temperature ranges due to the vacuum in space, in which industry or military temperature grade devices, using appropriate packaging technology, are able to work safely. Moreover, the high level of ionizing radiation present beyond the Earth's magnetic field is the most serious threat to these devices [17].

#### 2.2.1 Radiation Effects

Just like other VLSI devices, FPGAs in space need to deal with radiation-induced effects, including Total Ionizing Dose (TID), Single Event Latchup (SEL), Single Event Upset (SEU) and Single Event Transient (SET), which are mainly induced by ionizing radiation caused by heavy ions, high-energy electrons and protons etc. striking the PN junctions of CMOS devices. Making matters worse is that for SRAM-based devices, SEUs may also

cause configuration memory errors, which can change the circuit state and/or behavior [24]. The detailed description of these radiation effects is as follows.

- TID can create parasitic leakage paths as more electric charges are trapped in the gate insulation layers of CMOS transistors. TID biases the gate and changes the threshold voltage Vth, which gradually defeats the transistors [25]. TID tolerance of a CMOS device is a factor that indicates its lifetime in space, which is also determined by the radiation harshness and manufacturing technique of the device.

- SEL is a potentially destructive effect that has long been a bane to CMOS circuits [26]. Latchup is a sequence of events occurring very quickly that change CMOS circuit behavior to become equivalent to that of a thyristor, causing failures of circuit function, which may furthermore destroy the device [27]. Among all cosmic rays, heavy ions are the main cause of latchup events, while high energy protons get less chances to produce latchup in silicon devices [28]. However, in modern CMOS processes, the susceptibility to SELs is reduced due to a reduction in Vcc [25].

- SEUs change the state of dynamic cells on electronic devices, which are always called soft-errors. In FPGAs, upsets can modify the data being processed by the circuit, as well as the configuration memory that determines the implementation of the circuit. The consequence of this effect is that it permanently corrupts the circuit function if the error persists in feedback cycles or in the configuration memory [2].

- SET is an upset due to a transient pulse induced in the wiring or combinational logic between storage cells arriving at the input of a latch on the latching edge of the clock, and the faster the clock speed, the greater the probability for latches to latch a transient signal [29].

#### 2.2.2 Radiation-hardening

In order to prolong the working life and to avoid errors and interrupts on the processing circuit, space-borne FPGAs are hardened in four aspects — architecture, manufacturing process, logic cell design, and redundancy scheme. Modern FPGAs are mainly based on SRAM, but anti-fuse FPGAs and flash-based FPGAs are more robust and common in space applications. Anti-fuse FPGAs do not require configuration memories and therefore SEUs will not corrupt the state of the circuit. Flash-based FPGAs, due to their higher reprogram voltage, are far less sensitive to configuration memory SEUs [30]. However, all three types of FPGAs are prone to the other effects and sacrifice adaptivity and dynamic

reprogram ability. Hardening approaches applied to the manufacturing process, such as the thin epitaxial wafer process, or Silicon-On-Insulator (SOI) technique [31, 32], can greatly reduce or completely preclude leakage current, parasitic capacitors and transistors, and trapped electron-induced degradations, and all of these cause the two destructive effects, TID and SEL [26, 33]. To overcome errors caused by SETs and SEUs, storage cells and configuration memory in space-borne SRAM-based FPGAs could be fabricated based on the Dual Interlocked storage Cell (DICE) design [34], which greatly improves the SEU resistance by nearly 1,000 times [32] while only doubling area, energy consumption and gate delay compared with standard SRAM cells [35]. Flip-flops could be preceded with SET filters, which can significantly reduce proton-induced short transients, but they may impose extra delay [36]. However, all of the above-mentioned hardening approaches are costly and cannot completely immunize the device against upsets, and as the transistor feature size shrinks, state-of-the-art FPGAs are becoming more vulnerable to soft errors [37]. Applying redundancy schemes such as Triple Modular Redundancy (TMR) is more important and effective than hardening logic cell designs [1]. As only latches are sensitive to upsets in anti-fuse and flash-based FPGAs, a unique flip-flop hardening approach using voter gate logic that is described in [38] has been applied to mitigate upsets in user flip-flops. With the majority of voting circuitry provided by the Triple Modular Redundancy (TMR) technique, a triplicated latch block can mask and detect errors occurring in one of the latches, while the error can also be corrected by asynchronous voting logic [38]. For SRAM-based FPGAs, as both latches and configuration memory cells are sensitive to upsets, combinational logic also needs to be triplicated and aided with configuration memory scrubbing approaches, which periodically sweep away errors that have accumulated in the device configuration memory [39].

Deploying Commercial, Off-The-Shelf (COTS) SRAM-based FPGAs has became more attractive than using radiation-hardened devices, as numerous radiation tests on Xilinx Kintex-7 XC7K325T FPGA [28, 40, 41] have proven this to be feasible. Table 2.1 provides a comparison of typical anti-fuse, flash-based, radiation-hardened SRAM-based and commercial-grade FPGA models in terms of their manufacturing process, logic cell features and density, performance, available soft-error mitigation approaches, and radiationtolerance. Commercial FPGAs cannot provide high radiation immunity, but are surprisingly resistant to TID and SELs, especially in Low Earth Orbit (LEO), and if proven to be sufficiently reliable, may even have applications in geosynchronous satellites. As reported in [28], no change in post-irradiation supply current was observed after the FPGA received an equivalent total dose of 17 krad(Si), which guarantees enough device lifetime in space for short duration and moderate radiation level missions, while the authors of [41] predict the latchup event rate to be  $9.2 \times 10^{-5}$  per device day in Geostationary Earth Orbit (GEO),

| Technique       | Anti-fuse           | Flash               | Rad-hard               | Standard              |

|-----------------|---------------------|---------------------|------------------------|-----------------------|

|                 |                     |                     | SRAM                   | SRAM                  |

| Device          | RTAX4000D           | RT4G150             | XQR5VFX130             | XC7K325T              |

| Family          | RTAX                | RTG4                | Virtex-5QV             | Kintex-7              |

| Vendor          | Microsemi           | Microsemi           | Xilinx                 | Xilinx                |

| Process         | 0.15 μm             | 65 nm               | 65  nm                 | 28 nm                 |

| Logic Cell      | C-Cell              | LUT-4               | LUT-6                  | LUT-6                 |

| Density         | 36K                 | 151K                | 131K                   | 326K                  |

| Speed           | 230 MHz             | 300 MHz             | 450 MHz                | 600 MHz               |

| TID Immunity    | 300 krad            | 100 krad            | 1,000 krad             | 17 krad               |

| Latchup Thresh- | 110                 | 110                 | 100                    | 15                    |

| old             | $MeV \cdot cm^2/mg$ | $MeV \cdot cm^2/mg$ | $MeV \cdot cm^2/mg$    | $MeV \cdot cm^2/mg$   |

| GEO Orbit Con-  | N/A                 | Immune [30]         | $3.80 \times 10^{-10}$ | $1.52 \times 10^{-8}$ |

| figuration Mem- |                     |                     | upsets/bit·day         | upsets/bit·day        |

| ory SEU Rate    |                     |                     |                        |                       |

| Embedded Miti-  | TMR-FF              | TMR-FF              | XTMR +                 | Scrubbing             |

| gation Approach |                     |                     | Scrubbing              |                       |

Table 2.1: Overview of FPGA Parameters & Radiation Immunity

and those observed latchups are non-destructive, which can be mitigated by discharging the device through the auxiliary power-rail. More importantly, in LEO, there are scarcely any heavy ions that could cause SELs on these commercial devices [28].

Commercial FPGAs are on the order of two magnitudes more sensitive to upsets than the other space-grade models. The SEU rate for a Kintex-7 device in the table is obtained from [28] using CREME96 [42] assuming a GEO orbit, solar minimum conditions, and 100 mils (2.54mm) of aluminum shielding, while that of the space-grade Virtex-5 device is from its datasheet [32] assuming a geosynchronous orbital altitude. As anti-fuse and flash architectures are not sensitive to configuration memory SEUs, their vendors only need to harden them by triplicating the flip-flops to protect user data. For the radiation-hardened SRAMbased FPGA model listed, Xilinx provides the XTMR tool and a configuration memory scrubber (IP block) [2] to boost the development of their space-grade FPGAs. However, the commercial-grade device model lacks ready-to-use upset mitigation approaches to deal with more intense soft-error rates. Since ground-based critical systems also have stringent reliability constraints [43], Xilinx has made the Soft Error Mitigation (SEM) controller [44] available for non-radiation hardened devices. However, commercial FPGAs are in urgent need of more flexible and comprehensive, reliable and portable SEU mitigation solutions. In general, commercial devices also need to rely on TMR techniques to mask and detect errors in user circuits, but approaches for correcting SEUs in configuration memory are