## NoC support for dynamic FPGA pages

#### **Eduard Warkentin**

Bachelor of Computer Science, TU Darmstadt, 2007

A thesis submitted in fulfilment of the requirements for the degree of

#### Master of Science

Darmstadt University of Technology, Department of Computer Science

THE UNIVERSITY OF NEW SOUTH WALES

March 2009

Copyright © 2009, Eduard Warkentin

## **Originality Statement**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

| Signed |  |  |  |  |  |

|--------|--|--|--|--|--|

|--------|--|--|--|--|--|

## Acknowledgements

I would like to thank my supervisor, Dr. Oliver Diessel, for his great support in this project. His supervision was exceptionally good and was critical for achieving such results. From the first moment he supported me in any reasonable way. I would also like to thank my examiner Prof. Dr.-Ing. Sorin A. Huss, who gave me the chance to investigate an interesting area of research abroad. Further, he provided excellent support from afar. I would like to thank my family which supported me throughout my initiatives.

#### Abstract

Module-based FPGA reconfiguration offers virtualization and multitasking capabilities, but to support this, many problems need to be solved. Current methodologies are very specific and are not capable of scaling or of being reused for other applications. This thesis proposes a methodology whereby the use of dynamic reconfiguration is supported for every core independent of the communication interface and communication needs. The infrastructure introduces a general interface for attaching and detaching dynamically reconfigurable modules and a Network on Chip (NoC) to provide communication between modules and off-chip resources. The approach advocates the regular layout of modules on the device, which are connected with a network, helping to generalize the interface and share the communication lines. The NoC provides essential advantages such as scalability, increased parallelism and simplifying the process of partial dynamic reconfiguration. The interface between NoC and reconfigured modules requires a glue logic. Guidelines were composed for designing a simple, working and reusable Network Interface core (NWIF) for a general types of cores. This allows to use the regular layout with the NoC as a communication medium for multitasking or virtualization, where the modules may be easily replaced. The results of implemented examples using the guidelines are presented. The performance compared to the conventional design is worse in the NoC design and the overhead is significant, but the reusability, generalism of the interface and the scalability of the framework are improved for future applications. Several avenues for improving the prototype developed in this work are exposed.

## Contents

| Li | st of            | Figur  | es                                              | X   |

|----|------------------|--------|-------------------------------------------------|-----|

| Li | $\mathbf{st}$ of | Table  | es :                                            | xiv |

| 1  | Intr             | roduct | ion                                             | 1   |

|    | 1.1              | Thesis | s Contributions                                 | 5   |

|    | 1.2              | Thesis | s Organization                                  | 6   |

| 2  | Bac              | kgrou  | nd and Related Work                             | 8   |

|    | 2.1              | Introd | luction                                         | 9   |

|    | 2.2              | FPGA   | A Pages - Distinct Clock Regions                | 10  |

|    |                  | 2.2.1  | The Virtex-4 FPGA Family                        | 10  |

|    |                  | 2.2.2  | The Virtex-5 FPGA Family                        | 11  |

|    |                  | 2.2.3  | The Virtex-6 FPGA Family                        | 11  |

|    | 2.3              | NoC -  | - Previous Work                                 | 13  |

|    | 2.4              | Suppo  | ort for Module-based Dynamic Reconfiguration    | 17  |

|    |                  | 2.4.1  | On-Demand Run-Time System by Ulmann             | 17  |

|    |                  | 2.4.2  | Erlangen Slot Machine (ESM) by Majer            | 18  |

|    |                  | 2.4.3  | Dynamic Network-on-Chip architecture (DyNoC) by |     |

|    |                  |        | Bobda                                           | 20  |

|    | 2.5              | Concl  | usion                                           | 21  |

| 3 | No  | C Supp | port for FPGA Pages                                      | 23 |

|---|-----|--------|----------------------------------------------------------|----|

|   | 3.1 | Requi  | rements of the system                                    | 23 |

|   |     | 3.1.1  | NoC                                                      | 24 |

|   |     | 3.1.2  | Page/Network Communication Interface                     | 25 |

|   |     | 3.1.3  | Inter Page Communication                                 | 27 |

|   |     | 3.1.4  | Shared Access to Common Ports                            | 28 |

|   | 3.2 | Const  | raining the Degrees of Freedom                           | 28 |

|   |     | 3.2.1  | Clock and Clock Regions                                  | 29 |

|   |     | 3.2.2  | IP-Cores                                                 | 29 |

|   | 3.3 | HERN   | MES - NoC Infrastructure                                 | 29 |

|   |     | 3.3.1  | Network on Chip                                          | 30 |

|   |     | 3.3.2  | HERMES Router and Interface                              | 30 |

|   |     | 3.3.3  | HERMES Interface Adaptation for PDR                      | 34 |

|   | 3.4 | Netwo  | ork Interface cores - Translator between Cores and NoC . | 37 |

|   |     | 3.4.1  | Role of the Network Interface                            | 37 |

|   |     | 3.4.2  | Design guidelines for Network Interface                  | 38 |

|   |     | 3.4.3  | Packet Layout and different Formats                      | 41 |

|   | 3.5 | Summ   | nary                                                     | 42 |

| 4 | Cus | stom D | Design for Dual AES                                      | 44 |

|   | 4.1 | Introd | luction                                                  | 44 |

|   | 4.2 | AES    |                                                          | 45 |

|   | 4.3 | Custo  | m Design without NoC and two AES Cores                   | 46 |

|   |     | 4.3.1  | Dual AES Interface                                       | 46 |

|   |     | 4.3.2  | Dual AES Controller                                      | 49 |

|   |     | 4.3.3  | Design Area and Timing Analysis                          | 52 |

|   | 4.4 | Host ( | Control Application                                      | 53 |

| 5 | No  | C Vers | ion Design and Implemantaion                             | 55 |

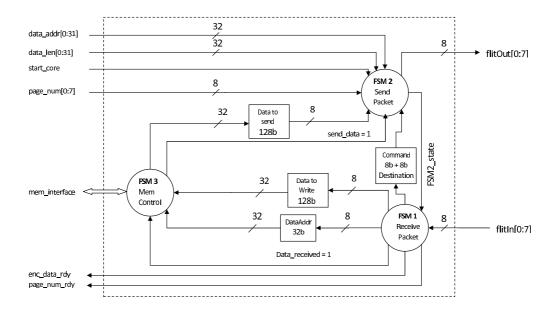

|   | 5.1 |                      | al Design with NoC, Memory Controller and Two AES            | 56 |  |  |

|---|-----|----------------------|--------------------------------------------------------------|----|--|--|

|   |     | 5.1.1                | Splitting the Dual AES Interface into two Network Interfaces | 56 |  |  |

|   |     | 5.1.2                | Packet Formats                                               | 58 |  |  |

|   |     | 5.1.3                | Operational Interface                                        | 60 |  |  |

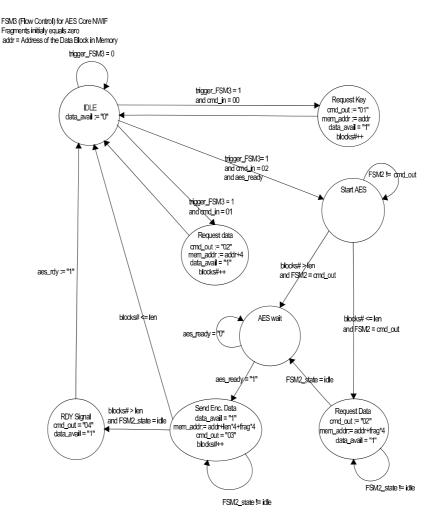

|   |     | 5.1.4                | Design of the AES Core NWIF                                  | 64 |  |  |

|   |     | 5.1.5                | Design of the Memory Controller NWIF                         | 68 |  |  |

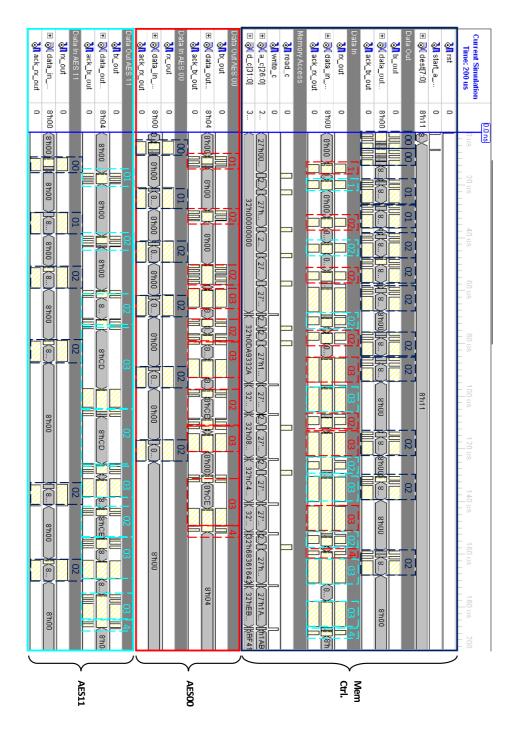

|   |     | 5.1.6                | Simulation                                                   | 69 |  |  |

|   |     | 5.1.7                | Design Area and Timing Analysis                              | 71 |  |  |

|   | 5.2 | Host (               | Control Application                                          | 73 |  |  |

|   | 5.3 | Concl                | usion                                                        | 73 |  |  |

| 6 | Ben | nchmarks and Results |                                                              |    |  |  |

|   | 6.1 | Comp                 | arison between Area and Timing Analysis for all Designs      | 74 |  |  |

|   | 6.2 | Bench                | mark Results                                                 | 76 |  |  |

|   |     | 6.2.1                | Test Pattern                                                 | 76 |  |  |

|   |     | 6.2.2                | One AES                                                      | 77 |  |  |

|   |     | 6.2.3                | Two AES                                                      | 78 |  |  |

|   |     | 6.2.4                | NoC with three AES Cores                                     | 82 |  |  |

|   | 6.3 | Discus               | ssion                                                        | 83 |  |  |

|   |     | 6.3.1                | Judgment of the Results                                      | 84 |  |  |

|   |     | 6.3.2                | Differences between the designs                              | 85 |  |  |

|   |     | 6.3.3                | Potential improvements for the Designs                       | 86 |  |  |

|   | 6.4 | Concl                | usion                                                        | 88 |  |  |

| 7 | Cor | clusio               | ns and Future Work                                           | 89 |  |  |

|   | 7.1 | Summ                 | nary and Conclusions                                         | 89 |  |  |

|   | 7.2 | Future               | e Work                                                       | 91 |  |  |

Bibliography 94

## List of Figures

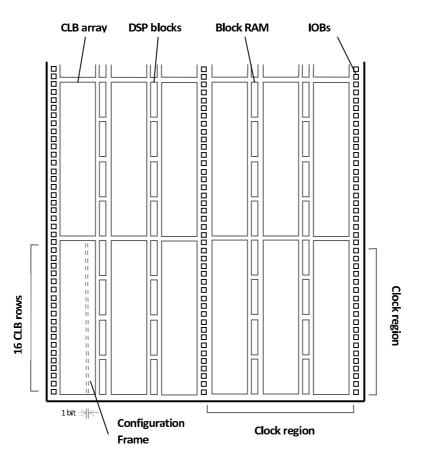

| 2.1 | Pages in an XC4VLX15 device. It consists of 8 independent         |    |

|-----|-------------------------------------------------------------------|----|

|     | clock regions. The figure shows the bottom half of the device     |    |

|     | and indicates the smallest reconfiguration unit (row) as well     |    |

|     | distinct clock regions [25]                                       | 12 |

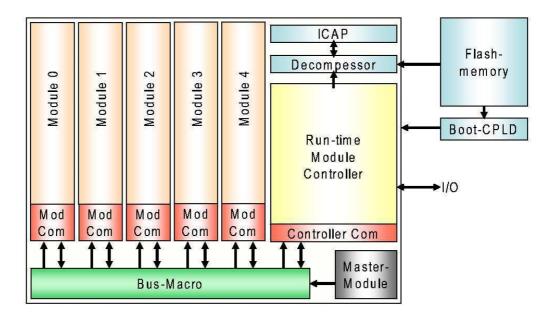

| 2.2 | On-demand run-time system (Ullmann et al.) $\dots$                | 18 |

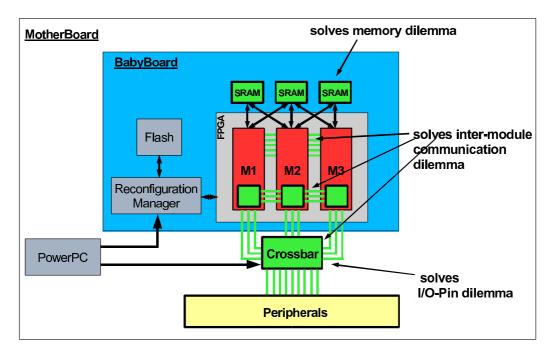

| 2.3 | The Erlangen Slot Machine (Majer et al.)                          | 19 |

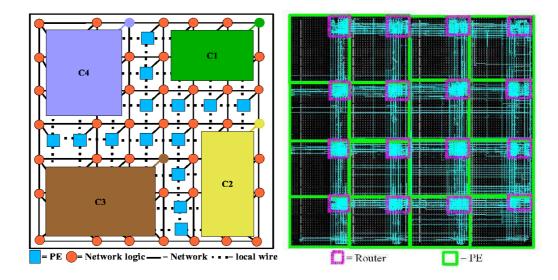

| 2.4 | DyNoC (left: conceptual, right: implemented) by Bobda et al.      | 21 |

|     |                                                                   |    |

| 3.1 | NoC mesh layout with intermediate Routers                         | 27 |

| 3.2 | HERMES router architecture. $B$ indicates input buffers $\dots$ . | 31 |

| 3.3 | Physical interface between routers in HERMES framework $$         | 32 |

| 3.4 | Interface between Artemis routers                                 | 35 |

| 3.5 | GAPH macros: (a) Fixed to Reconfigurable area (F2R); (b)          |    |

|     | Reconfigurable to Fixed area (R2F) [20]                           | 35 |

| 3.6 | Interface between Router and page, supporting partial dy-         |    |

|     | namic reconfigurable. Consists of Bus Macros from Figure 3.5      |    |

|     | and control signals                                               | 36 |

| 3.7 | General packet Layout, illustrating the layout in terms of OSI    |    |

|     | lavers                                                            | 41 |

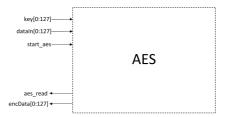

| 4.1 | AES core having three inputs and two outputs. Inputs are key and dataIn both 128 bits and start. The outputs are encData which is also 128 bits and ready. The AES core encrypts the data with a given key. The start signal is a control signal; the ready signal indicates when the data is finished with encryption                                 | 45         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

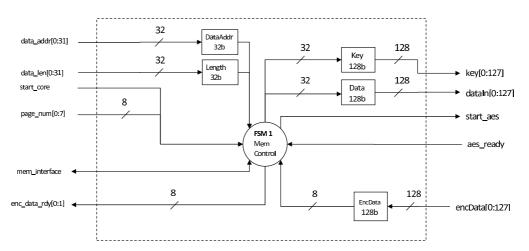

| 4.2 | Design module implementing a custom design with memory controller, dual AES controller and two AES cores                                                                                                                                                                                                                                               | 48         |

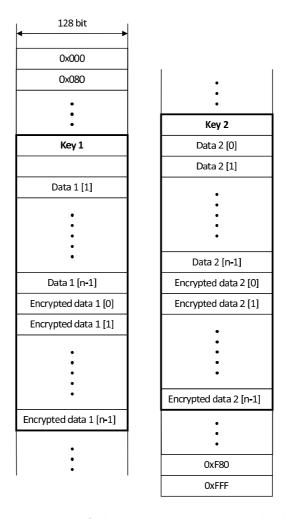

| 4.3 | Memory map of the communication model between the Host and both designs                                                                                                                                                                                                                                                                                | 49         |

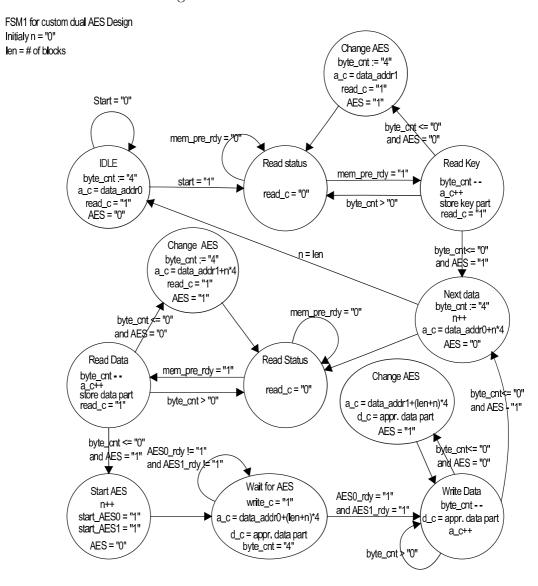

| 4.4 | Dual AES controller, it has one controll FSM and five buffer registers                                                                                                                                                                                                                                                                                 | 50         |

| 4.5 | FSM 1                                                                                                                                                                                                                                                                                                                                                  | 51         |

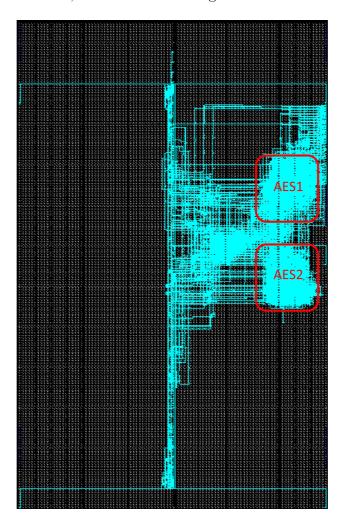

| 4.6 | FPGA floorplan for custom implementation for dual AES core                                                                                                                                                                                                                                                                                             | <b>F</b> 0 |

|     | design                                                                                                                                                                                                                                                                                                                                                 | 52         |

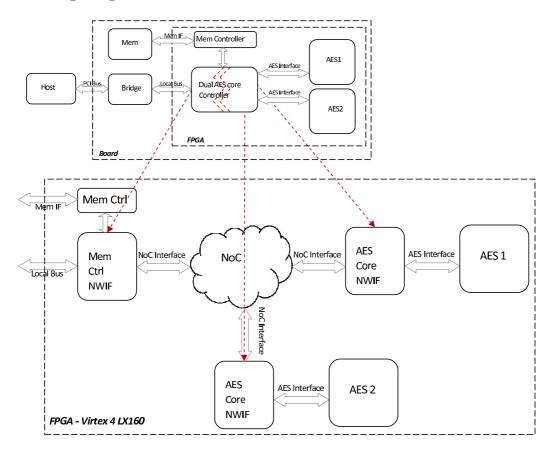

| 5.1 | Design of the NoC based implementation for multi AES core support. The dual AES core controller is split into two parts: the memory controller NWIF and an AES core NWIF. Custom connections are replaced by the HERMES NoC                                                                                                                            | 57         |

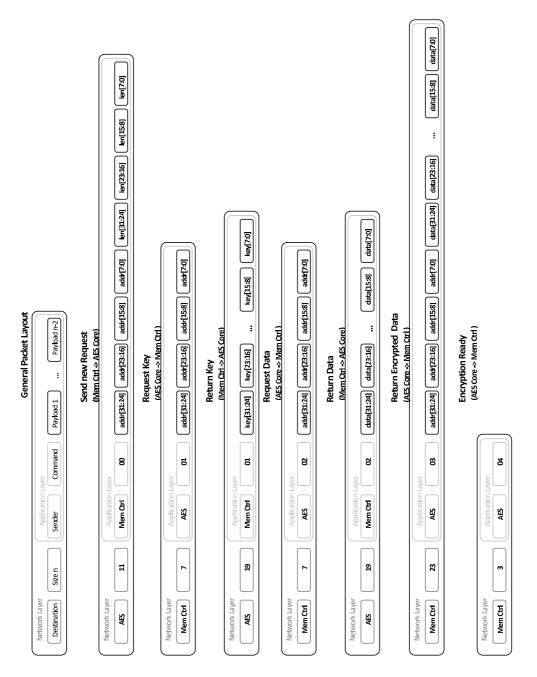

| 5.2 | Packet formats used in the current implementation. The first general packet Layout illustrates the arrangement and interpretation of each 8-bit flit                                                                                                                                                                                                   | 59         |

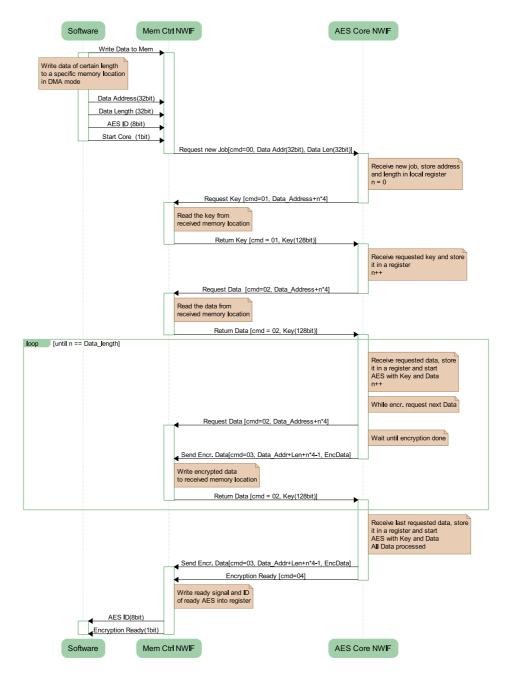

| 5.3 | Sequance diagram representing an example of communication among the three promponents $Host$ , $Memory\ Controller\ NWIF$ and $AES\ Core\ NWIF$ . In the example the Host writes $n$ blocks (each 128 bits) into memory, encrypts $n-1$ blocks and write the result back into the local memory and notifies the Host via an interrupt that it is ready | 62         |

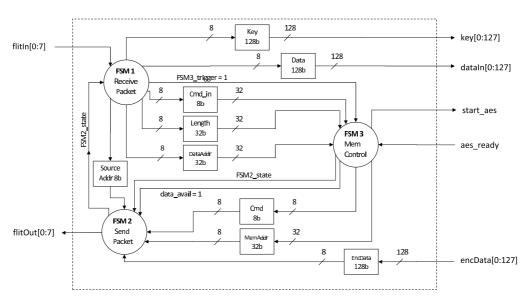

| 5.4 | The AES NWIF module consists of 3 FSMs and intermediate                                                                                                                                                                                                                                                                                                | 02         |

|     | buffers. FSM 1 receives packets, FSM2 sends packets and FSM 3 controls the AES core and estimates addresses for requesting                                                                                                                                                                                                                             |            |

|     | and reading data                                                                                                                                                                                                                                                                                                                                       | 64         |

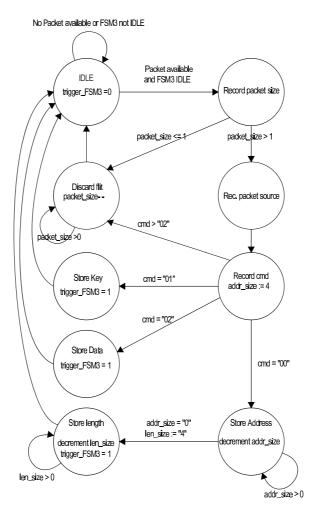

| 5.5  | disassembling routines                                                                                                                                                                                                                      | 65 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.6  | AES core NWIF FSM 3. Implements the control logic for the AES core and the next step including all relevant registers for the next packet                                                                                                   | 67 |

| 5.7  | AES core NWIF FSM 2. Implements the packet assembling and sending routines                                                                                                                                                                  | 68 |

| 5.8  | The memory NWIF module consists of 3 FSMs and intermediate buffers. FSM 1 receives packets, FSM2 sends packets and FSM 3 controls the memory controller                                                                                     | 69 |

| 5.9  | Timing diagram example for NoC design with two AES cores, where each AES core receives a job to encrypt 5 blocks. The rectangles marks different packets and the number in the rectangles defines the packet format according to Figure 5.2 | 70 |

| 5.10 | FPGA floorplan of the NoC design with two AES cores                                                                                                                                                                                         | 72 |

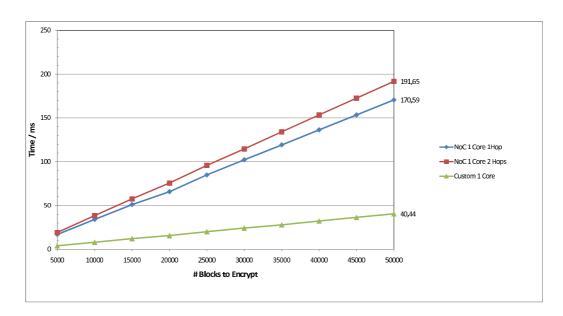

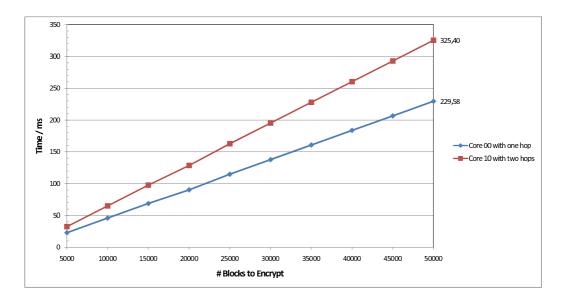

| 6.1  | Benchmark for single AES core in custom and NoC Design with one and two hops                                                                                                                                                                | 78 |

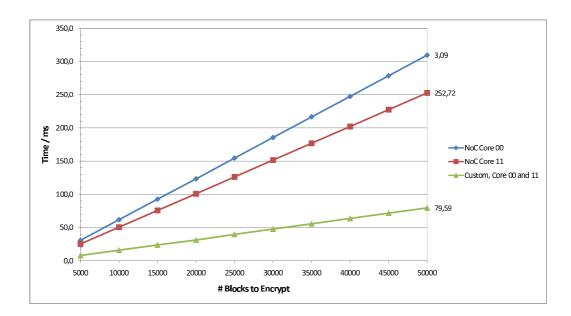

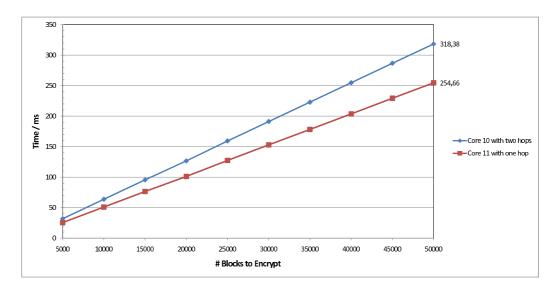

| 6.2  | Benchmark for two AES core in custom and NoC designs. The core 00 and core 11 lies one hop away from the Mem Ctrl. with ID 01. The arrangement maybe obtained in Figure 6.3                                                                 | 79 |

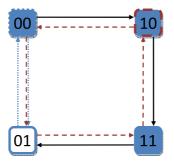

| 6.3  | Constellation where the <i>core</i> $\theta\theta$ and <i>core</i> $\theta\theta$ share, according to the XY routing algorithm, the output link. The Mem. Ctrl is the ID 01. The core 11 does not have any core attached                    | 80 |

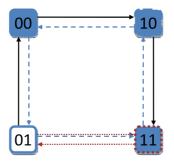

| 6.4  | Constellation where the <i>core 11</i> and <i>core 10</i> share the input link                                                                                                                                                              | 81 |

| 6.5  | Benchmark for two AES cores, where the <i>core 00</i> and <i>core 10</i> share, according to the XY routing algorithm, the output link. The Mem. Ctrl is the ID 01. The core 00 does not have any core attached                             | 81 |

| 6.6  | Benchmark for two AES cores where, the <i>core 11</i> and <i>core 10</i>                                                                                                                                                                    | or |

|      | shares the input link                                                                                                                                                                                                                       | 82 |

| 6.7 | Benchmark for three AES cores in the NoC design. The | he topol- |    |

|-----|------------------------------------------------------|-----------|----|

|     | ogy is illustrated in Figure 6.6                     |           | 83 |

## List of Tables

| 1.1 | Virtex-4 LX FPGA costs in US Dollars (source: Avnet February 2008)                                                                                                                                                                     | 4  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | State of the art in NoCs [22]                                                                                                                                                                                                          | 13 |

| 6.1 | Area and timing analysis of custom single AES design, custom dual AES design and NoC multi AES. First column gives the names of modules, second column shows the area of each modules in slices and the third column shows the maximum | 75 |

|     | speed for each module                                                                                                                                                                                                                  | 75 |

## List of Abbreviations

ASIC Application-Specific Integrated Circuit

PCI Peripheral Component Interconnect

CLB Configurable Logic Block

DES Data Encryption Standard

DSP Digital Signal Processing

DyNoC Dynamic Network-on-Chip

ESM Erlangen Slot Machine

FIFO First-In First-Out

FPGA Field-Programmable Gate Array

HDL Hardware Description Language

ICAP Internal Configuration Access Port

**IEEE** Institute of Electrical and Electronics Engineers

I/O Input/Output

IOB Input-Output BlockLUT Look-Up TableNoC Network-on-Chip

NP Non-deterministic Polynomial time

RAM Random Access Memory

RMB Reconfigurable Multiple Bus

RPM Relatively Placed Macro

VHDL Very-high-speed integrated circuit

Hardware Description Language

## Chapter 1

## Introduction

Field-Programmable Gate Arrays (FPGAs) are reprogrammable integrated circuits (ICs), comprising an array of logic blocks (cells) placed in an infrastructure of interconnections, which can be programmed at three distinct levels: (1) the function of the logic cells, (2) the interconnections between cells, and (3) the inputs and outputs. All three levels are configured via a string of bits, called a *bitstream*, that is loaded from an external source, either once or several times while the device is powered on. However, this potential power necessitates a suite of tools in order to design a system. Essentially, these tools generate the configuration bitstring, given such inputs as a logic diagram or a high-level functional description.

FPGA design tools start by synthesizing an application circuit specified in a design language such as VHDL [12] or Verilog [13] into a *netlist*, which is mapped to a particular FPGA, thereby creating a *circuit description*, and finally generating the configuration bitstream for this circuit description. Once the bitstream is loaded into the configuration memory of the FPGA, it be-

haves like the application circuit description that was synthesized at the start of the design flow. Thereafter, loading a different bitstream to change the circuit on the device is known as a *reconfiguration*.

FPGAs like the Xilinx Virtex-4 family [30] offers an opportunity to reconfigure the device in a partial and dynamic manner. After the bitstream is loaded and the FPGA is operating it is possible to reconfigure a part of the device, while the remaining parts are continue running. This reduces the amount of data that needs to be transferred as well the time needed for reconfiguration. In the literature, the names for this procedure are not unique, the common variants are runtime partial reconfiguration or partial dynamic reconfiguration (PDR).

The Virtex FPGA family supports two basic styles of partial reconfiguration: module-based and difference-based. Module-based partial reconfiguration uses modular design concepts to reconfigure large blocks of logic. The distinct portions of the design to be reconfigured are known as reconfigurable modules. Because specific properties and specific layout criteria, such as communication interface and 2D communication layout, must be met with respect to a reconfigurable module, any FPGA design intending to use partial reconfiguration must be planned and laid out with that in mind [29].

Partial dynamic reconfiguration opens up a variety of applications across many industries. It potentially increases system performance. Although a portion of the design is being reconfigured, the rest of the system can continue to operate. There is no loss of performance or functionality with unaffected portions of a design i.e., no down time. It also allows for multiple applications on a single FPGA [31].

Embedded systems often use FPGAs, because they offer the ability to provide alternative hardware components. If the system requires two or more hardware components and only one is active at the time, it may be possible to use a FPGA and reconfigure it as the situation demands. Some industries already uses this approach, e.g. in aeronautic, automotive, multimedia, industrial process control. But most designs targeted at the FPGA are static and do not change during operation.

The potential to partially reconfigure FPGAs at run time, introduces many benefits to the designer. The most relevant for this thesis is supporting so-called hardware virtualization, where a design is generally partitioned and swapped over time onto the FPGA. This allows the designer to fit a larger design onto a smaller FPGA [28]. Because of the high cost of the larger FPGAs it may be beneficial to partition the design and run it on a smaller FPGA in order to reduce part cost and power consumption. This is especially advantageous, since a larger device is almost twice the cost of the next smaller alternative, shown as the multiplicative factor in parentheses in Table 1.1, which lists the average prices of Virtex-4 devices from Avnet as of February 2008. Note that the price per logic cell also increases as the device size grows [16].

Since the size of modern FPGA scales gradually, an alternative use of partial dynamic reconfiguration in FPGA may be preferred, where by the high cost of resources (e.g. chip cost, power consumption) may be be shared among many applications. This would enable multitasking systems and increase the overall utilization of a device. Multitasking on an FPGA-based processor is one possibility to explore the efficacy of reconfigurable comput-

| Device    | Logic Cells | Average Price     | Price/Logic Cell |

|-----------|-------------|-------------------|------------------|

| XC4VLX15  | 13,824      | \$206.22          | \$0.0149         |

| XC4VLX25  | 23,192      | \$420.63 (×2.04)  | \$0.0181         |

| XC4VLX40  | 41,472      | \$608.13 (×1.45)  | \$0.0147         |

| XC4VLX60  | 59,904      | \$928.75 (×1.53)  | \$0.0155         |

| XC4VLX80  | 80,640      | \$1493.75 (×1.61) | \$0.0185         |

| XC4VLX100 | 110,592     | \$2816.25 (×1.89) | \$0.0255         |

| XC4VLX160 | 152,064     | \$4560.63 (×1.62) | \$0.0300         |

| XC4VLX200 | 200,448     | \$8320.00 (×1.82) | \$0.0415         |

**Table 1.1:** Virtex-4 LX FPGA costs in US Dollars (source: Avnet February 2008)

ing. Conventional computers and operating systems have demonstrated the many advantages of sharing computational hardware by several tasks over time. The ability to do run-time configuration allows the opportunities of multitasking to be investigated.

Design complexity, verification, and time-to-market pressures encourage reuse of components and designs that are tried and proven. Module-based design methodologies form a class of higher-level design methods that focus on implementing a design that is specified or described in terms of its constituent modules [6][14]. As such, dynamic reconfiguration at the module level is ideal for implementing hardware virtualization or multitasking [16].

Modular dynamic reconfiguration is currently not widely used in the industry, the reason could be the lack of practical methods and frameworks. If the vendor wants to design a partial reconfigurable system, it has to develop all the communication interface between static and reconfigurable part from scratch. This entails that the system designer must have intimate knowledge of the FPGA device architecture and partial reconfiguration, and how to best design an application for dynamic reconfiguration. If this step would be generalized and developed into a well known procedure, maybe vendors would use it more often.

This thesis investigates a general approach for communication and a general communication interface between IP blocks. In doing so, it presents a specific Network on Chip (NoC) and proposes a top-down methodology for implementing the interfaces used by the *NoC*. This work proposes a framework in which the partial dynamic reconfiguration can be done without caring about the connections between modules. This framework is implemented on the the Virtex-4 FPGA family [30] and has some limitations, which makes it possible to focus on the investigation in a relevant scope.

#### 1.1 Thesis Contributions

This thesis focus on difficulties using FPGAs in a multitasking manner. Concurrent usage of the input and output resources, while using an NoC infrastructure, is the main focus of this work. Another point of investigation is a general interface for communication between IP modules and the NoC, allowing partial dynamic reconfiguration of modules without errors in the NoC. The decision was made to use an already available NoC infrastructure named HERMES from the GAPH group [22] and to examine the sufficiency of this Infrastructure for the needs of the multitasking FPGA environment with highly concurrent inputs and outputs.

A general guide is presented for designing so-called glue logic or wrappers between the modules and the NoC interfaces. A top-down methodology is presented, in which a custom design is modified into an NoC design. An extension is also made for general signals, where different signal approaches were examined and the implementation models into NoC infrastructure were worked out.

This thesis also proposes a test implementation of a custom design, which uses two AES cores for test purposes. The custom design uses conventional design methods and implements a single purpose system in which the speed is optimized. This custom system serves the role of a reference design against which the NoC infrastructure is tested. Further the thesis proposes an implementation of an NoC - based design with multiple AES core. The AES cores network interface is designed in a general manner, and this allows reuse of the implementation.

This work advocates the use of NoC infrastructure and proving the feasibility by proposing some experiments, where the performance of the custom design and NoC designs are evaluated.

This work discovers also some possible improvements, which are presented and are a target for future development.

## 1.2 Thesis Organization

The relevant background and state of the art is discussed in the Chapter 2. It gives an overview of the idea to use *pages* for implementing reconfigurable modules and possible advantages. Further it addresses the general discussion about benefits and drawback of an NoC for communication.

Chapter 3 presents the main methodologies and constraints in this work. It gives an overview of the general requirements for page-based communication and of the NoC infrastructure (HERMES). The methodology for for designing of network interfaces forms the main part of this Chapter.

The custom design for two AES cores is presented in details in the Chapter 4. The implementation of the interface between the memory, PCI bus and the host application is systematically illustrated.

Chapter 5 addresses the implementation design of the NoC with multiple AES cores, where the relevant NoC parameters are discussed, the particular example of the designing a network interface for an AES core ,memory controller and a PCI bus, is presented. Further, the packet formats that are proposed to be used in this particular implementation are outlined.

The Chapter 6 presents an evaluation of the effectiveness of NoC communications compared to a conventional custom design. Experimental benchmarks for assessing the performance of custom designs and NoC designs are introduced and the results of the experiments are presented and explained. Further the results are discussed and a preliminary evaluation is made. Based on the results, some suggestions for further improvement are presented.

The last Chapter 7 concludes this thesis with a summary of the work and its evaluation. Further directions for future work and improvement are proposed.

## Chapter 2

## Background and Related Work

This chapter presents the relevant background for the scope of the thesis: the support for pages in todays FPGAs is presented (Section 2.2), a general approach to page-based communication is described in Section 2.1, and an overview of the previous work is given.

This thesis is based on NoC communication, which has to replace the static wiring concept between modules of earlier work by Shannon Koh [15]. This chapter illustrates in the Section 2.3 the previous work done on NoC, and introduces aspects such as topology, flit size, buffering, router area, performance and implementation.

The last section presents an overview of previous work in support for module-based dynamic reconfiguration.

#### 2.1 Introduction

To divide the FPGA into fixed pages and use the pages for virtualization of designs comes from the well known approach of virtual memory. But the concept of virtual memory is quite simple, it requires to store the data for some period of time. In the FPGA world this approach needs more capabilities, such as communication ability to other pages and to the off chip resources.

The next section analyzes the Xilinx FPGA families for feasibility for FPGA paging. One of the newest capabilities of the Virtex 4/5 families is the option to run particular parts of the FPGA with distinct clock speeds. This option allows the FPGA to be shared and run several applications with different timing, where by those can still communicate with each other. However, it is exactly this option that causes some new issues for the communication interface, since it connects different clock regions and still has to be general.

The paged FPGA approach allows the FPGA resources to be used for various applications running in parallel. Today, FPGAs are mostly used for single applications. Using pages, it becomes feasible not just to reconfigure the FPGA during the operation as the autonomous system demands, but to use the FPGA for multitasking purposes. FPGAs are playing the role of a multipurpose processor which is controlled by an operating system. The methodologies used by virtual memory approach are similar to the framework introduced by FPGA paging.

The communication between pages needs to describe a general interface in terms of supporting partial dynamic reconfiguration for swapping/programming a page. Some approaches to this communication problem are already presented by other research work, but the main problem with this is a lack of scalability and generality. In Section 2.4 some related research works are presented and discussed.

## 2.2 FPGA Pages - Distinct Clock Regions

Each Xilinx Virtex FPGA Family has specific characteristics, which need to be known to be able to design a page-based application framework. For example, the distinct clock regions and the smallest partial reconfiguration frame are different in each generation. This Section gives an overview about last three Virtex FPGA generations and their ability to support paging.

## 2.2.1 The Virtex-4 FPGA Family

Since the Virtex-4 FPGA Family [30] was introduced by Xilinx in 2004, the support for partial reconfiguration has changed and allows more flexibility for users and introduces the ability for page oriented reconfiguration.

Previous Virtex Families, such as Virtex-2, allowed reconfiguring a frame spanning the entire hight of a FPGA device as a smallest unit. This makes use of pages not feasible. The Virtex-4 family introduces new architecture improvement specific to partial reconfiguration, where the smallest reconfiguration frame consists of 16 CLB in the hight and the entire hight consists of multiple of 16 CLB rows.

Independent clock regions were introduced first in Virtex-4 Family, this allows applications to run inside one or more clock regions with different timing constrains. So the smallest Virtex-4 FPGA has 8 such independent clock domains and the largest device has 24.

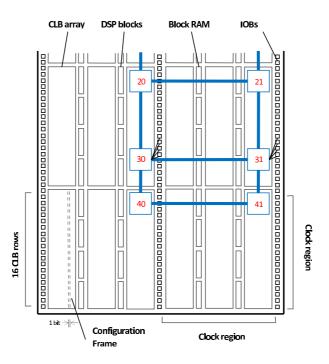

New options provided in Viretex-4 were the intention to introduce the idea of paging. So a page is an area on a chip with an independent clock region, where each row of 16 CLBs may be reconfigured dynamically. Figure 2.1 shows the bottom half of the layout in a smallest Virtex-4 FPGA, overall it has 8 distinct clock domains.

#### 2.2.2 The Virtex-5 FPGA Family

In 2006 the Virtex-5 FPGA generation was introduced and brought some new options [32]. The architectural structure for partial reconfiguration remains the same and does not have any impact on the proposed paged-based reconfiguration scheme, except that the smallest reconfigurable unit consists of 20 CLB rows in this device family.

Important improvements to the Virtex-4 architecture included 6-input LUTs, diagonal routing and an increased maximum clock frequency of 550 MHz compared to the Virtex-4 at 500 MHz.

## 2.2.3 The Virtex-6 FPGA Family

In February 2009, Xilinx introduced the next generation of Virtex family the Virtex-6 FPGA [33]. The changes made to the architectural structure

**Figure 2.1:** Pages in an XC4VLX15 device. It consists of 8 independent clock regions. The figure shows the bottom half of the device and indicates the smallest reconfiguration unit (row) as well distinct clock regions [25]

for partial reconfiguration is an increase to the page size, now it is doubled compared to Virtex-5 family and the smallest unit is a column of 40 CLBs.

Since the smallest unit consists of 40 CLB rows, the amount of the clock regions has slightly decreased compared to previous generations to 6 - 18. If before there were some concerns about the size of a page, now the page is quite large and it allows fitting larger cores into it.

## 2.3 NoC - Previous Work

| NoC                     | Topology              | Flit Size         | Buffering              |                       | Perfor.                | $\mathbf{QoS}$          | Impl.             |

|-------------------------|-----------------------|-------------------|------------------------|-----------------------|------------------------|-------------------------|-------------------|

|                         |                       |                   |                        | Area                  |                        |                         |                   |

| aSOC-                   | 2D Mesh               | 32 bits           | None                   | 50,000                |                        | Circuit                 | ASIC lay-         |

| 2000 [17]               | Scalable/ De-         |                   |                        | transistors           |                        | switch-                 | out CMOS          |

|                         | termined by           |                   |                        |                       |                        | ing(no                  | 0.35m             |

|                         | application           |                   |                        | 9                     |                        | wormhole)               |                   |

| Dally-                  | Folded 2D             | 256 bits          | Input                  | $0.59 \ mm^2$         | 4 Gbits/s              | Guarant.                | No                |

| 2001 [8]                | Torus 4x4/            | data +            | queue                  | CMOS                  | per wire               | Through-                |                   |

|                         | XY Source             | 38 bits           |                        | 0.1m                  |                        | put (vir-               |                   |

|                         |                       | control           |                        |                       |                        | tual chan-              |                   |

| 2.6                     | 2D T                  | 10 11             | * * * * 1              | 4.40 1:               | 2227 (1:1: /           | nels)                   | EDGA              |

| Marescaux-<br>2002 [19] | 2D Torus (scalable) / | 16 bits<br>data + | Virtual                | 446 slices<br>Virtex- | 320Mbits/s<br>per vir- | 2 time mul-<br>tiplexed | FPGA<br>Virtex-II |

| 2002 [19]               | XY blocking,          | 3 bits            | output<br>queue        | II(4.8%               | per vir-<br>tual       | virtual                 | Virtex-11         |

|                         | hop-based,            | control           | queue                  | area over-            | channel                | channels                |                   |

|                         | deterministic         | COLLIO            |                        | head for              | at 40                  | Chamieis                |                   |

|                         | deterministic         |                   |                        | XCV800)               | MHz                    |                         |                   |

| Rijpkema-               | 2D Mesh               | 32 bits           | Input                  | 0.26 mm2              | 80Gbits/s              | Circuit-                | ASIC lav-         |

| 2002 [23]               |                       |                   | queue                  | CMOS                  | per                    | switching               | out               |

| [24]                    |                       |                   | 1                      | 0.12m                 | switch                 | (guar-                  |                   |

| . ,                     |                       |                   |                        |                       |                        | anteed                  |                   |

|                         |                       |                   |                        |                       |                        | through-                |                   |

|                         |                       |                   |                        |                       |                        | put)                    |                   |

| Hermes-                 | 2D Mesh (scal-        | 8 bits            | Input                  | 631 LUTs              | 500                    | No                      | FPGA              |

| 2003 [22]               | able) / XY            | data +            | queue                  | 316 slices            | Mbits/s                |                         | Virtex-II         |

|                         |                       | 2 bits            | (paramet-              | Virtex-II             | per                    |                         |                   |

|                         |                       | control           | erizable)              |                       | switch at              |                         |                   |

|                         |                       | (paramet-         |                        |                       | 25 MHz                 |                         |                   |

| 37 1.137 0              | 25.11.1               | erizable)         | <b>.</b>               | 004 1117              | 4 (1) : /              |                         | FDGA              |

| MultiNoC-               | 2D Mesh (scal-        | 8 bits            | Input                  | 631 LUTs              | 1 Gbit/s               | No                      | FPGA              |

| 2005 [20]               | able) / XY            | data + 2 bits     | queue                  | 316 slices            | per<br>switch at       |                         | Virtex-II         |

|                         |                       | control           | (paramet-<br>erizable) | Virtex-II             | switch at 50 MHz       |                         |                   |

|                         |                       | (paramet-         | erizabie)              |                       | JU MIIIZ               |                         |                   |

|                         |                       | erizable)         |                        |                       |                        |                         |                   |

| DvNoC-                  | 2D Mesh               | 32 bits           | six 32-                | 0,5% of               | Timing                 | No                      | Virtex-II         |

| 2005 [3]                | / custom              | data + 4          | bit FIFO               | Virtex-II             | 391 MHz                | 110                     | 6000              |

| _500 [0]                | routing               | control           | buffers                | 6000                  | 551 11112              |                         |                   |

|                         | 0 000000              |                   |                        |                       |                        |                         | l                 |

Table 2.1: State of the art in NoCs [22]

This Section is intended to provide a big picture of the state of the art in Network on Chip (NoC) propositions. The results of the review are summarized in Table /reftab:NoCs. In this Table, each row corresponds to an NoC model that could be found in a liturature. The NoC parameters considered relevant can be divided into three groups: (i) structural information, presented in the four first columns; (ii) performance information, in the fol-

lowing three columns; (iii) prototyping or silicon implementation details, in the last column.

Although the authors do not pose claims about the completeness of this review, they consider it rather comprehensive. Benini, De Micheli and Ye made important contributions to the NoC subject area in their conceptual papers [21] [2] [27]. However, none of these documents contains any NoC implementation details, except HERMES NoC [22], where MultiNoC is based on HERMES NoC

Each NoC defining parameter is described in detail below, together with an evaluation of the relative merits of each reviewed NoC proposition.

Almost all reviewed NoCs are based on packet switching and this is not stated in the table. The exception is the paper proposing the aSOC NoC [17], where the connection for each packet is fixed after the synthesis step. The first column in the Table 2.1 describes the topology of the NoC and the switching strategy. The most common topology used by many authors is a 2D mesh topology, it offers facilitated implementation using current IC planar technologies, simplicity of the XY switching strategy and network scalability. Another approach is to use the 2D torus topology, to reduce the network diameter [19]. The folded 2D torus presented by Dally [8] is an option to reduce the increased cost in wiring compared to a standard 2D torus. Concerning switching strategies, there is a clear lack of published information on specific algorithms. This indicates that further research is needed in this area. For instance, it is widely known that XY adaptive algorithms are prone to deadlock, but solutions exist to improve XY routing without causing deadlock risk.

The second important quantitative parameter of NoC switches is the flit size. From Table 2.1 it is possible to classify approaches into two groups, those focusing on future SoC technologies and those adapted to existing limitations. The first group includes the proposal of Dally [8], where switching channels are supposed to be 300-wire wide without significantly affecting the overall SoC area. However, this is clearly not feasible for today's FPGAs. The second group comprises works with flit sizes ranging from 8 to 64 bits, a data width similar to current processor architectures. The works providing an NoC prototype, Marescaux [19] and Moeller [22], have the smallest flit sizes, 16 and 8 bits, respectively.

The next parameter in Table 2.1 is the switch buffering strategy. Most NoCs employ input queue buffers. Since input queuing implies a single queue per input, this leads to lower area overhead, justifying the choice. Another solution is to use virtual output queuing associated with time-multiplexed virtual channels, as proposed in [19].

Another important parameter is the queue size, which implies the need to solve the compromise among of the amount of network contention, packet latency and switch area overhead. A bigger queue leads to small network contention, higher packet latency, and bigger switches. Smaller queues lead to the opposite situation.

The fourth column collects results concerning the size of the switch. It is reasonable to expect that the adoption of NoCs by SoC designers be tied to gains in intra-chip communication performance. On the other hand, low area overhead when compared with e.g. standard bus architectures is another important issue. A SoC design specification will normally determine

a maximum area overhead allowed for intra-chip communication, as well as minimum expected communication performance, possibly on an IP by IP basis. Switch size, flit size (i.e. communication channel width) and switch port cardinality are fundamental values to allow estimating the area overhead and the expected peak performance for intra-chip communication.

Estimated peak performance, presented in the fifth column of Table 2.1, is a parameter that needs further analysis to provide a meaningful comparison among different NoCs. In this way, this column displays different units for different NoCs. This column must accordingly be considered as merely illustrative of possible performance values. Most of the estimates are derived from the product of three values: number of switch ports, flit size, and estimated operating frequency. The wide variation of values is due mostly to the last two values. No measured performance data could be found in any reviewed publication.

Next comes the quality of service (QoS) support parameter. The most commonly found form of guaranteeing QoS in NoCs is through circuit switching. This is a way of guaranteeing throughput and thus QoS for a given communication path. The disadvantage of the approach is that bandwidth may be wasted if the communication path is not used at every moment during the time the connection is established. In addition, since most approaches combine circuit switching with best effort techniques, this brings as consequence the increase of the switch area overhead. This is the case for NoC proposals presented in [8] and [23]. Virtual channels are one way to achieve QoS without compromising bandwidth, especially when combined with time division multiplexing (TDM) techniques. This last technique, exemplified

in [19] avoids that packets remain blocked for long periods, since flits from different inputs of a switch are transmitted according to a predefined time slot allocation associated with each switch output. It is expected that current and future SoC utilization will be dominated by streaming applications. Consequently, QoS support is regarded as a fundamental feature of NoCs by the authors. [22]

Finally, it is possible to state that NoC implementation results are still very scarce. None of the two ASIC implementations found in the literature gives hints to whether the design corresponds to working silicon. In addition, four NoCs have been reported to be prototyped in FPGAs, those proposed in [19],[22] and [3].

# 2.4 Support for Module-based Dynamic Reconfiguration

## 2.4.1 On-Demand Run-Time System by Ulmann

Ullmann et al. [26][10][11] proposed the *On-Demand Run-Time System* as shown in Figure 2.2. This system implements a custom bus system, and attached to it, four areas for dynamically reconfigured modules. It also implements bitstream decompression and self-reconfiguration via the ICAP.

Figure 2.2: On-demand run-time system (Ullmann et al.)

The bus protocol overheads still exist. In addition, there can be long routing paths from the top of the modules to the bus interfaces at the bottom and then through the bus network (labeled as "Bus-Macro" in Figure 2.2). It is also unclear as to how one designs applications targeted to this system.

## 2.4.2 Erlangen Slot Machine (ESM) by Majer

One-dimensional, slot-based approach is the Erlangen Slot Machine (ESM) by Majer et al. [18]. The ESM is composed of two boards: a BabyBoard and a MotherBoard, as shown in 2.3. The MotherBoard is composed of a crossbar switch that links external I/O to the BabyBoard, and a PowerPC that runs software to control the application. The BabyBoard has a reconfigurable Virtex-II FPGA, SRAM and a reconfiguration manager responsible

for bitstream relocation and loading. Modules are loaded into fixed-sized slots M1-M3 on the Virtex-II FPGA.

Figure 2.3: The Erlangen Slot Machine (Majer et al.)

There are four levels of inter-module communications provided on the ESM: shared SRAM gives access to two neighboring modules among each other, direct communication between adjacent modules by using bus macros, non-neighboring modules can communicate via a modified version [1] of a Reconfigurable Multiple Bus (RMB) [9] and the crossbar is used for off-chip communication.

This approach also suffers from area and timing overheads required to manage the system and its communications. The RMB requires crosspoint modules consisting of a controller, FIFOs and data network. External I/O is very expensive as it has to go off-chip into another FPGA, which in turn has to be routed through the crossbar and then off-chip again to the actual

peripherals or off-chip logic. The delay of the crossbar itself is 15 ns with an 18 clock-cycle setup time.

Programming such a system is an extremely complex task. The multiple levels of communication and application management add a high degree of complexity at the application design level.

# 2.4.3 Dynamic Network-on-Chip architecture (DyNoC) by Bobda

Two-dimensional approaches offer more flexibility in placement and thus the possibility of shorter intermodule wiring paths. The Dynamic Network-on-Chip architecture (DyNoC) proposed by Bobda et al. [3] [4] is a two-dimensional network-on-chip with routers laid out in a grid on an FPGA (see Figure 2.4). Rectangular modules of any size can be placed onto the network. Routers are disabled if they are temporarily obscured by a module placed over them, and are re-enabled when the module is removed.

It is a complex task to determine the appropriate set of shapes and placements of the modules in the application such that area and timing constraints are met. This is accentuated by the fact that it is very difficult to provide network bandwidth guarantees. The complete temporal communication patterns of the application must be known. Even then, doing so requires that multiple NP-hard problems be solved, as determined by Chan et al. [5] in addressing a similar problem in NoC topology generation and module shaping.

Figure 2.4: DyNoC (left: conceptual, right: implemented) by Bobda et al.

Finally, some area of the chip is underutilized because a ring of unobscured routers must surround every module in order to ensure routability.

Technically speaking, a two-dimensional layout such as this is counterintuitive to the reconfiguration mechanism of the Virtex and Virtex-II devices. Since a configuration frame spans the entire height of the device reconfiguring a module that is wider than it is high will take longer than one of the same size that is rotated 90 degrees. This tends to indicate that the best way to lay out modules would be to pack them into the narrowest possible rectangles, thereby reverting to a one-dimensional layout.

#### 2.5 Conclusion

This Chapter discussed the background found in the literature about NoC implementations and their support for partial dynamic reconfiguration. The approaches provide quite complex frameworks with impracticable limitations.

Further, the approaches provide an overview of how they are supposed to be implemented, but do not give application examples where they would be suitable.

The scope of paged design in newer FPGA families was also analyzed and the benefits stated. The main advantages offered by pages is virtualization and multitasking ability, but the proposed requires a general interface and suitable NoC support. After the research of previous work, it was concluded to use the HERMES [22] NoC framework because of its simplicity, low level of overhead, provided examples, and available simulation framework.

# Chapter 3

# NoC Support for FPGA Pages

The concept of "pages" supported by todays FPGAs is the main idea of this thesis and it is explored in this chapter. In Section 3.1 this chapter presents the requirements of the system for supporting pages. The NoC HERMES, configured as a suitable communication media, is presented in Section 3.3. The degree to which the design freedom was constrained is explained in Section 3.2. Furthermore, Section 3.4 presents the importance and design guidelines followed for the *Network Interface Core* (NWIF) in this work.

# 3.1 Requirements of the system

This Section gives an overview of the requirements imposed by the "paged" use of an FPGA. Paged use of an FPGA refers to capability of modern FPGAs to reprogram independent, rectanglular areas. Further, each of such rectangles forms an independent clock domain (See Section 2.2.1).

One of the main requirements of a paged dynamic reconfiguration method is a generalized communication approach. This requirement is presented in Section 3.1.1. The appropriate requirements of the interfaces supporting pages is described in Section 3.1.2. The model of communication, required to be supported by interpage and off-chip communications, is presented in Sections 3.1.3 and 3.1.4.

#### 3.1.1 NoC

Network on Chip (NoC) is a new approach to System on a chip (SoC) design. NoC-based systems can accommodate multiple asynchronous clocking as used in many of today's complex SoC designs. The NoC solution brings a networking methodology to on-chip communication and brings notable scalability and performance improvements over conventional bus systems.

The paged design introduced in Section 2 requires an appropriate communication framework to be able to exchange data between pages and off-chip resources. Previously a point-to-point communication scheme based on static wiring between modules was investigated and implemented [16]. The results were not sufficient in terms of scalability and simplifying the process of partial dynamic reconfiguration.

The need for a more general communication method and a general support for partial dynamic reconfiguration were the reasons why the NoC concept was chosen to implement the page-based communication. NoC provides enhanced scalability in comparison with previous communication architectures such as point-to-point and shared bases communications. Further, on one hand it allows the wires in the links of the NoC to be shared, which reduces the demand for wiring resources, and on the other hand it is capable of operating simultaneously on different data packets on independent links, which achieves a high level of parallelism.

The NoC selected in this Thesis is static and so it does not need to be reprogrammed during run time, but it has to to provide a general interface to each communication partner such as each page and off-chip resource, via an interface, as described in the next section.

## 3.1.2 Page/Network Communication Interface

Since the communication infrastructure is defined once at the outset, a general communication interface has to be defined, which is suited to every connection between network nodes and pages as well as off-chip communication port. We want the pages and off-chip communication ports to be partially reconfigurable FPGA areas. To decrease the complexity, the ports could be also predefined and configured once at the beginning.

To delimit the partial reconfiguration area from the network the interface between them has to use a reliable attach/detach mechanism. There are several approaches for realize this. One of the common methods is provided by Xilinx, but this approach is superseded. The *bus macros* from Xilinx are based on tri-state buffers, which are scarce resources in Xilinx FPGAs. Another approach, presented in Section 3.3.3, is proposed by the group GAPH from Catholic University of Rio Grande do Sul, Brasil [20].

The communication interface has to provide support for partial dynamic reconfiguration, where during a partial reconfiguration process the network should not be affected by glitches in the interface between page and network. These glitches may introduce spurious data into the network, causing malfunctions or even circuit blocking. In addition, packets transmitted to an area undergoing reconfiguration, must be discarded, since it is typically impossible to know if these packets are targeted to the previous configuration in this area or to the next one.

Another requirement of the network and interfaces is the ability to scale with future devices and provide the same operational utilization. For this purpose the NoC is supposed to be fully parametrized and provide a high level simulation framework.

Figure 3.1 shows a lower half of the XC4VLX15 Virtex-4 device. The XC4VLX15 Virtex-4 device has overall 8 pages. The figure shows just the lower 4 pages, which are connected to each other using an NoC. The topology of the NoC is a mesh, chosen because of its simplicity and small implementation overhead [22]. The routing algorithm used here is XY Routing, according to which all routers have a unique, fixed address. An XY Routing algorithm requires a strict mesh topology to perform well and in a deterministic, deadlock and starvation free manner [20]. In our case it is required, that intermediate routers are located on the Y-axis to satisfy this requirement. The Figure 3.1 also shows the routers with address 30 and 31, which are connected to the IO blocks. To achieve low area overhead and high performance, the off-chip ports have to be chosen well.

Figure 3.1: NoC mesh layout with intermediate Routers

## 3.1.3 Inter Page Communication

This section introduces some general communication scenarios, imposed by paged-based architecture, which need to be supported by the NoC and which need a deeper investigation to find optimal solution.

The first scenario is page to page communication in which one page communicates with another one and the NoC does not have any congestion on the link between two pages. This is a best case in which the communication is possible with the full bandwidth of the NoC.

If two or more pages want to communicate with one specific page over one link, then congestion occurs in the network, since the link has to be shared between many pages. At this point, the order in which access to the link is provided is determined by an arbiter in a particular NoC router, where one page needs to wait (is blocked) and another can communicate. Since the link is shared and the bandwidth is fixed, the data of both pages needs more time to arrive at its destination. To prioritize one of the pages, the communication infrastructure can provide QoS and give more priority to a specific task.

If a task has a realtime constraint and relies on communication with another component it is very hard to predict the behaviour of the network, except when QoS is implemented and used. It is possible to allocate the page in a cluster with no link sharing and so it is also possible to predict the run time of the communication.

#### 3.1.4 Shared Access to Common Ports

Another scenario is the communication between many pages and one off-chip resource. The resource is accessible through some dedicated I/O pins. This is similar to the scenario above, but the potential communication need is higher. To avoid congestion and blocking of some applications a solution could be increasing throughput to the off-chip resource or choosing a large buffer for critical ports. This decision can be made if the Interface of external resources is known. The goal is to maximize the utilization of the off-chip resources such as memory read and write operations

## 3.2 Constraining the Degrees of Freedom

To assess the main problems, as outlined in the previous sections some simplifications are made to the model and described below.

### 3.2.1 Clock and Clock Regions

The first simplification is the clock speed, which can be set independently for each page region, and ideally the clock speed is allowed to vary for every page region according to the IP. This requires the ability to operate different routers at different clock speeds. In this work it is assumed that page IP operates with the same clock speed as the NoC model and constrains the whole FPGA to operate at one clock speed for the sake of prototyping. The network as well the cores operate with the same clock speed and are limited by the slowest component.

#### **3.2.2** IP-Cores

In this work it is assumed that the page is large enough to fit any core on it, and not constrained to a fix region or timing constrains on the device, which would be needed for a mesh structure. Further, this work uses just cores which provide a built-in blocking mechanism, or does not need such communication type.

## 3.3 HERMES - NoC Infrastructure

HERMES is the name of a NoC infrastructure developed by the group GAPH from Catholic University of Rio Grande do Sul, Brasil [20] and proposed in by Moares et al. in [22]. This section gives a top-down overview of important details of this NoC. Section 3.3.1 gives a role of the HERMES NoC and provided services. The routers and interface implemented in HERMES are

described in detail in Section 3.3.2. Section 3.3.3 presents an adaptation of the interface to support partial dynamic configuration.

### 3.3.1 Network on Chip

HERMES is an infrastructure used to generate NoCs with packet switching, which is adaptable for different topologies, flit sizes, buffer depths and routing algorithms. The HERMES name is also employed to refer to the NoCs implemented with this infrastructure and to the other components of this network, like routers and buffers.

With the HERMES infrastructure it is possible to implement the three lower levels of the ISO OSI Reference Model: (i) physical - corresponding to the definition of the router physical wiring interface; (ii) link - which defines the data transfer protocol between routers (the HERMES infrastructure adopts an explicit handshake protocol for sending and receiving data reliably) (iii) network - corresponding to the level at which the switching mode employed by the NoC is defined.

#### 3.3.2 HERMES Router and Interface

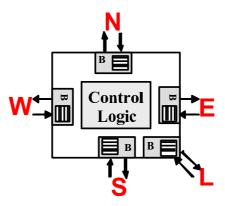

The HERMES infrastructure assumes wormhole packet switching is used. The main component that implements this characteristic is the HERMES router shown in Figure 3.2. This router contains two parts: control logic and a set of up to 5 bidirectional ports: *East*, *West*, *North*, *South* and *Local*. Each port contains a queue to temporarily store packet flits, and whose size is parameterizable at design time. The Local port establishes the commu-

nication path between the processing core and the NoC, and from the local router to any other core in the system. The remaining ports connect routers together. The control logic is composed of two modules: routing and arbitration. The routing module implements one of the algorithms made available by the HERMES infrastructure. The arbitration module determines which packet must receive priority to be switched inside the router when more than one packet arrives simultaneously at the router requiring the same output port. A dynamic arbitration scheme(round-robin) is assumed by the HERMES infrastructure [22].

Figure 3.2: HERMES router architecture. B indicates input buffers

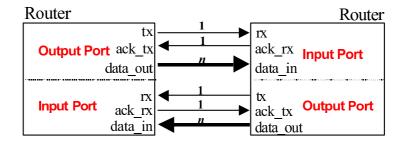

The routing algorithm defines the path taken by a packet between the source and the destination. The deterministic XY routing algorithm is taken. The HERMES NoC follows a mesh topology, justified to facilitate routing, IP cores placement and chip layout generation. The routers use an 8-bit flit size in parallel (bandwidth of the link n=8), and the maximum number of flits in a packet is fixed at  $2^{(flitsizeinbits)}$ . The first and the second flits of a packet are header information, being respectively the address of the target router, named header flit, and the number of flits in the packet payload. An asynchronous handshake protocol is used between neighboring routers. The

physical interface between routers is shown in Figure 3.3 and is composed of the following signals:

- tx: control signal indicating data availability;

- data\_out: data to be sent;

- ack\_tx: control signal indicating successful data reception.

- rx: control signal indicating data availability;

- data\_in: data to be received;

- ack\_rx: control signal indicating successful data reception.

Figure 3.3: Physical interface between routers in HERMES framework

The control logic implements the routing and arbitration algorithms. When a router receives a header flit, arbitration is performed, and if the incoming packet request is granted, an XY routing algorithm is executed to connect the input port data to the correct output port. If the chosen port is busy, the header flit, as well as all subsequent flits of this packet, will be blocked in the input buffers. The routing request for this packet will remain active until a connection is established in some future execution of the procedure in this router. When the XY routing algorithm finds a free output port

to use, the connection between the input port and the output port is established. After routing all flits of the packet the connection is closed. At the operating frequency of 50MHz, with a word size (flit) of 8 bits the theoretical peak throughput of each HERMES router over one link is 1 Gbits/s [22]. This is because a router can establish up to five connections simultaneously (Lin->Eout, Ein->Nout, Nin->Wout, Win->Sou, Sin->Lout, as referred in Figure 3.2).

Arbitration logic is used to grant access to an output port when one or more input ports require a connection at the same time. At the first step round-robin arbitration scheme is used to avoid starvation. Thereafter a prioritized arbitration scheme is implemented, to grant priorities to different packets, depending upon type or source. When a flit is blocked in a given router, the performance of the network is affected, since several flits belonging to the same packet may be blocked in several intermediate routers. To lessen the performance loss, a 4-flit buffer is added to each input router port, reducing the number of routers affected by the blocked flits. Larger buffers can provide enhanced NoC performance. Buffers work as circular FIFOs. The minimal latency in clock cycles to transfer a packet from source to destination is given by:

$$latency (min) = (\sum_{i=1}^{n} R_i) + P * 2$$

where: n is the number of routers in the communication path (source and target included),  $R_i$  is the time required by the routing algorithm at each router (at least 7 clock cycles), and P is the packet size. This number is

multiplied by 2 because each flit requires 2 clock cycles to be sent in case the path is free, due to the handshake protocol.

### 3.3.3 HERMES Interface Adaptation for PDR

NoCs are good choices due to their scalability, increased parallelism and short-range wires that reduce power consumption. This section proposes Artemis, a NoC that supports specific reconfiguration services and is based on the HERMES NoC [22]. This Section describes the modifications carried out in HERMES to allow its use in dynamically reconfigurable systems. Section 3.1 presented the requirements of a partial reconfiguration process. To fulfill these, a set of services is added to the NoC.

Three services are implemented in Artemis: (i) reconfigurable area insulation; (ii) packet discarding; (iii) reconfigurable area reconnection. HERMES added of two functionalities to support these services: (i) definition of control packets, enabling IPs to send packets to routers, not only to other IPs; and (ii) the capacity to disconnect/connect routers to its associated reconfigurable area.

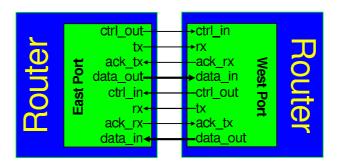

The addition of two sideband signals per port to the original HERMES router serves to differentiate control packets from data packets. These signals, depicted in Figure 3.4, are  $ctrl\_in$  and  $ctrl\_out$ . For each flit sent by  $data\_out$ , the  $ctrl\_out$  is asserted together with tx if the flit is a control packet. The target router receives flits analogously, using  $data\_in$ , rx and  $ctrl\_in$  signals. When the reconfigurable area is insulated, the router discards any data packets sent to the area under reconfiguration. Insulation also protects the network, since during reconfiguration transients can occur in the reconfig-

urable interface. Once the new IP is configured, a control packet reconnects IP and router, enabling normal operation.

Figure 3.4: Interface between Artemis routers

The reception and forwarding of control and data packets is similar. The major change in the router is the addition of one bit at each position of the input buffer. This is required to propagate the value of the *ctrl\_out* signal to the reconfigurable IP router. When the control packet arrives at its destination router, it decodes and executes the corresponding operation.

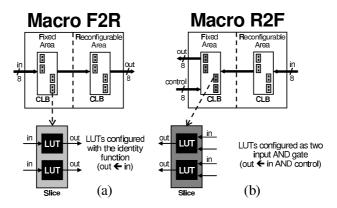

**Figure 3.5:** GAPH macros: (a) Fixed to Reconfigurable area (F2R); (b) Reconfigurable to Fixed area (R2F) [20]

To delimit the static region and the partial reconfiguration region GAPH macros are used, it is a new reconfigurable interface that does not impose the use of a specific communication infrastructure. This interface uses LUTs.

Two unidirectional macros compose the reconfigurable interface, as depicted in Figure 3.5. The first one, named F2R, is responsible to send data from the fixed part of the system to a reconfigurable IP, while the second one, named R2F, implements the communication in the reverse direction. Both macros allow the simultaneous transmission of 8 data bits. The F2R macro is an identity function, while the R2F uses special logic to avoid transient glitches during the reconfiguration process from reconfigurable to fixed areas [20].

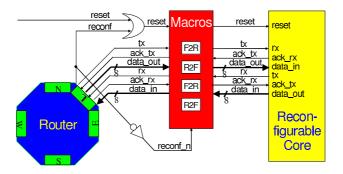

The complete interface between the Artemis router and a reconfigurable IP appears in Figure 3.6. It uses two R2F macros to connect 10 bits from right to left and two F2R macros to connect 11 bits in the opposite direction. The interface between the router and the reconfigurable IP does not contain the *ctrl\_in* and *ctrl\_out* signals because reconfigurable IPs neither send nor receive control packets. The reset is a global signal used to initialize the entire system. The router asserts the *reconf* signal to initialize the reconfigurable core connected to the local port. The *reconf\_n* signal in Figure 3.6 connects to the control signal in Figure 3.4, controlling the connection from the router to the reconfigurable core.

Figure 3.6: Interface between Router and page, supporting partial dynamic reconfigurable. Consists of Bus Macros from Figure 3.5 and control signals

# 3.4 Network Interface cores - Translator between Cores and NoC

This section addresses the network interface core, which has the central role in interpreting signals coming from the NoC to a custom core or page and vice versa. In the literature common names for it are *glue logic*, *adapter* or *wrapper*. This thesis will use the more specific NoC name *Network Interface Adapter* (NWIF). Section 3.4.1 lists all the responsibilities and issues involved in creating a NWIF. A guideline for designing an NWIF is presented in Section 3.4.2, where various aspects which need to be kept in mind are presented and discussed.

#### 3.4.1 Role of the Network Interface