# On Scheduling Dynamic FPGA Reconfigurations

# A Partial Rearrangement Approach

## Oliver Frank Diessel

B.Math., B.E. (Hons)

A thesis submitted in fulfilment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

The Department of

Computer Science and Software Engineering

The University of Newcastle

Callaghan NSW 2308

Australia

January, 1998

# Certificate of Originality

I hereby certify that the work embodied in this thesis is the result of original research and has not been submitted for a higher degree to any other University or Institution.

(Signed) \_\_\_\_\_

Oliver Frank Diessel

# Acknowledgments

It has been an inspiration and a pleasure to be guided in this work by Hossam ElGindy. His vision, enthusiasm, and expertise motivated me as much as I appreciated and benefited from his open warmth and generosity. The foundations for this work were shaped by many enriching discussions with Bryan Beresford–Smith, who also inspired me to start.

I have had a great deal of assistance from the staff, students, and visitors to the Departments of Computer Science and Software Engineering and Electrical and Computer Engineering. In particular, I thank Mathew Wojko and Lachlan Wetherall for reviewing, discussing, and helping me clarify many aspects of this work. Thanks also to Peter Eades, Michael Hannaford, Arun Somani, and the CS&SE technical staff for providing infrastructure support. The financial support of a University of Newcastle Research Scholarship is gratefully acknowledged.

Finally, I would not have begun nor been able to complete this work without the love, support, and encouragement of my family and friends.

# Contents

| A | bstra                                   | act                                       |                                           |  |  |  |  |

|---|-----------------------------------------|-------------------------------------------|-------------------------------------------|--|--|--|--|

| 1 | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Motivation — The Space—Sharing Challenge  |                                           |  |  |  |  |

| 2 | Architectural Models                    |                                           |                                           |  |  |  |  |

|   | 2.1<br>2.2                              |                                           | ce-Shared Multi-Tasking Model             |  |  |  |  |

|   | 2.3                                     | Task l                                    | Management with Partial Rearrangement     |  |  |  |  |

|   | 2.4                                     | Task 1<br>2.4.1<br>2.4.2<br>2.4.3         | Rearrangement                             |  |  |  |  |

| 3 | Par                                     | Partial FPGA Rearrangement 2              |                                           |  |  |  |  |

|   | 3.1                                     | Identii 3.1.1 3.1.2 3.1.3                 | fying Feasible Rearrangements             |  |  |  |  |

|   | 3.2                                     | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5 | uling FPGA Rearrangements                 |  |  |  |  |

|   | 3.3                                     | Evalua 3.3.1 3.3.2 3.3.3                  | ation of Partial Rearrangement Heuristics |  |  |  |  |

|   | 3 4                                     |                                           | usions                                    |  |  |  |  |

| 4                | On-Chip Compaction   |                                   |                                                         |                 |  |  |  |

|------------------|----------------------|-----------------------------------|---------------------------------------------------------|-----------------|--|--|--|

|                  | 4.1                  | Compa                             | acting with Nearest Neighbour Links                     | 59              |  |  |  |

|                  |                      | 4.1.1                             | Scheduling Ordered Compactions                          | 59              |  |  |  |

|                  |                      | 4.1.2                             | Performance Evaluation                                  | 60              |  |  |  |

|                  |                      | 4.1.3                             | Hardware Enhancements                                   | 61              |  |  |  |

|                  | 4.2                  | Compacting with Segmentable Buses |                                                         |                 |  |  |  |

|                  |                      | 4.2.1                             | Notation                                                | 63              |  |  |  |

|                  |                      | 4.2.2                             | Selecting an Optimal Allocation Site                    | 63              |  |  |  |

|                  |                      | 4.2.3                             | Scheduling One-Dimensional Compaction                   | 65              |  |  |  |

|                  |                      | 4.2.4                             | Compacting Unit Length Tasks                            | 70              |  |  |  |

|                  |                      | 4.2.5                             | Compacting Arbitrary Length Tasks                       | 79              |  |  |  |

|                  |                      | 4.2.6                             | Final Remarks                                           | 87              |  |  |  |

|                  | 4.3                  | Conclu                            | isions                                                  | 89              |  |  |  |

| 5                | Experimental Results |                                   |                                                         |                 |  |  |  |

|                  | 5.1                  |                                   | mance of FPGA Rearrangement Scheduling                  | <b>90</b><br>90 |  |  |  |

|                  |                      | 5.1.1                             | One-State Lookahead                                     | 91              |  |  |  |

|                  |                      | 5.1.2                             | Two-State Lookahead                                     | 92              |  |  |  |

|                  |                      | 5.1.3                             | Discussion                                              | 93              |  |  |  |

|                  | 5.2                  | Perfor                            | mance of Off-Chip Rearrangements                        | 94              |  |  |  |

|                  |                      | 5.2.1                             | Overview of Simulator                                   | 94              |  |  |  |

|                  |                      | 5.2.2                             | Overview of Experiments                                 | 96              |  |  |  |

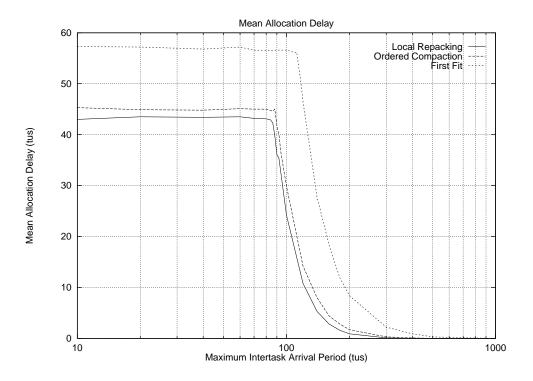

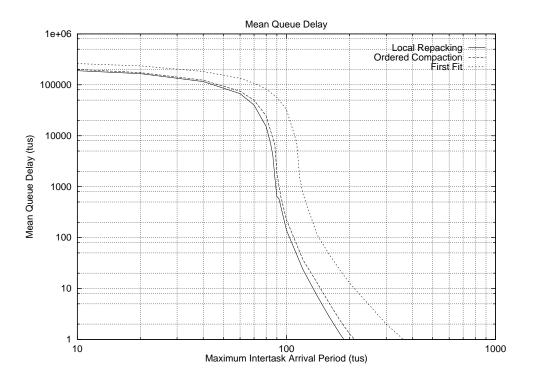

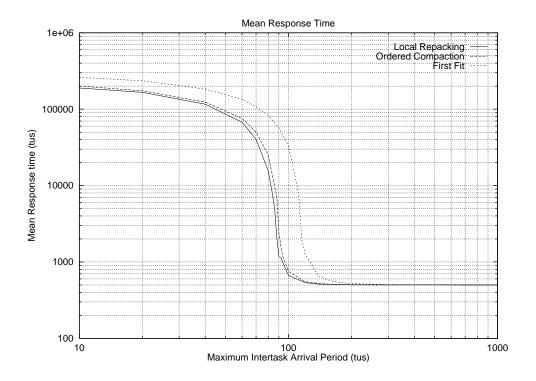

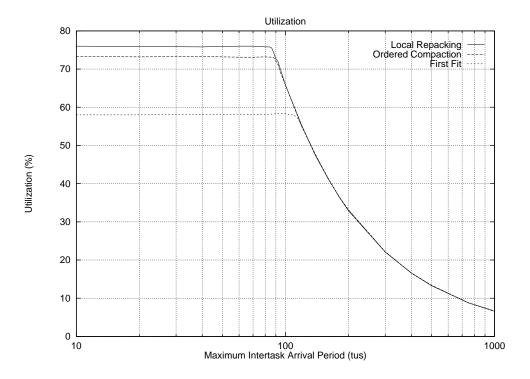

|                  |                      | 5.2.3                             | Effect of System Load on Allocation Performance         | 97              |  |  |  |

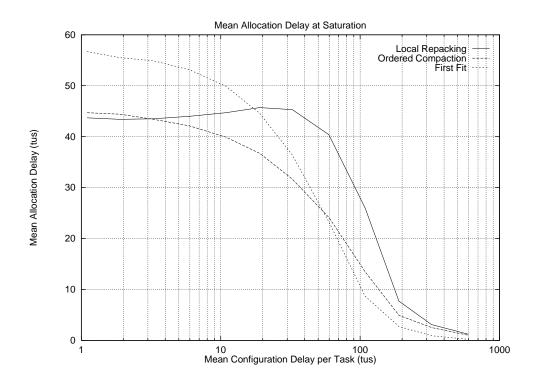

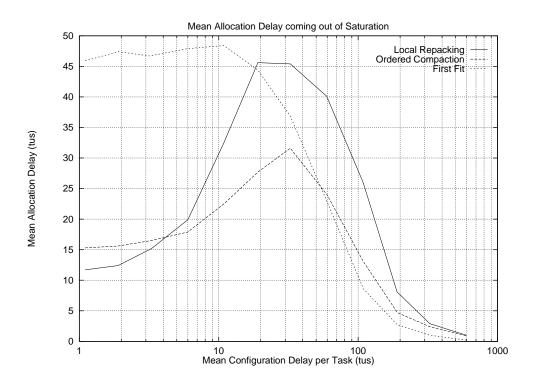

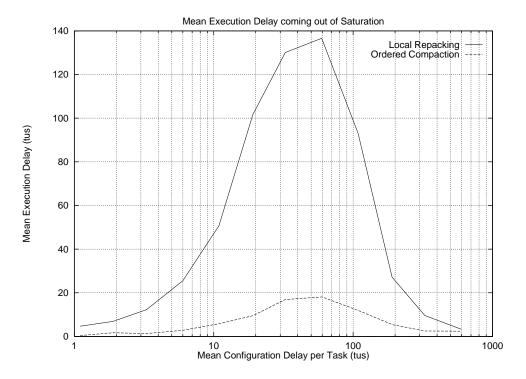

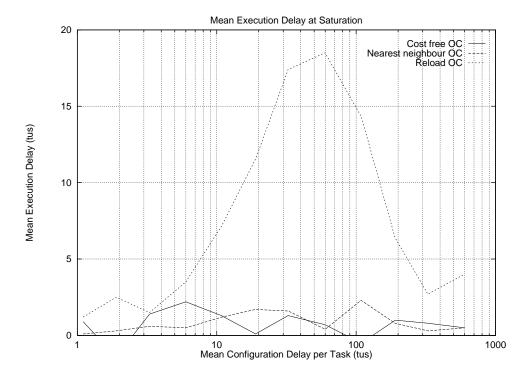

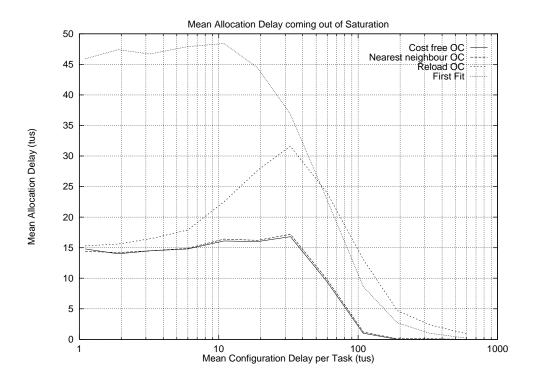

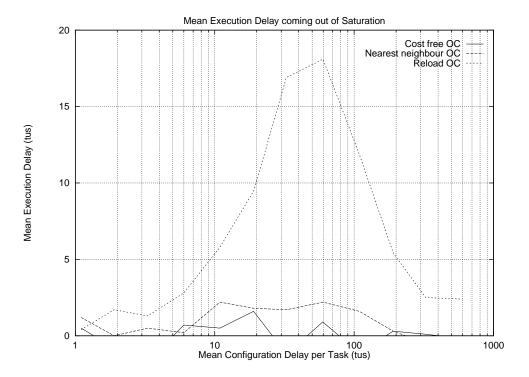

|                  |                      | 5.2.4                             | Effect of Configuration Delay on Allocation Performance | 101             |  |  |  |

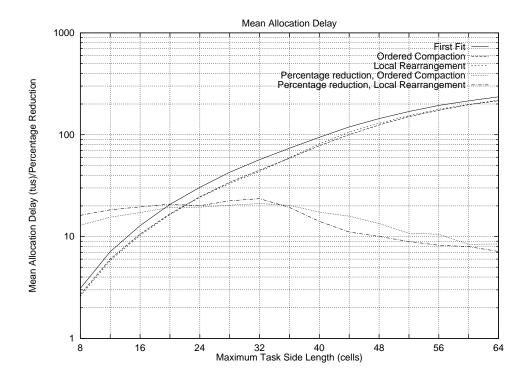

|                  |                      | 5.2.5                             | Effect of Task Size on Allocation Performance           | 103             |  |  |  |

|                  | 5.3                  | Perfor                            | mance of On-Chip Rearrangements                         | 105             |  |  |  |

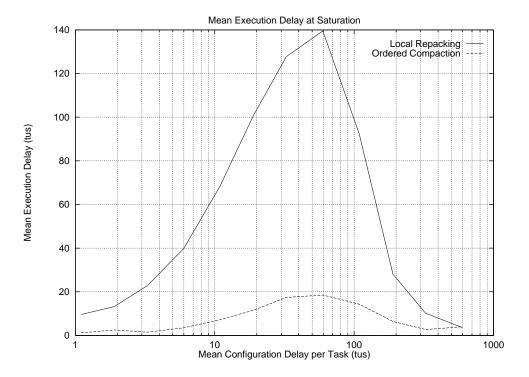

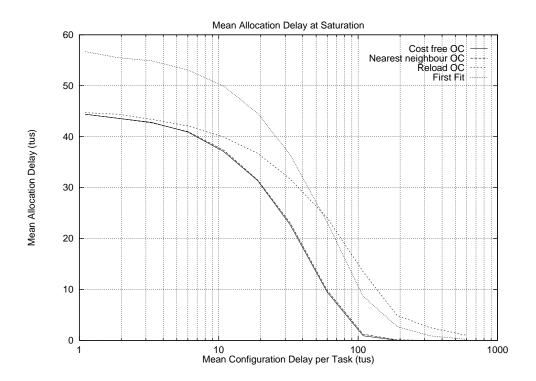

|                  |                      | 5.3.1                             | Effect of Configuration Delay on Allocation Performance | 106             |  |  |  |

|                  | 5.4                  | Compa                             | arison with Previous Methods                            | 109             |  |  |  |

|                  | 5.5                  | Conclu                            | isions                                                  | 110             |  |  |  |

| 6                | Conclusion 11        |                                   |                                                         |                 |  |  |  |

|                  | 6.1                  |                                   | v of the Results and Conclusions                        | 113             |  |  |  |

|                  | 6.2                  | Directions for Further Study      |                                                         |                 |  |  |  |

| Bibliography 117 |                      |                                   |                                                         |                 |  |  |  |

# Abstract

The ability to partially reconfigure dynamically reconfigurable Field-Programmable Gate Arrays (FPGAs) at run-time allows them to be shared among multiple independent tasks. When the sequence of tasks to be performed is known in advance, the FPGA controller can optimize the use of shared resources. However, when the sequence is not predictable, or the task designs are not fixed, the controller needs to make allocation decisions on-line. Since on-line allocation suffers from fragmentation as variously sized tasks arrive and depart, tasks can end up waiting despite there being sufficient, albeit non-contiguous resources available to service them. The time to complete tasks is consequently longer and the utilization of the FPGA is lower than it could be.

This thesis proposes rearranging a subset of the tasks executing on the FPGA when doing so allows the next pending task to be processed sooner. Partial rearrangement proceeds in two steps. The first step identifies a rearrangement of the executing tasks that frees sufficient space for the waiting task, and the second schedules the movement of the tasks so as to minimize the delay in executing them. The scheduling strategies employed depend upon the methods available to move the tasks. Thus the problem of identifying the best rearrangement is linked by feedback through the schedule to the underlying hardware and its capabilities.

Current FPGA architectures allow tasks to be moved by reloading them. Simulation results indicate that significant reductions in allocation delays are possible when the FPGA is saturated with work and the time to load a task is relatively short. However, the reloading tasks face an I/O bottleneck that must be eliminated if partial rearrangements are to be practical for short-lived tasks. Techniques for copying tasks to their destinations over on—chip routing resources are therefore developed. These methods appear to be effective, even when link delays are long, giving hope that they may also be of use in boosting the performance of multiple—SIMD mesh connected computers.

# Chapter 1

# Introduction

This thesis proposes and assesses methods for rearranging a subset of the tasks configured on a Field-Programmable Gate Array (FPGA). The thesis considers moving the tasks by reloading them from off-chip storage and by copying them over on-chip routing resources. This chapter motivates and outlines the work described in the thesis.

The first section of this chapter describes the inspiration for developing space-shared multi-tasking FPGAs. The second section motivates the theme after summarizing the challenges facing the designers of space—shared FPGA systems. The contributions of this thesis and those of earlier investigators are reviewed in the third section. The fourth section then presents an outline of the thesis. The chapter concludes with a statement on related publications.

# 1.1 Historical Developments

Field-Programmable Gate Arrays occupy an increasingly important niche in the price/performance spectrum of computing hardware. At one end of the spectrum, a general purpose processor makes use of the von Neumann model of computation to execute a program by stepping through a sequence of stored instructions. The strength of this model lies in the flexibility of performing different computations by altering the instruction sequence. Unfortunately, the rate at which instructions are executed and the number of bits operated upon by each instruction limit the speed of processing. Specialized architectures and techniques that exploit parallelism are therefore sought when applications require levels of performance that cannot be delivered by sequential processors. For the majority of applications however, they

are perfectly adequate, and large production volumes thus allow manufacturers to market popular processors for relatively low prices.

At the other end of the spectrum, application—specific integrated circuits (ASICs) are designed to compute a particular function, thereby gaining a performance advantage over general purpose processors in a number of ways. First, components such as decoders and multiplexors that are intended to support arbitrary instruction streams but which take time for signals to pass through can be removed from the circuit. Second, by eliminating the need for hardware to fetch, decode, or cache instructions, additional chip area can be allocated to performing computational tasks. Third, instructions that are performed serially at both the bit and word level on the sequential processor can be performed in parallel on the different bits of a word and the different stages of a pipeline. However, once fabricated, ASICs are fixed in function, and their function is limited to the one intended at the design stage. ASICs thus sacrifice flexibility to achieve maximum performance. Moreover, the complexity of designing and testing ASICs leads to long manufacturing lead times and high non—recurring engineering costs. However, for large production volumes, the cost of ASICs can be lower than for general purpose processors.

Current FPGAs, on the other hand, consist of two-dimensional arrays of programmable logic elements and interconnections on a single chip that can be mass-produced and then customized in software to suit specific purposes. The function of the FPGA is programmed by configuring the function of individual logic cells and the interconnections between them. As with ASICs, performance advantages over general purpose processors can be gained by performing instructions in parallel on the bits of a word and the stages of a pipeline. However, as with general purpose processors, supporting flexibility comes at the cost of electrical delays due to configurable components and increased area due to the size of these components and the need to provide sufficient resources to implement circuits of varying complexity. Nevertheless, for small to medium volumes, these costs are offset by significantly lower implementation costs than for ASICs.

Historically, FPGA circuits were configured by programming anti-fuse, UV-EPROM, or EEPROM [53], and were therefore static. The introduction of FPGAs with configuration memory implemented in static RAM allowed the configuration to be modified by altering memory contents during normal operations [31]. However, altering the FPGA function necessitated halting the device and loading a new configuration for the entire chip. Since configuration data had to be loaded

serially, the time needed to reconfigure a circuit was large and depended upon the area of the chip. FPGAs that provide random access to configuration memory were recently introduced to overcome the excessive reconfiguration delay [2, 69]. Such FPGAs are able to reduce reconfiguration delays in two important ways. First, parts of the FPGA not being reconfigured may continue to operate and are therefore not delayed at all. Second, the time to configure a circuit depends upon its size since the configuration bit stream need only load relevant cells.

FPGAs that provide random access to configuration memory while the device is active are known as dynamically or partially reconfigurable. Dynamically reconfigurable FPGAs are used by decomposing the application or FPGA task into a number of mutually time exclusive modules or subtasks that are loaded at run—time as needed [37]. When a module is no longer needed, its resources can be reused by modules that are required but not yet loaded. The range and number of applications reported for dynamically reconfigurable FPGAs is rapidly increasing. Examples of applications so far reported are digital signal processing [54], image processing [28], neural processing [33], video coding [67], simulation [30], string searching [32], and postscript processing [61]. Application areas that may benefit from dynamic reconfiguration include video—on—demand hardware, mobile computing, data encryption, content—based searching, and multiprocessor cache coherence protocols [52]. As more ambitious systems are developed, it is conceivable that it will become possible and desirable for related or even disparate functions to share the one hardware platform.

Partial reconfiguration recycles resources that are not currently used for circuits that are currently needed. A good example of partial reconfiguration is the DISC system, which makes use of a well-defined global context to implement relocatable FPGA tasks of arbitrary size [68]. Tasks that occupy the entire width and an arbitrary number of rows of the FPGA may be located at any row, allowing physical placement of hardware to be determined at run-time. When a new task is to be executed on the FPGA and there is insufficient contiguous space for it, the least recently used tasks are removed from the system to allow for the new task to be placed. The effective area of the FPGA is thus increased by simulating many FPGAs or a much larger FPGA on a small one. While the well-defined global context simplifies DISC task design, it restricts the use of the FPGA to a single task or user at a time so as to prevent tasks from contending for the use of control lines that span the length of the chip. Interest in exploiting partial reconfiguration

to share the FPGA amongst multiple simultaneous tasks and/or users is, however, growing [11, 25, 55].

Switching between configurations to time-share an FPGA among several tasks or users is under investigation for the Garp system [34], which consists of a multi-tasking MIPS processor and an FPGA coprocessor integrated onto a single die. Garp tasks are also prevented from contending for the use of globally spanning control lines by executing one at a time. However, the system supports multiple users by providing instructions to save and restore configurations in array memory when a context switch occurs. The number of multiple users supported in this fashion is limited by the amount of on-chip memory. However, current dynamically reconfigurable FPGAs already use several bytes of valuable space per cell to store configuration and register data, and saving FPGA contexts off-chip becomes infeasible as FPGA sizes grow. A purely time-shared approach to multi-tasking therefore limits the maximum number of users.

While DISC and Garp allow the low-level parallelism inherent in applications to be exploited, much of the FPGA resource may remain idle because tasks are processed sequentially. This inefficiency is exacerbated as FPGA sizes grow. In order to utilize the unused portions of devices and to reduce response times by processing tasks in parallel, future FPGA systems need to support the partitioning of available resources amongst independent tasks that can be processed simultaneously. This technique, known as space—sharing, allows each of the multiple tasks to execute without interruption within its own partition as if it were the sole application executing on an FPGA that is just large enough to support it.

# 1.2 Motivation — The Space-Sharing Challenge

The design and implementation of space—shared FPGAs poses many challenging problems. Multi-tasking systems not only need to support individual users with design tools and monitors, they also need to manage the resources shared by all users. At the lowest operating system level, the sharing amongst several users of logic elements, wires, and input/output (I/O) pins needs to be managed. At a higher level, access to resources needs to be scheduled according to task priorities. Some of the challenging optimization problems that need to be solved to support multiple simultaneous tasks are listed below.

## Hardware support

How should the hardware be made partitionable so that multiple independent tasks can execute? Can multiple simultaneous I/O streams be supported? If so, can multiple tasks be configured and controlled simultaneously? Do multiple clocks need to be supported?

#### Task design

The operating system should be responsible for the choice of task location; a task must therefore be relocatable. How should relocatable tasks be designed so that they do not interfere with neighbouring tasks? What are the global requirements for supporting arbitrary task location?

#### Run-time binding

Since tasks need to be relocatable, there is a need for some run-time binding. Task partitioning, placement, and routing need to adapt according to temporal and spatial constraints. How much preprocessing of the final design can be done? What needs to be done on—the—fly? How can it be done efficiently?

#### Task relocation

In order to maximize utilization and to be fault tolerant, the system also needs to support preemption and to implement garbage collection. How can the overheads of the operating system be minimized? Should operating system functions be implemented as dynamically reconfigurable tasks? If so, how?

Effective solutions to these problems will make space—shared FPGA systems easier to use, more powerful, and more cost effective. These factors in turn will contribute to the attractiveness and more general use of systems employing reconfigurable hardware.

This thesis examines one strategy for boosting performance by defragmenting space—shared FPGAs. Performance loss due to fragmentation comes about as follows. When the sequence of tasks to be performed by an FPGA is known in advance the designer can optimize the use of resources off—line and design an appropriate static controller. However, when the set of tasks to be executed is not closed, the controller needs to make task placement (cell allocation) decisions on—line. The layout of a task is assumed to comprise a contiguous block of logic cells and interconnections that are known before the task is to be configured onto the

array. Thus "allocating" a task is the process of deciding where on the array to place the layout. On—line allocation of contiguous resources is by nature suboptimal. Since users want rapid response, the goal of allocation is to allocate as quickly as possible because task execution times are fixed. However, when the task sequence and/or execution times are not known, it is impossible for the allocator to place a task so as to guarantee minimum impact on subsequent tasks because contiguous allocation schemes suffer from fragmentation as variously sized tasks are allocated and deallocated. Tasks consequently end up waiting in a queue despite there being sufficient, albeit non—contiguous resources available to service them. The response times of tasks are therefore longer and the utilization of FPGA resources is lower than they could be. There is thus a need for a means of minimizing the consequences of fragmentation.

## 1.3 Contributions

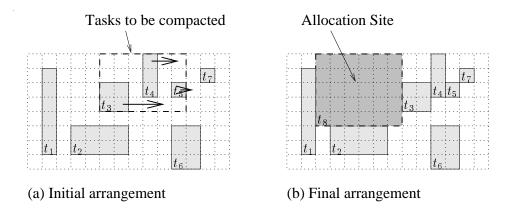

This thesis proposes rearranging, at run—time, a subset of the tasks executing on the FPGA so as to aggregate sufficient contiguous space for the next waiting task when doing so allows it to be allocated sooner. The rearrangement goals are to minimize the delay to the next waiting task, to minimize the delays to executing tasks that have to move, and to minimize the time needed to complete the rearrangement.

A partial rearrangement at run—time involves moving a subset of the tasks executing on the FPGA while the remaining tasks continue to execute. When the task at the head of the pending queue cannot be allocated immediately because of fragmentation, a procedure that attempts to identify a rearrangement of a subset of the currently allocated tasks to accommodate the waiting task is invoked. If such a rearrangement is found, then a schedule for moving the executing tasks that allocates the waiting task as soon as possible and minimizes the delays to executing tasks that are to be moved is computed. The thesis considers three task movement models: moving the tasks by reloading them from off the chip; copying the tasks on—chip over nearest neighbour links; and copying the tasks over segmentable buses. The scheduling methods needed are unique to each model.

The main contributions of this thesis are:

• Two new heuristics for the NP-complete problem of identifying rearrangements of FPGA tasks that will accommodate an additional task. These solu-

tions, respectively known as local repacking and ordered compaction, apply to rectangle packing situations which permit repacking. In particular, they apply to the problem of allocating mesh of processor tasks.

- A proof that it is NP-hard to schedule arbitrary rearrangements of FPGA tasks so as to minimize delays to tasks when they are moved by reloading.

- A depth—first ordered search heuristic for scheduling local repackings by reloading.

- An optimal algorithm for scheduling ordered compactions by reloading.

- An optimal algorithm for the ordered compaction of unit sized one-dimensional tasks over segmentable buses.

- A heuristic for the ordered compaction of arbitrarily long one-dimensional tasks over segmentable buses that bounds the maximum delay to a task.

- An assessment and comparison of the costs and benefits of FPGA task rearrangement methods for varying configuration delays when tasks are reloaded from off-chip and copied on-chip.

The use of task rearrangement to reduce fragmentation was first investigated for multi-stage interconnection networks as part of the PASM project, with efforts directed at modelling and performing the movement of a single task [57, 58]. Several task rearrangement methods that moved some or all of the executing tasks were subsequently proposed for MIMD hypercubes, with efforts directed at devising optimal edge-disjoint migration algorithms (see, for example, [13, 36]). Algorithms for rearranging the tasks on a star graph were described in [40]. The first results for the mesh, which is a natural model for a generic FPGA architecture, were reported by Youn, Yoo, and Shirazi [70]. Youn et al. proposed a complete, parallel task rearrangement method that moved all of the tasks executing on the mesh. They also proposed a sequential method for performing partial rearrangements. Their results suggest that modest performance improvements are possible with the complete method, but that the partial method is not particularly beneficial, especially as communication overheads rise. In contrast to Youn's findings, this thesis indicates that, depending upon the operating conditions, substantial performance benefits are possible with partial rearrangements irrespective of the communication overhead.

There are alternative approaches to overcoming fragmentation which are not discussed in this thesis. They include scaling tasks down or up in size to influence task execution times or to fit them into available blocks, and partitioning the waiting task at run—time into appropriately sized subtasks that can be placed immediately.

## 1.4 Outline

Chapter 2 presents the hardware and operating system models upon which this thesis is based. The chapter first describes the space—shared FPGA and segmentable bus models. Next, it outlines the allocation of tasks with partial rearrangement. Then, it details the three models for moving tasks considered: by reloading, by copying over nearest neighbour links, and by copying over segmentable buses.

Chapter 3 describes two proposals for identifying and scheduling task rearrangements on FPGAs when tasks can only be loaded one after another from off the chip. The chapter begins with a statement of the FPGA task rearrangement problem and the solution goals. It then describes the proposals for identifying partial task rearrangements on conventional FPGAs and describes how optimal allocation sites for the next pending task can be found. After proving the NP-hardness of task rearrangement scheduling, the chapter presents polynomial time scheduling methods for each of the rearrangement identification methods. The chapter compares the time complexity and summarizes the empirical performance of the algorithms before concluding with a description of possible improvements.

Chapter 4 describes the use of nearest neighbour links and segmentable buses to move tasks in parallel on the chip. First of all, a method for performing ordered compactions, described in Chapter 3, using nearest neighbour links to move the tasks is described. The remainder of the chapter then presents and analyzes algorithms for the ordered compaction of unit length and arbitrarily sized one-dimensional FPGA tasks over a segmentable bus. The further development of these methods, including the extension to two dimensions, is considered at the conclusion of the chapter.

Chapter 5 reports on an empirical study into the impact of the proposed methods on simulated FPGAs. To begin with, the effectiveness of the arbitrary task rearrangement scheduling algorithm is examined. Then, the effects of varying the system load, the configuration delay, and the task size distribution when tasks are reloaded are investigated. Finally, the effect of varying the link delay when tasks are

moved over nearest neighbour links is assessed To conclude the chapter, the results are compared with those of Youn et al. for the mesh, and areas for improvement are identified.

Chapter 6 concludes the thesis with a review of the results and their significance as well as a description of the unresolved issues and directions for further study.

# 1.5 Related Publications

Chapters 3 and 5 contain material that has appeared in [20] and [21]. Chapters 4 and 5 contain material reported in [19] and [23]. A summary of the results will appear in [22].

# Chapter 2

# Architectural Models

This chapter describes the hardware platforms and operating system environment for the algorithms in this thesis. First, it describes the partitionable array models considered. Next, it presents the multi-tasking operating environment that supports task rearrangements. Finally, it details the various models investigated for moving tasks.

The space—shared FPGA model is a multi—tasking model in which the programmable resources are partitioned among multiple independent tasks. Ideally, each task executes in its own partition as if it were the sole task executing on an FPGA just large enough for its own needs. Each task is served by its own controller, which has the responsibilities of loading, interrupting, and reconfiguring interdependent subtasks, and of directing the flow of communications to and from the task.

The first section of the chapter presents a high-level model for a partitionable Single Instruction, Multiple Data (SIMD) machine that forms the basis for the hardware architectures discussed in this thesis. Because of its generality, this model is also suitable for describing partitionable FPGAs. Indeed the fundamental similarities between SIMD and FPGA computing models are touched upon in this and the second section, which describes the dynamically reconfigurable FPGA, reconfigurable mesh, and segmentable bus models used in the thesis.

The algorithms of Chapter 3, which use reloading to move tasks, are designed for the dynamically reconfigurable FPGA model. In Chapter 4, two methods for moving tasks on—chip are considered. Since nearest neighbour links are commonly found on current FPGA architectures, the dynamically reconfigurable FPGA model applies when these are used to rearrange the tasks. However, to move tasks over

buses, dynamic switching is needed. Since this is not a feature of currently available FPGAs, a segmentable bus model which incorporates the distinctive features of the reconfigurable mesh is developed.

The third section outlines the multi-tasking operating system environment that allows tasks to be rearranged. The description focuses on the task allocation function with particular emphasis on allocation with task rearrangement but is necessarily high-level so as to remain implementation independent.

Detailed models for moving tasks by reloading them and by copying them over nearest neighbour links and buses are provided in the final section of the chapter.

# 2.1 A Space-Shared Multi-Tasking Model

The Single Instruction, Multiple Data (SIMD) model of parallel computation is characterized by a large number of simple compute processors all executing, at the same time, the same instruction, which is broadcast by a centralized control processor. The model achieves high performance through massive data parallelism.

Of the many network topologies that have been investigated, the SIMD array has gained supremacy, not just for its design simplicity, but also because many real world problems naturally map to it. Indeed, the first parallel machine built, the ILLIAC IV [6], was a SIMD mesh. Like ILLIAC, the MPP [8] was a bit—slice mesh, and the MasPar MP-1 [49], a word—width processor array, achieved commercial success.

As early as 1968 [6], designers of massively parallel computers recognized that effective use of the processing elements in such machines can be achieved through the ability to partition a large—scale multiprocessor into independent SIMD subsystems. The ILLIAC IV supported partitioning at the processor and array level. The 64 bit—wide processing elements were able to be split into two 32 bit—wide or eight 8 bit—wide elements, and the array could be split into two or four independently controlled, equally sized machines. The Connection Machine [66] was also partitionable into one, two, or four machines of equal size, each of them controlled by its own front end processor. However, this coarse type of partitioning is static and limiting.

The partitionable multiple—SIMD model, first proposed by Nutt in 1977 [50], allows for the set of compute processors to be shared by multiple control units. Systems adhering to this model make effective use of the compute processors by

adjusting the sizes of processor partitions to the sizes of the tasks, thereby allowing several tasks to be executed in parallel. Possible implementations were subsequently investigated by the MOPAC [41], PASM [60], and GPA [12] projects.

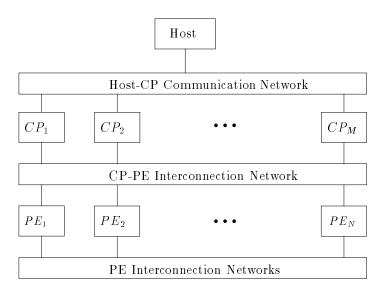

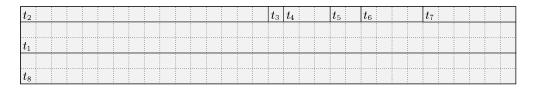

An overview of this model is illustrated in Figure 2.1. The compute resource consists of N interconnected processing elements (PEs) that are controlled by a set of M control processors (CPs). The CPs in turn are under the global control of a host. The host orchestrates the operation of the CPs, each of which broadcasts instructions for the PEs under its control over the CP-PE interconnection network. It is assumed that partitions involve non-overlapping sets of consecutive or contiguous processors and behave like a dedicated machine of the corresponding size [59].

Figure 2.1: Nutt's multi-SIMD model of parallel computation.

# 2.2 Compute Resource Models

## 2.2.1 Dynamically Reconfigurable FPGA Model

Bolotski, DeHon and Knight describe a model of computational arrays that unifies SIMD arrays and FPGAs [10]. Their model consists of a grid of array elements with interconnection resources linking array elements together. Each array element performs a simple function on some state and some inputs from the array and either updates its own state to record the result of its computation or shares the results with other elements in the array. An instruction specifies the computation performed

by each array element. The instruction is also used to specify communications and state manipulation. In their model, the transform from input values to outputs is modelled as a look up table addressed by the input value. The instruction is modelled as either the programming of the look up table or as additional inputs. Ideally, each array element should be able to perform a different instruction each cycle. However, the instruction bandwidth that would be needed for reasonably sized arrays would be too large. Both FPGAs and SIMD therefore weaken the model. While SIMD arrays compromise in the spatial variation of instructions to allow a high rate of instruction dispatch, FPGAs compromise in the rate of instruction dispatch to allow the instructions to vary spatially through the array. FPGAs achieve high performance by pipelining data through multiple stages, each of them performing different logic functions simultaneously.

In broad terms, an FPGA task is a sequential or combinational circuit that is laid out in space rather than time. The logic functions of an FPGA circuit are performed by configurable logic cells that are interconnected through wires and programmable routing switches. A "program" not only instructs the cells which functions to perform but also determines how they are to be interconnected by setting the routing switches. The circuit is configured before the data arrives and remains configured until a new configuration is loaded.

The cells of common dynamically reconfigurable FPGAs [2, 69] are laid out in a two-dimensional grid and are usually directly connected with their neighbours to the north, south, east, and west via nearest neighbour links. In addition, FPGAs usually incorporate some network of bus segments for fast communications over longer distances. Routing switches are used to connect cells to bus segments and to interconnect bus segments for turns or longer paths.

**Definition 1** A space-shared FPGA of width W and height H is a two-dimensional grid of configurable cells and routing resources denoted  $G^2[(1,1),(W,H)]$  with bottom-left cell labelled (1,1) and top-right cell labelled (W,H).

Current FPGA cells typically consist of no more than a few logic gates, or a small look up table, a flip—flop, and some multiplexors for configuring the cell function. Cells typically operate on two or four bits of input and produce a single output bit. The output of the cell is a boolean combination of the inputs, flip—flop contents, and constants.

Configuration involves loading the look up table and/or memory selectors for the multiplexors associated with each cell to select the cell's function. Several bytes of configuration data per cell are serially loaded as a configuration bit—stream via pins on the periphery of the chip. The configuration of the routing switches is also determined by the program.

With current technology, the time to configure a cell is an order of magnitude greater than the signal delay through it or along a wire. The signal delay along interconnections composed of several bus segments is approximately linear in the number of switches along the path from the source cell to the destination cell [39].

It is assumed that an FPGA task and the used routing resources surrounding its perimeter can be modelled as a rectangular subarray of arbitrary yet specified dimensions. Some internal fragmentation therefore results when task designs cannot be optimized to a rectangular shape. The size of a task is assumed fixed for the duration of its execution.

**Definition 2** The FPGA task  $t[l_1, l_2]$  with  $l_1, l_2 \in Z^+$  requires an array of size  $l_1 \times l_2$  to execute.

Tasks are assumed to be independent. However, when a task is decomposed into several reconfigurable subtasks, they are allocated to the largest bounding box required throughout the task's instantiation. In this way, routing conflicts and interference with other tasks are avoided.

Tasks are assumed to be deadline—free and to have unknown service periods. However, it is possible to check whether or not tasks for which service periods are known can be rearranged without exceeding deadlines.

No limit is placed upon the number of tasks that can execute simultaneously. To support multi-tasking, the FPGA should be able to support multiple simultaneous I/O streams. The idealized model considered in this thesis assumes any number of I/O streams can be supported without slowdown. The relatively small and fixed number of I/O pins on FPGA packaging necessitates the use of time multiplexing for I/O. Techniques for doing so are being investigated by MIT's virtual wires project [3].

Each task is allocated a subarray of the required size within a larger partitionable array. Usually a subarray will simply be referred to as an array as well.

**Definition 3** The orientation or(t) = (x, y) of a task t specifies the number of cell

columns x and rows y allocated to the task from the array. Given the orientation of a task, its width w(or(t)) = x and height h(or(t)) = y are known.

Tasks may be rotated and relocated. Task  $t[l_1, l_2]$  may be oriented such that  $or(t) = (l_1, l_2)$  or such that  $or(t) = (l_2, l_1)$ . If  $or(t) = (l_1, l_2)$ , then it may be allocated to any array  $G^2[(x, y), (x + l_1 - 1, y + l_2 - 1)]$  where  $1 \le x \le W - l_1 + 1$  and  $1 \le y \le H - l_2 + 1$ . If tasks make use of hierarchical routing networks, then they might not in practice be relocated anywhere. The FPGA abstraction assumes the routing interface to all cells is identical.

The dynamically reconfigurable FPGA model assumes the I/O architecture permits random access to the configuration memory of a single logic cell or routing switch in a single step. Moreover, it is assumed that a cell or switch can be configured in a constant amount of time.

It is assumed that the time needed to configure a subarray

$$t_{\text{conf}}(G^2[(x_1, y_1), (x_2, y_2)]) = CD \times (x_2 - x_1 + 1)(y_2 - y_1 + 1)$$

(2.1)

is proportional to the configuration delay per cell CD and the size of the subarray since, at worst, cells are configured sequentially. Since the delay properties of commercially available chips are isotropic and homogeneous, CD is assumed to be constant, i.e., the time needed to configure a task and route I/O to it is independent of the task's location and orientation.

The logic cells are assumed to have storage for a single task context. Configuration memory contents are assumed to be overwritten when a cell is configured.

#### 2.2.2 Reconfigurable Mesh Model

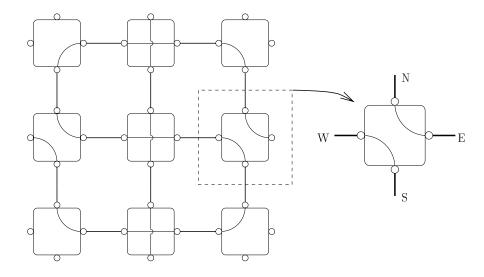

The reconfigurable mesh [1, 38, 47] is a more traditional SIMD model of computation that is also based on a two-dimensional grid of processors architecture (see Figure 2.2).

The model is distinguished by its reconfigurable bus system. Internal to each processing node is a set of locally controlled short circuit switches that allow the interprocessor wires to be connected together to form a communications bus. A different connection configuration can be established during each machine cycle, and all processors participating in a bus configuration have access to the data available on it. The model is said to display connection autonomy because the connection configuration of a PE can be set according to local state information. The 15 possible connection configurations are depicted in Figure 2.3.

Figure 2.2: A reconfigurable mesh of size  $3 \times 3$ .

Figure 2.3: Reconfigurable mesh connection configurations.

Reconfigurable mesh processors operate synchronously, in one machine cycle setting a connection configuration, sending (receiving) a datum to (from) each I/O port, and performing an arithmetic, logic or control operation. When a connection is set, signals received by a port are simultaneously available to any port connected to it. For example, if processors connect their northern and southern I/O ports by closing the appropriate switches as in the configuration (NS,E,W), data "broadcast" onto the "column buses" so formed can be read by all of the processors in a column. The model allows concurrent reading from a bus but requires exclusive writing to the bus. If in a single cycle multiple broadcasts are to be made over multiple buses, those buses are required to be disjoint. The model usually assumes the delay along a bus is a constant independent of length. For buses of bounded length this assumption is reasonable. Techniques for coping with buses of unconstrained length have also been proposed [9, 24].

## 2.2.3 Segmentable Bus Model

The segmentable bus model used in this thesis adopts the central assumptions of the reconfigurable mesh model while simplifying the hardware considerably. The model makes use of the ability to establish a new bus configuration each cycle and to communicate in one cycle irrespective of distance. The former is not difficult to implement, and the adoption of the latter is motivated by the assumption that the buses formed will not branch and will span the width of the FPGA chip at most. For a review of the computational power of this model see [65].

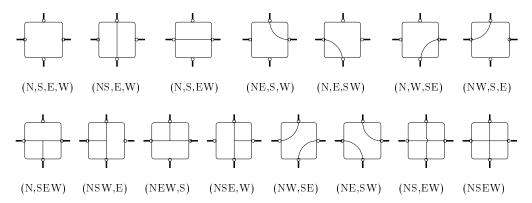

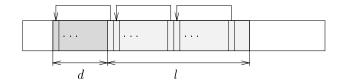

In Chapter 4, a hybrid model comprising a linear array of FPGA cells as the compute resource and a linear array of switching elements for the configurable interconnect is used to investigate the complexity and power of using segmentable buses to rearrange tasks. See Figure 2.4.

Linear array of dynamic switching elements

Linear array of logic cells

Figure 2.4: The segmentable bus FPGA model.

The one-dimensional grid or linear array of L cells  $G^1[1,L]$  is labelled  $C_1, \ldots, C_L$  from left to right. Each cell  $C_i$  is connected to a bus segment of unit length labelled  $B_i$  directly to its north. Between each pair of consecutive bus segments  $B_i$  and  $B_{i+1}$  there is a short circuit switch labelled  $S_i$  which can be opened or closed at the commencement of each communication cycle or step.

Cells  $C_i$  and  $C_j$  with i < j communicate in a single cycle in the following manner:

- 1. Switches  $S_{i-1}$  and  $S_j$  open, and switches  $S_i, S_{i+1}, \ldots, S_{j-1}$  close, and

- 2.  $C_i$  and  $C_j$  communicate via their northern ports and the bus formed between them.

Opening the switches  $S_{i-1}$  and  $S_j$  isolates the bus spanning cells  $C_i$  and  $C_j$  from the rest of the bus system, thereby allowing additional buses to be formed to the left of  $S_{i-1}$  and to the right of  $S_j$  in the same cycle.

Setting a bus configuration and transferring a cell's contents is assumed to take a single step irrespective of transfer distance. The length of a step is therefore normalized to the longest period needed to establish the switch settings and propagate a cell's contents across the width of the FPGA at most.

Logic cells are assumed to have storage for two task contexts between which they can switch in a single step. Storage for the cell configuration and state that is switched out of context may be accessed from the bus segment attached to the cell while the cell executes a second task context.

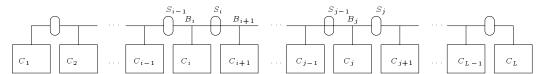

## 2.3 Task Management with Partial Rearrangement

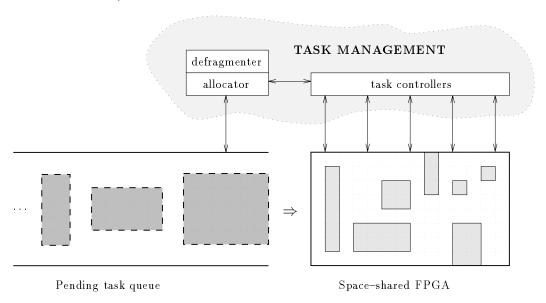

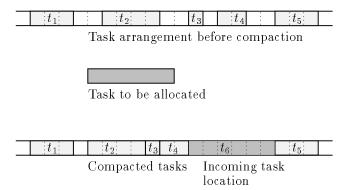

Overall management of tasks is accomplished in the following way. Refer to Figure 2.5 for an overview. Note that the model applies equally well to one-dimensional arrays.

Figure 2.5: An overview of task management with partial rearrangement.

Requests for service are queued in arrival order by a sequential host. A task allocator, executing on the host, attempts to find an allocation site to satisfy the next pending request when it arrives. If the allocator succeeds in finding a suitable site, it associates a controller with the new task and its partition and allows the controller to assume responsibility for loading the task and establishing I/O to it.

When the allocator fails to find a suitable allocation site for the next pending request, it invokes a defragmenter, which determines whether or not the request

can be satisfied with partial rearrangement. If allocation with rearrangement is possible, the defragmenter performs the rearrangement and returns the allocation site thereby created to satisfy the request. If on the other hand allocation with rearrangement is not possible, then all requests are blocked until allocation is attempted once more.

Subsequent allocation attempts are made whenever a task completes and there is a request for service pending. If some executing tasks can be rearranged to accommodate the task, then a schedule for suspending and moving them is computed. The defragmenter then coordinates the partial reconfiguration of the FPGA by signalling individual task controllers to suspend a task's operation, save the task's context, move the task and its context to a new location, and to resume the task's operation.

For the sake of fairness and simplicity, requests for service are processed in first-come first-served (FCFS) order. However, the methods discussed in this thesis do not depend upon the scheduling method. Non-FCFS methods with better performance, such as back-filling [44], could therefore be used.

The task allocator uses bottom-left allocation, which is a first fit method [71]. The bottom-leftmost free block large enough to satisfy the request is allocated to the task. The advantages of the first fit method are that it is simple and that it has complete recognition capability, i.e., it recognizes all possible allocation sites. Many other contiguous allocation schemes have been proposed. For example, the two-dimensional buddy method [43] and frame-sliding [14] are more efficient than first fit, as originally proposed, but they suffer from high fragmentation, and have incomplete recognition capability. The busy-list method [18] is efficient, and it attempts to reduce fragmentation by using a best-fit approach. However, it is considerably more complicated to implement. It should be noted that partial rearrangement can be successfully used with any allocation method.

**Definition** 4 Let  $T = \{t_i[l_{1,i}, l_{2,i}] : 1 \leq i \leq n\}$  be a set of tasks allocated to an FPGA  $G^2[(1,1),(W,H)]$ . The arrangement of tasks  $A(G^2[(1,1),(W,H)]) = \{a(t_i) : t_i \in T\}$  is the set of non-overlapping orthogonally aligned rectangular allocations  $a(t_i) = G^2[\mathrm{bl}(t_i), \mathrm{tr}(t_i)]$  in the array  $G^2[(1,1),(W,H)]$ . The allocation for task  $t_i$  is said to be based at the cell allocated to the bottom-left corner of the task  $(x(\mathrm{bl}(t_i)), y(\mathrm{bl}(t_i)))$  and to extend to the cell allocated to the top-right corner of the task  $(x(\mathrm{tr}(t_i)), y(\mathrm{tr}(t_i)))$ .

# 2.4 Task Rearrangement

Rearranging the tasks executing on an FPGA requires moving them. Moving a task involves: suspending input to the task and waiting for the results of the last input to appear or waiting for the task to reach a checkpoint; storing register states if necessary; reconfiguring the portion of the FPGA at the task's destination; loading stored register states if necessary; and resuming the supply of input to the task for execution. The problem of rerouting I/O to a task that is moved is not addressed in this thesis.

Since tasks are assumed to be without deadlines, any task is considered preemptable and may therefore be suspended with its inputs being buffered and necessary internal states being latched until the task is resumed. The time needed to wait for the results of an input to appear or for the task to reach a checkpoint is considered to be proportional to the size of the task which in the absence of feedback circuits is the worst case. However, since with current technology the time to configure a cell and associated routing resources is typically an order of magnitude greater than the signal delay of a cell or the latency of a wire, the latency of the design is considered negligible compared with the time needed to configure the task.

A task cannot be moved without some cost. The approach in this thesis is to distinguish between the minimum possible cost of moving a task and the actual cost of moving it. The minimum cost is the time needed to suspend, move and resume the task, which is unavoidable. However, the actual cost needs to account for the time a task is suspended while other tasks are being moved. The difference between the actual and minimum costs represents a scheduling delay that is to be minimized for all tasks.

#### 2.4.1 Moving Tasks by Reloading

In Chapter 3, the effectiveness of reconfiguring the destination region of a task by reloading the configuration stream with a new offset is investigated. This approach naturally re–incurs the cost of configuring the task, given above in Equation 2.1, but is applicable to any dynamically reconfigurable device.

Moving tasks by reloading them is inherently sequential. Tasks are reloaded one after another, cell by cell. In Chapter 4, techniques for using on-chip resources to overcome this bottleneck are developed. It should also be noted that if I/O to tasks is performed using direct addressing, then tasks not being moved may be

delayed by the configuration stream of tasks being moved.

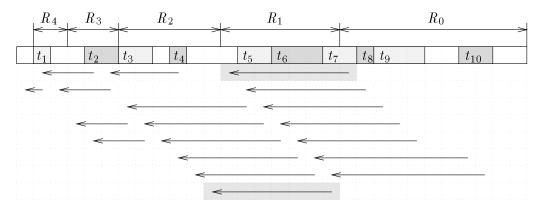

## 2.4.2 Moving Tasks over Nearest Neighbour Links

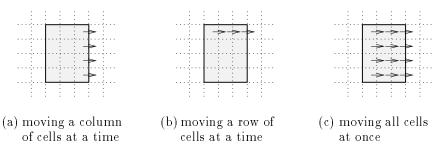

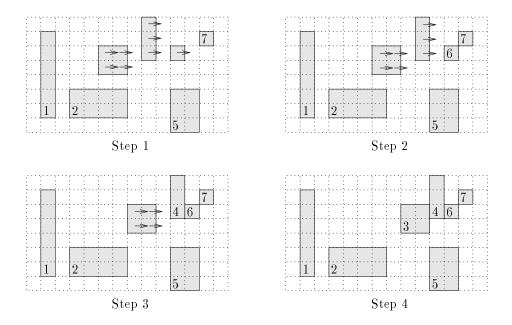

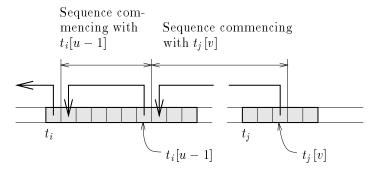

The time required to move a task over the links connecting neighbouring cells is significantly less than that required to reload it. Assume a task is to be moved d cells to the right along the rows of the FPGA and that there are no tasks in its way to impede its movement. See Figure 2.6 for an illustration.

**Definition 5** The configuration bits for a cell and the cell's state are collectively referred to as a task element.

All task elements in the rightmost column of task cells can be moved simultaneously by writing them onto port E and having them read by the neighbouring cells from port W. Moreover, the task elements in each row of task cells can be moved simultaneously as well by having all cells write their task element to port E, and having all cells that are to receive a task element read it from port W. The task elements of each row are said to be pipelined to the right. The task can thus be moved one column of cells to the right in each move cycle, and d cycles in total are needed to move the task to its destination.

Figure 2.6: Moving a task over nearest neighbour links.

To move a task it must be halted. Cells then repeatedly send their task elements to their neighbours until the task reaches its destination. All task elements reach their destination in the same cycle. Once the task reaches its destination it is resumed again.

The time to move a task is proportional to the distance the task has to move. The actual time spent moving depends upon the time needed to transfer a task element to the neighbouring cell, which depends upon the amount of configuration and state information that needs to be transferred, as well as the bandwidth of the link. Current FPGAs allow configuration bits to be loaded one byte or word

at a time while their nearest neighbour links are usually one bit wide. However, transferring configuration data over a nearest neighbour link may be faster than loading it from off—chip because absolute addresses may not need to be decoded and wire lengths are shorter. The time spent moving a task also needs to take into account the time required to halt and resume the task. This task or design latency is considered negligible compared with the time needed to load the task. Assuming tasks are not moved too often, this cost can therefore be ignored.

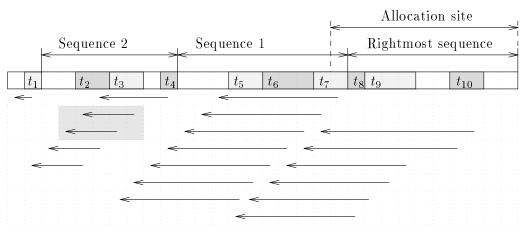

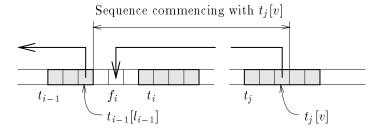

## 2.4.3 Moving Tasks over a Segmentable Bus

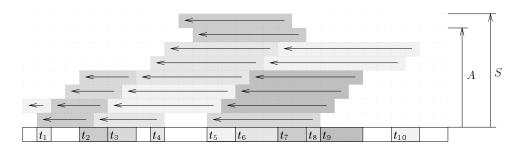

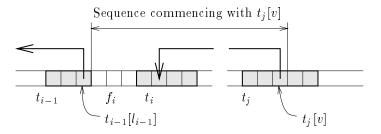

Moving a linear array task over a segmentable bus involves switching the task out of context and configuring the buses needed to move the task elements over a sequence of steps. During each step, the source (destination) cells of a move then write (read) their task elements to (from) the bus segments to which they are connected. When all the elements of a task have reached their destination, the task is switched back into context and task execution is resumed.

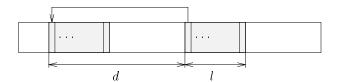

#### Case l < d:

## Case l > d:

Figure 2.7: Moving a linear array task over a segmentable bus.

The time required to move the task is derived in the following lemma.

**Lemma 1** A one-dimensional task of length l can be moved d cells to the left in  $\Theta(\min(l,d))$  steps over a segmentable bus. This is optimal.

**Proof:** Refer to Figure 2.7. When  $l \leq d$ , all task elements must be moved over and past the bus segment connected to the leftmost cell occupied by the task. Since

the buses used to move task elements are required to be disjoint, at most one task element can be moved per cycle or step. At least l steps are therefore required to move the task. Moving them one at a time achieves the lower bound.

When l > d, d task elements need to be moved to the left of the leftmost cell occupied by the task. The need to form disjoint buses implies d steps are needed for these movements. Furthermore, the cell initially occupied by the leftmost task element cannot be the destination of a task element move during one of these cycles. Therefore d+1 steps at least are required to complete the task move. To complete the move in a minimum number of steps, task elements whose index mod (d+1) is equal to i are moved in parallel during step i. This movement maximizes the use of the segmentable bus and is therefore optimal.  $\blacksquare$

# Chapter 3

# Partial FPGA Rearrangement

This chapter proposes and evaluates methods by which feasible rearrangements can be identified and scheduled when tasks are moved by reloading them from off-chip memory.

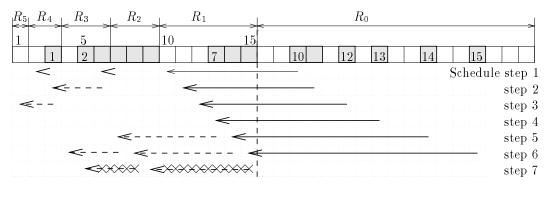

The purpose of partial FPGA rearrangement is to allocate waiting tasks as quickly as possible so as to reduce task response time. This benefit to the waiting task does not come without some cost to the executing tasks since they must be interrupted in order to be moved. It is therefore desirable to delay as few executing tasks as possible and to minimize the maximum amount any single task is delayed—the net effect of the delays to executing tasks should not outweigh the net benefit to the waiting tasks. The current FPGA model, described in Chapter 2, moves tasks by reloading their configuration bit streams with new offsets. This approach limits the time needed to complete the rearrangement since the time to move a task is assumed to be proportional to its area, and the tasks that need to be moved must be reloaded one after another. The time to complete a rearrangement is therefore proportional to the total area of the tasks moved. Since the rate at which tasks can be allocated is limited by the rate at which allocations can be found or rearrangements can be performed, it is desirable to complete rearrangements as quickly as possible. These factors contribute to the formulation of the FPGA rearrangement problem as follows.

#### FPGA REARRANGEMENT PROBLEM

INPUT: A set of executing tasks  $T = \{t_1, \ldots, t_n\}$ , an arrangement  $A(G^2[(1, 1), (W, H)]) = \{a(t_i) : t_i \in T\}$  of the executing tasks, and a waiting task  $t_{n+1}[l_{1,n+1}, l_{2,n+1}]$  that cannot be allocated to the array without overlapping the allocation of some other task in T.

OUTPUT: A new arrangement  $A'(G^2[(1,1),(W,H)]) = \{a'(t_i) : 1 \le i \le n+1\}$  of

the tasks, if possible, and a schedule  $p: T \to Z_0^+$  for moving the tasks in  $\{t_i : a(t_i) \neq a'(t_i)\}$  such that:

- 1. the allocation for  $t_{n+1}$  is freed of executing tasks in minimum time,

- 2. the maximum delay to executing tasks that must be moved is minimized, and

- 3. the time needed to complete the rearrangement is minimized.

The statement of the problem suggests two subproblems are to be solved. First, a new arrangement of the executing tasks that accommodates the unallocated or waiting task is needed. Second, a schedule for moving the tasks from their initial to their final allocations is to be found. The work involved in solving these problems represents an overhead to the system. An additional requirement therefore, is to find efficient solutions.

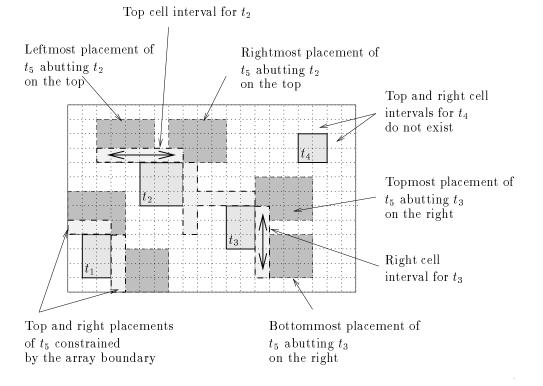

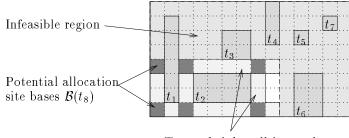

In Section 3.1 it is shown that the problem of identifying a rearrangement of the executing tasks that accommodates the waiting task is NP-complete. A reasonably quick approximate approach to finding suitable or feasible rearrangements is therefore needed. Two heuristic solutions are presented in this chapter. The first is based on the idea of repacking the tasks in a suitable local area of the array using a two-dimensional strip-packing algorithm. Local area candidates are identified by means of a quadtree decomposition of the free cells. Since strip-packing algorithms are approximation algorithms, some feasible local areas remain unidentifiable by this method. The second method constrains the range of task movements and thus the number of initial arrangements that can be successfully rearranged. This second method identifies all possible sites for the waiting task that moves a subset of the executing tasks closer together in one direction.

Each feasible rearrangement must be evaluated for the time needed to free the allocation site, for the time needed to complete the rearrangement, and for the maximum delay to moving tasks. The problem of identifying the best rearrangement is thus linked by feedback to the problem of scheduling the rearrangement of the tasks. While the geometric problem of identifying possible rearrangements of the tasks is independent of the hardware model, the choice of optimal rearrangement varies according to the different scheduling techniques and outcomes possible with different technologies. In this chapter, task movements are constrained to be performed sequentially by reloading tasks from off the chip. In Section 3.2, scheduling the rearrangement of tasks on the FPGA so as to minimize the delays to the waiting and moving tasks is shown to be NP-complete. A greedy heuristic that minimizes the increase in delay to tasks with each sequencing choice is thus developed. The time complexity and performance of this heuristic depends upon the depth to which the state—space is explored before making a choice. Methods for on-chip task movements and their effect on rearrangement scheduling are examined in the next chapter.

Section 3.3 presents a comparison of the time complexity of partial rearrangement heuristics and summarizes the results of the experimental investigation of allocation performance reported on in Chapter 5.

This chapter concludes with a chapter summary and avenues for improvement in Section 3.4.

# 3.1 Identifying Feasible Rearrangements

A feasible rearrangement of the executing tasks is a new arrangement of the executing tasks that allows the waiting task to be allocated as well. Although it is assumed that tasks may be rotated before allocation, the rearrangements considered in this thesis do not rotate the executing tasks.

In this section, it is first shown that the problem of identifying feasible rearrangements is NP-complete. Two heuristics are subsequently presented to overcome this intractability. Local repacking hierarchically decomposes and assesses the array for suitable subarrays of tasks that, when repacked using known methods, may accommodate the next waiting task. This method may translate tasks in several directions. Ordered compaction, on the other hand, makes use of a novel scanning procedure to identify subsets of tasks that can be squeezed together in one direction to make room for the waiting task.

## 3.1.1 Identifying Feasible Rearrangements is NP-Complete

In [42], Li and Cheng show that it is NP-complete to decide the RECT-ANGLE PACKABILITY problem, which is to determine whether or not a set of oriented rectangles can be orthogonally packed without overlap into a larger containing rectangle. Their proof was by reduction from the PARTITION problem [29]: the sizes of the elements of a given PARTITION instance determine the widths of corresponding rectangles having height 1/4. These can be packed into an ar-

ray of width one half the total size of the PARTITION elements and height 1/2 in polynomial time if and only if P = NP. The following theorem thus follows.

**Theorem 1** ([42]) RECTANGLE PACKABILITY is NP-complete.

Corollary 1 REARRANGEMENT FEASIBILITY, the problem of deciding whether a set of executing tasks can be feasibly rearranged to accommodate the next waiting task is NP-complete.

**Proof:** By equivalence with RECTANGLE PACKABILITY. A procedure for deciding RECTANGLE PACKABILITY can decide whether or not the set of executing tasks taken together with the next waiting task can be packed into the array. Similarly, an algorithm for deciding REARRANGEMENT FEASIBILITY can be used iteratively to determine RECTANGLE PACKABILITY. The problems are therefore computationally equivalent. ■

Since the problem of deciding REARRANGEMENT FEASIBILITY is NP-complete, it is unlikely to have a polynomial time solution. The corresponding optimization problem, that of finding a feasible rearrangement, is therefore also unlikely to be easy. Consequently, heuristic solutions are sought. The remainder of this section presents two such solutions.

#### 3.1.2 Local Repacking

The idea behind local area repacking is to repack the tasks initially allocated to some rectangular region of the array so as to accommodate the waiting task within the subarray as well. A hierarchical decomposition of the array known as a free area tree is used to keep track of the number of free cells within each subarray. In so doing, regions that contain sufficient free area to accommodate the waiting task can be quickly identified, and rearrangements of the tasks they contain can be attempted. Two—dimensional bin packing algorithms with good performance bounds are used for this last step: the tasks, viewed as rectangles, are packed from scratch into an infinitely long strip whose width is determined by the length of one side of the subarray. If the tasks are packed using total height less than the length of the other side of the subarray, then the rearrangement is feasible, and its cost is then assessed.

Following a definition of a free area tree and a description of its use, algorithms for constructing and searching it are presented. The subsection concludes

with a brief review of known strip—packing algorithms available for use by the method.

## 3.1.2.1 Free Area Trees

A free area tree is a type of quadtree [56, 72] that need not necessarily be defined over a square grid and whose leaves may have just one rather than three siblings. Each node of the tree, which represents a portion of the array, stores the number of free cells contained within the region and pointers to its children. If the array covered by a node is completely free, or if it is entirely allocated to a single task, then it is not further decomposed. Otherwise, the array represented by the node is partitioned evenly into two or four disjoint subarrays, depending upon its size, and represented by child nodes. A formal definition of a free area tree follows.

**Definition 6** Array  $G_1^2[(x_1, y_1), (x_2, y_2)]$  is said to intersect array  $G_2^2[(x_3, y_3), (x_4, y_4)]$  iff  $(x_1 \leq x_4)$  and  $(x_3 \leq x_2)$  and  $(y_1 \leq y_4)$  and  $(y_3 \leq y_2)$ . The intersection of arrays

$$\begin{split} G_1^2[(x_1,y_1),(x_2,y_2)] \cap G_2^2[(x_3,y_3),(x_4,y_4)] = \\ G^2[(\max(x_1,x_3),\max(y_1,y_3)),(\min(x_2,x_4),\min(y_2,y_4))] \end{split}$$

if  $(x_1 \le x_4)$  and  $(x_3 \le x_2)$  and  $(y_1 \le y_4)$  and  $(y_3 \le y_2)$ , otherwise it does not exist and is defined to be  $\emptyset$ .

**Definition 7** The area of the array  $G^2[(x_1, y_1), (x_2, y_2)]$  is

$$ar(G_1^2[(x_1, y_1), (x_2, y_2)]) = (x_2 - x_1 + 1)(y_2 - y_1 + 1).$$

By definition,  $ar(\emptyset) = 0$ .

The free area of the array  $G^2[(x_1, y_1), (x_2, y_2)]$  is the number of unallocated cells  $fa(G^2[(x_1, y_1), (x_2, y_2)])$  in the array.

For the arrangement of tasks  $A(G^2[(1,1),(W,H)]) = \{a(t_i): 1 \leq i \leq n\}$  the free area

$$\begin{split} \mathrm{fa}(G^2[(x_1,y_1),(x_2,y_2)]) &= & \mathrm{ar}(G^2[(x_1,y_1),(x_2,y_2)]) - \\ & & \sum_{i=1}^{i=n} \mathrm{ar}(G^2[(x_1,y_1),(x_2,y_2)] \cap G^2[\mathrm{bl}(t_i),\mathrm{tr}(t_i)]). \end{split}$$

**Definition 8** The predicate  $\mathcal{P}(G^2[(x_1, y_1), (x_2, y_2)])$  is defined to be true if some task  $t_i$  exists such that some but not all of the cells in  $G^2[(x_1, y_1), (x_2, y_2)]$  are allocated to

it, i.e., if for some allocated task  $t_i$ ,  $0 < \operatorname{ar}(G^2[(x_1, y_1), (x_2, y_2)] \cap G^2[\operatorname{bl}(t_i), \operatorname{tr}(t_i)]) < \operatorname{ar}(G^2[(x_1, y_1), (x_2, y_2)])$ .

**Definition 9** (After [72]) The free area tree  $F[(x_1, y_1), (x_2, y_2)]$  covering  $G^2[(x_1, y_1), (x_2, y_2)]$  is defined recursively as follows:

- 1. F[(x,y),(x,y)] is a leaf node.

- 2.  $F[(x, y_1), (x, y_2)]$  with  $y_1 < y_2$  is a node. If  $\mathcal{P}(G^2[(x, y_1), (x, y_2)])$ , then  $F[(x, y_1), (x, y_2)]$  has two children:

- (a)  $F[(x, y_1), (x, |(y_1 + y_2)/2|)]$ , and

- (b)  $F[(x, |(y_1 + y_2)/2| + 1), (x, y_2)].$

- 3.  $F[(x_1, y), (x_2, y)]$  with  $x_1 < x_2$  is a node. If  $\mathcal{P}(G^2[(x_1, y), (x_2, y)])$ , then  $F[(x_1, y), (x_2, y)]$  has two children:

- (a)  $F[(x_1, y), (|(x_1 + x_2)/2|, y)], and$

- (b)  $F[(\lfloor (x_1+x_2)/2\rfloor +1,y),(x_2,y)].$

- 4.  $F[(x_1, y_1), (x_2, y_2)]$  with  $x_1 < x_2$  and  $y_1 < y_2$  is a node. If  $\mathcal{P}(G^2[(x_1, y_1), (x_2, y_2)])$ , then  $F[(x_1, y_1), (x_2, y_2)]$  has four children:

- (a)  $F[(x_1, y_1), (\lfloor (x_1 + x_2)/2 \rfloor, \lfloor (y_1 + y_2)/2 \rfloor)],$

- (b)  $F[(\lfloor (x_1+x_2)/2 \rfloor + 1, y_1), (x_2, \lfloor (y_1+y_2)/2 \rfloor)],$

- (c)  $F[(x_1, \lfloor (y_1 + y_2)/2 \rfloor + 1), (\lfloor (x_1 + x_2)/2 \rfloor, y_2)], \text{ and }$

- (d)  $F[(\lfloor (x_1+x_2)/2 \rfloor + 1, \lfloor (y_1+y_2)/2 \rfloor + 1), (x_2, y_2)].$

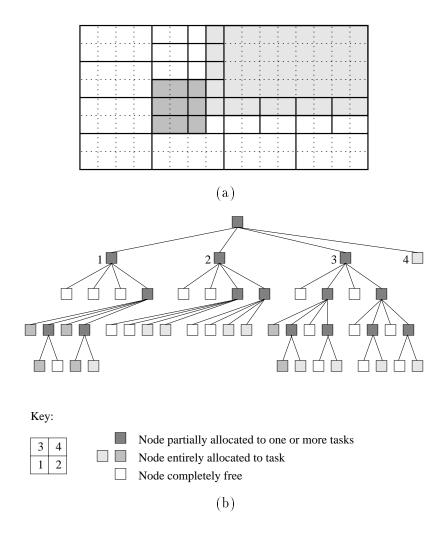

Figure 3.1(a) depicts the arrangement of a pair of tasks on a rectangular array. The array is partitioned to show the regions delimiting the extent of the leaf nodes in the free area tree representation of the arrangement. The free area tree corresponding to the arrangement of Figure 3.1(a) is illustrated in Figure 3.1(b). The left to right order of nodes on each level corresponds to the order in which the children of a node are listed in Definition 9.

When invoked, the local repacking method commences by building the free area tree for an arrangement of tasks on the array. Next the tree is searched for nodes that contain more free cells than are needed by the waiting task. For each such node, a repacking of the tasks allocated to the array covered by the node is attempted. These tasks are found in linear time by checking for intersections with

Figure 3.1: (a) The arrangement of a pair of tasks on an array with free area tree leaves marked. (b) The free area tree for the arrangement of (a).

the node's array. If the new arrangement accommodates the waiting task within the array covered by the node as well, then the rearrangement of the tasks to achieve the packing can be scheduled in order to evaluate its optimality.

Tasks which only partially intersect the array covered by a node need to be handled in some way. Should they be included in the packing, moved elsewhere, or left where they are to be packed around? The approach adopted in this work is to attempt to repack these tasks completely into the rectangular array covered by the node as well. This approach avoids further searching and avoids the complexity of packing into arbitrary rectilinear polygons. At each node, therefore, the area available for the waiting task needs to account for the total area of tasks that are only partially covered by the region.

**Definition 10** If the allocation for task  $t_i$  intersects the array  $G^2[(x_1, y_1), (x_2, y_2)]$ , then the uncovered area

$$ua(t_i, G^2[(x_1, y_1), (x_2, y_2)]) = ar(G^2[bl(t_i), tr(t_i)]) - ar(G^2[bl(t_i), tr(t_i)] \cap G^2[(x_1, y_1), (x_2, y_2)]).$$

Otherwise,  $ua(t_i, G^2[(x_1, y_1), (x_2, y_2)]) = 0$

**Definition 11** The attached area

$$\operatorname{aa}(F[(x_1, y_1), (x_2, y_2)]) = \sum_{i=1}^{i=n} \operatorname{ua}(t_i, G^2[(x_1, y_1), (x_2, y_2)])$$

is the total number of cells allocated to the uncovered portion of tasks that are partially intersected by the free area tree node  $F[(x_1, y_1), (x_2, y_2)]$ .

If the free area less the attached area at a node exceeds the area of the waiting task, then a packing into the array covered by the node of all the tasks intersected by it and the waiting task is attempted.

#### 3.1.2.2 Building the Free Area Tree

The free area tree is expanded iteratively by inserting each of the executing tasks into an initially empty root<sup>1</sup>. The procedure *InsertTaskIntoFAT* of Figure 3.2 updates the free and attached area for the current node and task and recurses with those children that are partially intersected by the task. It expands the tree by creating the children that don't already exist.

Except for step 4(b), each step requires constant time. Since the cost of step 4(b) can be attributed to the descendents of the node input to the procedure, the time spent updating each node in the tree per invocation is thus constant.

Dyer has analyzed the size of the quadtree representation of square objects in square images [26]. He showed that  $O(2^{p+2}-p+q)$  nodes at worst are needed to represent a square of size  $2^p \times 2^p$  in an image of size  $2^q \times 2^q$ . This expression accounts for the perimeter of the square, the logarithm of its diameter, and the height of the root of the tree above the expanded subtree covering the object. If  $m = \max(W, H)$ , then it follows that O(m) nodes of the free area tree are updated per task insertion since no task can be larger than the array. For n tasks therefore, O(mn) time is needed to build the free area tree. The worst case is attained by

<sup>&</sup>lt;sup>1</sup>An empty node has free area set to the area of the array covered by the node and attached area set to zero.

### Procedure InsertTaskIntoFAT

**Input** A pointer to a node in a free area tree and a pointer to the descriptor of a task that is to be inserted into the tree.

Output A free area tree that has been expanded or modified to account for the task inserted into it.

## begin

- 1. Compute the area of intersection (AI) between the node array and the task.

- 2. Update the free area for the node.

- 3. If the area of the task is greater than AI (the node does not wholly contain the task), then

- (a) Update the attached area for the node.

- 4. If the area of the node is greater than AI (the node is not completely allocated to the task), then

- (a) If the children of the node have not yet been created, then

- i. Create child nodes with free area initialized to the child's area and attached area set to zero.

- (b) For each child that intersects the task:

- i. Recurse with the task descriptor and a pointer to the child node.

#### end

Figure 3.2: Procedure InsertTaskIntoFAT.

any arrangement of tasks that occupy entire rows of a square array, for example,  $A(G^2[(1,1)(W,W)]) = \{a(t_i) = G^2[(1,i),(W,i)] : 1 \le i \le n \le W\}.$

It would be possible to reduce the O(mn) time required to build the free area tree if it were updated as allocations, deallocations, and rearrangements occurred. Insertions or deletions into the free area tree require O(m) time. However, a local repacking can potentially rearrange all of the tasks executing on the array, thereby entirely changing the structure of the tree. Nevertheless, rebuilding the tree after each rearrangement would represents a saving over building it each time the feasibility of rearrangement were to be checked.

## 3.1.2.3 Searching the Free Area Tree

It is desirable that the free area tree be searched in some way that allows promising regions to be discovered early in the search. Ideally the region that is known to cost least to repack should be discovered first. Searching the tree breadth—first allows schedules affecting successively fewer tasks to be discovered and allows the search to be abandoned at a time when the marginal benefit of finding arrangements with lower allocation and execution delays is offset by the growing allocation delay due to the search. A "deepest layer first" search examines those nodes that affect the least number of tasks but have the least chance of accommodating the waiting task first of all. An ideal search therefore starts somewhat higher in the tree and works its way up.

The local repacking method reported upon in Chapter 5 implements a depth—first search of the free area tree and abandons the search once the first feasible arrangement is found.

### 3.1.2.4 Repacking the Tasks

The search of the free area tree identifies those subarrays that might accommodate the waiting task if the tasks allocated to it are rearranged. Well-known strip-packing algorithms can be used to check whether such an arrangement exists.

Given a set of oriented rectangles and a two-dimensional bin of a given width and unbounded height, the strip-packing problem is to find a minimum height non-overlapping orthogonal packing of the rectangles into the bin [5]. This variant of the two-dimensional bin-packing problem is NP-complete. Much attention has therefore been given to finding polynomial time approximation algorithms, i.e., fast algorithms that come within a constant times the height used by an optimal packing

[15]. For L an arbitrary list of rectangles, let OPT(L) denote the minimum possible bin height into which the rectangles in L can be packed, and let A(L) denote the height actually used by a particular algorithm when applied to L [16]. An absolute performance bound  $\beta$  for A is a bound of the form

$$A(L) \leq \beta OPT(L)$$

.

On the other hand, in asymptotic performance bounds of the form

$$A(L) \le \beta OPT(L) + \gamma$$

,

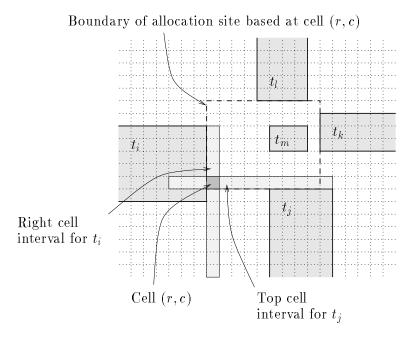

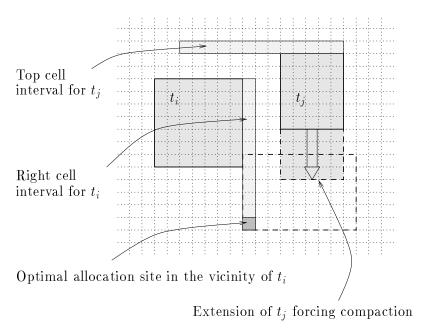

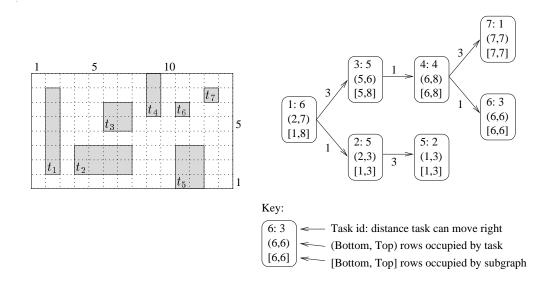

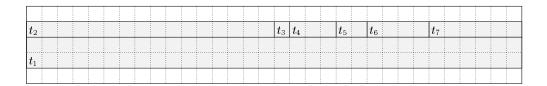

the constant  $\beta$  is intended to characterize the behaviour of the algorithm as the ratio between OPT(L) and the maximum height rectangle in L goes to infinity. The height of the tallest rectangle is usually normalized to 1, whereby any other choice would only affect the constant  $\gamma$ .