## Configuration Encoding Techniques for Fast FPGA Reconfiguration

#### Usama Malik

Bachelor of Engineering, UNSW 2002

A thesis submitted in fulfilment of the requirements for the degree of

#### **Doctor of Philosophy**

School of Computer Science and Engineering

## THE UNIVERSITY OF NEW SOUTH WALES

SYDNEY · AUSTRALIA

June 2006

Copyright © 2006, Usama Malik

## Originality Statement

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

| Signed |  |

|--------|--|

|--------|--|

## Acknowledgements

I would like to thank my supervisor, Dr. Oliver Diessel, for his continuous support in this project. Thank you for your high throughput editing, short response time feedback and fine-grained discussions containing no null data!

Numerous other researchers have given useful feedback on this work. Their names are, in alphabetical order, Aleksandar Ignjatovic (UNSW, Australia), Christophe Bobda (University of Erlangen, Germany), Gareth Lee (UWA, Australia), Professor George Milne (UWA, Australia), Gordon Brebner (Xilinx Inc., USA), Professor Hartmut Schmeck (Karlsruhe University, Germany), A/Professor Hossam ElGindy (UNSW, Australia), Professor Jürgen Teich (University of Erlangen, Germany), Kate Fisher (UNSW, Australia). A/Professor Katherine Compton (UWM, USA), Mark Shand (Compaq Inc., France), Professor Martin Middendorf (University of Leipzig, Germany), Peter Alfke (Xilinx Inc., USA), Philip Leong (Imperial College, UK) and A/Professor Sri Parameswaran (UNSW, Australia).

The Australian Research Council (ARC), the School of Computer Science and Engineering (CSE) and the National Institute of Information and Communication Technologies Australia (NICTA) are acknowledged for providing with the funding. In particular, Professor Paul Compton (the head of CSE), Professor Albert Nymeyer (the head of postgraduate research at CSE), Terry Percival (Director NICTA's research) and Professor Gernot Heiser (the head of Embedded and Real-time Systems (ERTOS) group in NICTA) are acknowledged for their continuous financial support for this project. The organisers of the International Conference on Field Programmable Logic and

Applications (FPL) 2003 are acknowledged for providing the travel fund that enabled me to present my work at the PhD poster session in Belgium.

#### Abstract

This thesis examines the problem of reducing reconfiguration time of an island-style FPGA at its configuration memory level. The approach followed is to examine configuration encoding techniques in order to reduce the size of the bitstream that must be loaded onto the device to perform a reconfiguration. A detailed analysis of a set of benchmark circuits on various island-style FPGAs shows that a typical circuit randomly changes a small number of bits in the null or default configuration state of the device. This feature is exploited by developing efficient encoding schemes for configuration data. For a wide set of benchmark circuits on various FPGAs, it is shown that the proposed methods outperform all previous configuration compression methods and, depending upon the relative size of the circuit to the device, compress within 5% of the fundamental information theoretic limit. Moreover, it is shown that the corresponding decoders are simple to implement in hardware and scale well with device size and available configuration bandwidth. It is not unreasonable to expect that with little modification to existing FPGA configuration memory systems and acceptable increase in configuration power a 10-fold improvement in configuration delay could be achieved. The main contribution of this thesis is that it defines the limit of configuration compression for the FPGAs under consideration and develops practical methods of overcoming this reconfiguration bottleneck. The functional density of reconfigurable devices could thereby be enhanced and the range of potential applications reasonably expanded.

## Contents

| Li       | st of                  | Figures                          | X  |  |

|----------|------------------------|----------------------------------|----|--|

| Li       | $\operatorname{st}$ of | Tables                           | iv |  |

| 1        | Introduction           |                                  |    |  |

|          | 1.1                    | Research Context                 | 2  |  |

|          | 1.2                    | Problem Background               | 3  |  |

|          | 1.3                    | Thesis Contributions             | 4  |  |

|          | 1.4                    | Thesis Outline                   | 7  |  |

| <b>2</b> | Rel                    | ated Work and Contributions      | 9  |  |

|          | 2.1                    | Introduction                     | 9  |  |

|          | 2.2                    | Partial Reconfiguration          | 9  |  |

|          | 2.3                    | Configuration Compression        | 12 |  |

|          | 2.4                    | Specialised Architectures        | 14 |  |

|          | 2.5                    | Configuration Caching            | 15 |  |

|          | 2.6                    | Circuit Scheduling and Placement | 15 |  |

|          | 2.7                    | Summary                          | 16 |  |

| 3        | Mo                     | dels and Problem Formulation     | 17 |  |

|          | 3.1                    | Introduction                     | 17 |  |

|          | 3.2                    | Hardware Platforms               | 17 |  |

|   |                   | 3.2.1                                                                                             | The device model                                | 18                                                       |

|---|-------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|

|   |                   | 3.2.2                                                                                             | The system model                                | 26                                                       |

|   | 3.3               | Progra                                                                                            | amming Environments                             | 31                                                       |

|   |                   | 3.3.1                                                                                             | Hardware description languages                  | 31                                                       |

|   |                   | 3.3.2                                                                                             | Conventional programming languages              | 37                                                       |

|   | 3.4               | Exam                                                                                              | oles of Runtime Reconfigurable Applications     | 38                                                       |

|   |                   | 3.4.1                                                                                             | A triple DES core                               | 39                                                       |

|   |                   | 3.4.2                                                                                             | A specialised DES circuit                       | 39                                                       |

|   |                   | 3.4.3                                                                                             | The Circal interpreter                          | 43                                                       |

|   | 3.5               | Proble                                                                                            | em Formulation                                  | 46                                                       |

|   |                   | 3.5.1                                                                                             | Motivation                                      | 46                                                       |

|   |                   | 3.5.2                                                                                             | Problem statement                               | 48                                                       |

|   |                   |                                                                                                   |                                                 |                                                          |

| 4 | An                | Analy                                                                                             | sis of Partial Reconfiguration in Virtex        | 49                                                       |

| 4 | <b>An</b> 4.1     |                                                                                                   | sis of Partial Reconfiguration in Virtex uction | <b>49</b>                                                |

| 4 |                   |                                                                                                   |                                                 |                                                          |

| 4 |                   | Introd                                                                                            | uction                                          | 49<br>50                                                 |

| 4 |                   | Introd<br>4.1.1<br>4.1.2                                                                          | The experimental environment                    | 49<br>50                                                 |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2                                                                          | The experimental environment                    | 49<br>50<br>52                                           |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc                                                                 | The experimental environment                    | 49<br>50<br>52<br>57                                     |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1                                                        | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59                         |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1<br>4.2.2<br>4.2.3                                      | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59                         |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1<br>4.2.2<br>4.2.3                                      | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59<br>60                   |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1<br>4.2.2<br>4.2.3<br>Reduc                             | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59<br>60<br>61             |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1<br>4.2.2<br>4.2.3<br>Reduc<br>4.3.1<br>4.3.2           | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59<br>60<br>61<br>61       |

| 4 | 4.1               | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1<br>4.2.2<br>4.2.3<br>Reduc<br>4.3.1<br>4.3.2<br>The In | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59<br>60<br>61<br>61       |

| 4 | 4.1<br>4.2<br>4.3 | Introd<br>4.1.1<br>4.1.2<br>Reduc<br>4.2.1<br>4.2.2<br>4.2.3<br>Reduc<br>4.3.1<br>4.3.2<br>The In | The experimental environment                    | 49<br>50<br>52<br>57<br>57<br>59<br>60<br>61<br>61<br>65 |

|   |     | 4.5.3  | Analysis                                               |

|---|-----|--------|--------------------------------------------------------|

|   | 4.6 | Analy  | sing Default-state reconfiguration                     |

|   |     | 4.6.1  | The impact of configuration granularity                |

|   |     | 4.6.2  | The impact of device size                              |

|   |     | 4.6.3  | The impact of circuit size                             |

|   | 4.7 | The C  | Configuration Addressing Problem 83                    |

|   | 4.8 | Evalua | ating Various Addressing Techniques                    |

|   | 4.9 | Chapt  | er Summary                                             |

| 5 | Nev | v Conf | iguration Architectures for Virtex 91                  |

|   | 5.1 | Introd | uction                                                 |

|   | 5.2 | Virtex | Configuration Memory Internals                         |

|   | 5.3 | ARCH   | I-I: Fine-Grained Partial Reconfiguration in Virtex 96 |

|   |     | 5.3.1  | Approach                                               |

|   |     | 5.3.2  | Design description                                     |

|   |     | 5.3.3  | Analysis                                               |

|   | 5.4 | ARCH   | I-II: Automatic Reset in ARCH-I                        |

|   |     | 5.4.1  | Approach                                               |

|   |     | 5.4.2  | Design description                                     |

|   |     | 5.4.3  | Analysis                                               |

|   | 5.5 | ARCE   | I-III: Scaling Configuration Port Width in ARCH-II 113 |

|   |     | 5.5.1  | Approach                                               |

|   |     | 5.5.2  | Design description                                     |

|   |     | 5.5.3  | Analysis                                               |

|   | 5.6 | Conclu | usions                                                 |

| 6 | Con | npress | ing Virtex Configuration Data 125                      |

|   | 6.1 | Introd | uction                                                 |

|   | 6.2 | Entro  | by of Reconfiguration                                  |

|   |     | 6.2.1   | Definition                                           |

|---|-----|---------|------------------------------------------------------|

|   |     | 6.2.2   | A model of Virtex configurations                     |

|   |     | 6.2.3   | Measuring Entropy of Reconfiguration                 |

|   |     | 6.2.4   | Exploring the randomness assumption of the model 133 |

|   | 6.3 | Evalua  | ating Existing Configuration Compression Methods 138 |

|   |     | 6.3.1   | LZ-based methods                                     |

|   |     | 6.3.2   | A method based on inter-frame differences 145        |

|   |     | 6.3.3   | Conclusions                                          |

|   | 6.4 | Comp    | ressing $\phi'$ Configurations                       |

|   |     | 6.4.1   | Golomb encoding                                      |

|   |     | 6.4.2   | Hierarchical vector compression                      |

|   | 6.5 | ARCE    | H-IV: Decompressing Configurations in Hardware 152   |

|   |     | 6.5.1   | Design challenges                                    |

|   |     | 6.5.2   | Solution strategy                                    |

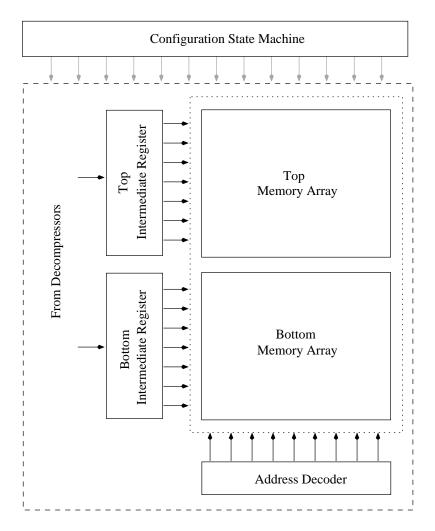

|   |     | 6.5.3   | Memory design                                        |

|   |     | 6.5.4   | Decompressor design                                  |

|   |     | 6.5.5   | Design analysis                                      |

|   | 6.6 | Concl   | usions                                               |

| 7 | Cor | ıfigura | tion Encoding for Generic Island-Style FPGAs 169     |

|   | 7.1 | Introd  | luction                                              |

|   | 7.2 | Exper   | imental Method                                       |

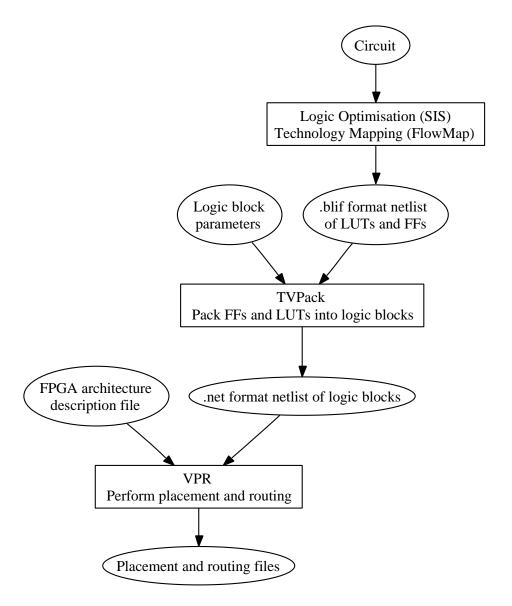

|   | 7.3 | TVPa    | ck and VPR Tools                                     |

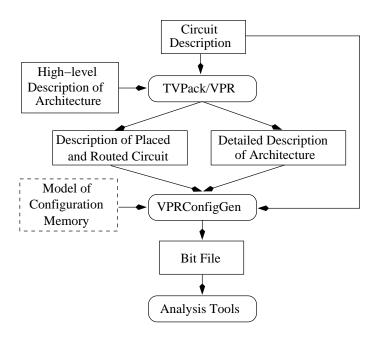

|   | 7.4 | VPRC    | ConfigGen Tools                                      |

|   |     | 7.4.1   | CLB configuration                                    |

|   |     | 7.4.2   | Switch configuration                                 |

|   |     | 7.4.3   | Connection block configuration                       |

|   |     | 7.4.4   | Configuration formats                                |

|              | 7.5   | Measuring Entropy of Reconfiguration                               | . 183 |

|--------------|-------|--------------------------------------------------------------------|-------|

|              | 7.6   | Compressing Configuration Data                                     | . 189 |

|              | 7.7   | The Impact of Cluster Size on Reconfiguration Time                 | . 189 |

|              | 7.8   | The Impact of Channel Routing Architecture on Reconfiguration Time | . 194 |

|              | 7.9   | Generic Configuration Architectures                                | . 196 |

|              | 7.10  | Conclusions                                                        | . 198 |

| 8            | Con   | clusion & Future Work                                              | 199   |

| $\mathbf{A}$ | A N   | ote on the Use of the Term 'Configuration'                         | 202   |

| В            | Deta  | ailed Results for Section 4.8                                      | 204   |

| C            | Sim   | ulating ARCH-III                                                   | 217   |

| Bi           | bliog | raphy                                                              | 222   |

## List of Figures

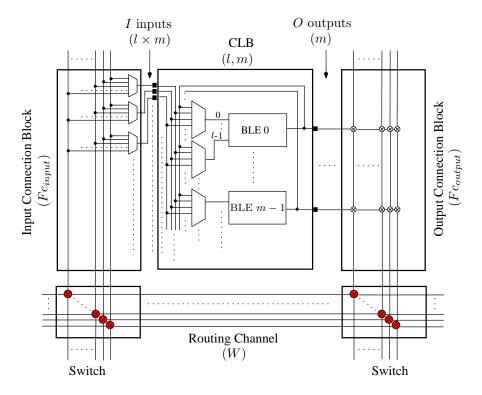

| 3.1  | A generic island-style FPGA. A basic block is enlarged to show |    |

|------|----------------------------------------------------------------|----|

|      | its internal structure                                         | 19 |

| 3.2  | The internal architecture of the model FPGA                    | 20 |

| 3.3  | A simplified model of a Virtex CLB (adapted from [121])        | 24 |

| 3.4  | The $24 \times 24$ singles switch box in a Virtex device       | 24 |

| 3.5  | All possible connection of a subset switch                     | 25 |

| 3.6  | A six pass-transistor implementation of a switch point         | 25 |

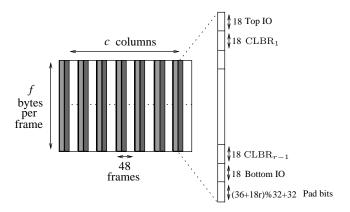

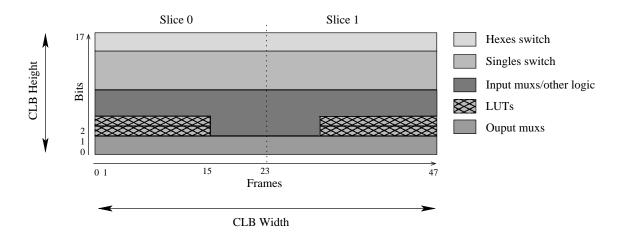

| 3.7  | A simplified model of configuration memory of a Virtex         | 27 |

| 3.8  | The internal details of Virtex frames                          | 27 |

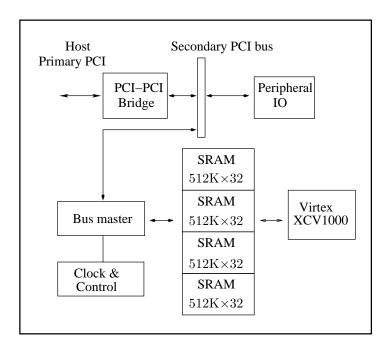

| 3.9  | The Celoxica RC1000 FPGA board                                 | 29 |

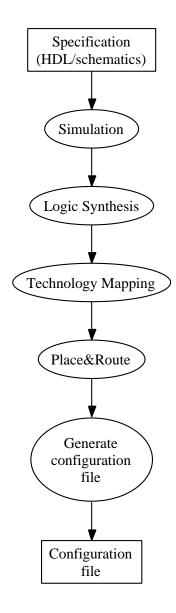

| 3.10 | Typical FPGA design flow                                       | 33 |

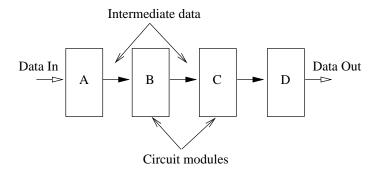

| 3.11 | An example of a hypothetical dataflow system                   | 34 |

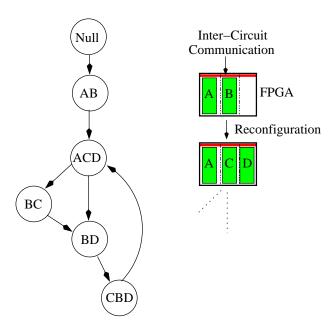

| 3.12 | An example reconfigurable system. The circuit schedule is      |    |

|      | shown on the left while various configuration states of the    |    |

|      | FPGA on the right                                              | 35 |

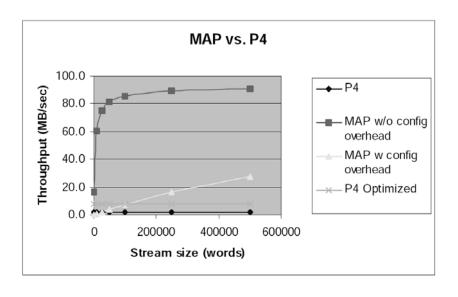

| 3.13 | Performance measurements for Triple DES [31]                   | 40 |

| 3.14 | Performance measurements for Triple DES [24]                   | 42 |

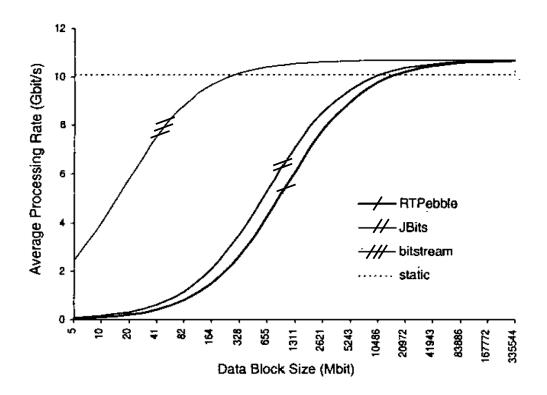

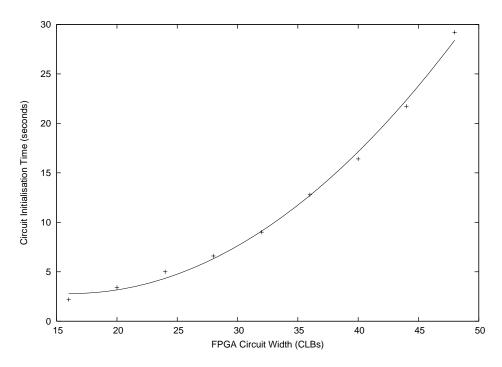

| 3.15 | Circuit initialisation time of the CirCal interpreter [63]     | 45 |

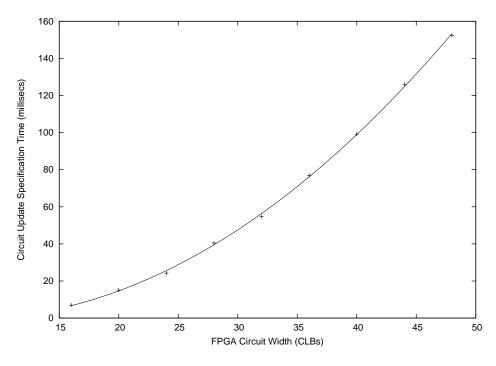

| 3.16 | Circuit update time of the CirCal interpreter [63]             | 45 |

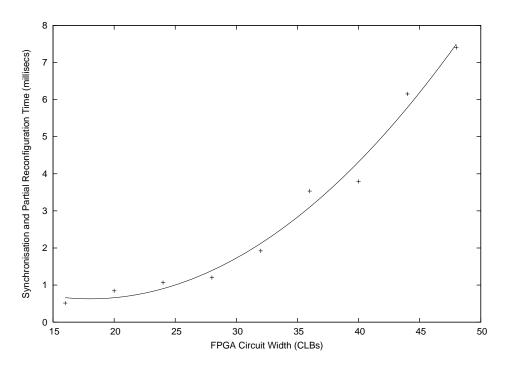

| 3.17 | Partial reconfiguration time of the CirCal interpreter [63]    | 46 |

| 4.1  | An example core-style reconfiguration when the FPGA is time                                                                           |   |

|------|---------------------------------------------------------------------------------------------------------------------------------------|---|

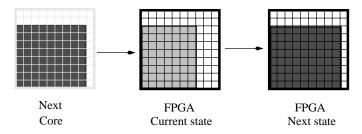

|      | shared between circuit cores                                                                                                          | 2 |

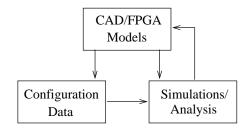

| 4.2  | A high-level view of the research framework                                                                                           | 3 |

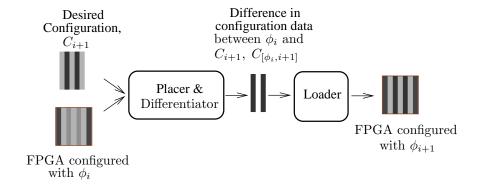

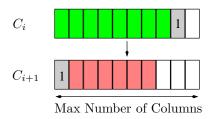

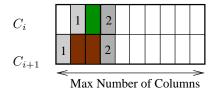

| 4.3  | The operation of Algorithm 1                                                                                                          | 3 |

| 4.4  | Explaining the non-alignability of the common frames 65                                                                               | 3 |

| 4.5  | An example of frame interlocking 64                                                                                                   | 1 |

| 4.6  | Coarse vs. fine-grained partial reconfiguration 65                                                                                    | 5 |

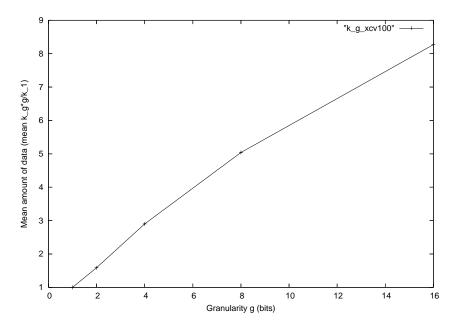

| 4.7  | The amount of configuration data needed at granularity $g$ relative to the amount of data needed at a granularity of a single bit     | 7 |

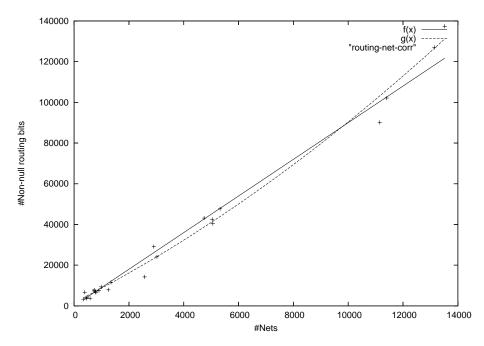

| 4.8  | Correlating the number of nets with the total number of non-null routing bits used to configure an XCV400 with the benchmark circuits | 1 |

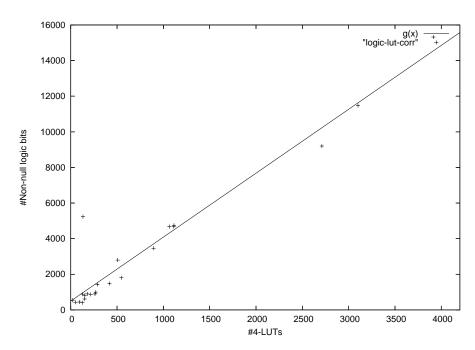

| 4.9  | Correlating the number of LUTs with the total number of non-null logic bits used to configure an XCV400 with the benchmark circuits   | 2 |

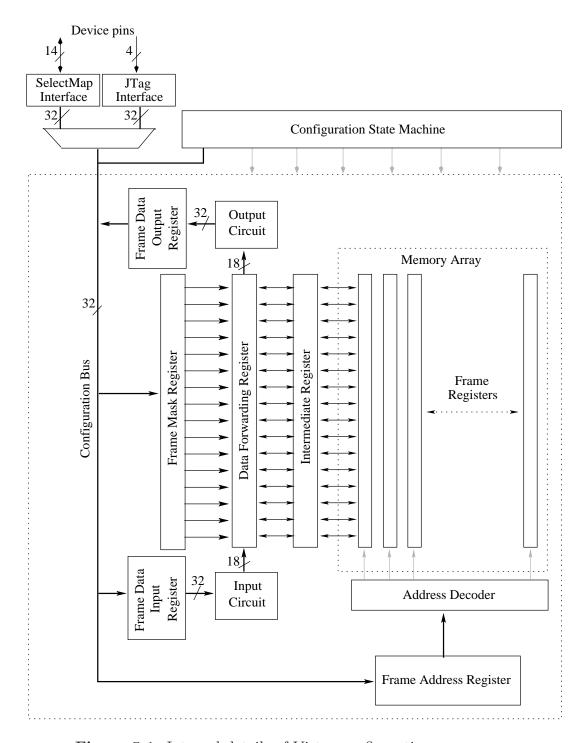

| 5.1  | Internal details of Virtex configuration memory 93                                                                                    | 3 |

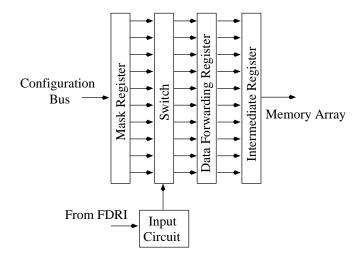

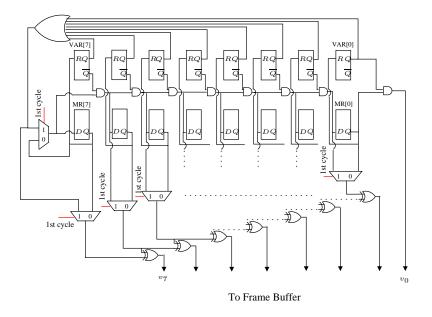

| 5.2  | The internal architecture of the input circuit 98                                                                                     | 5 |

| 5.3  | Comparing the operation of Virtex and ARCH-I 97                                                                                       | 7 |

| 5.4  | Virtex redesigned with an intermediate switch                                                                                         | 3 |

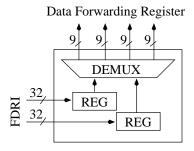

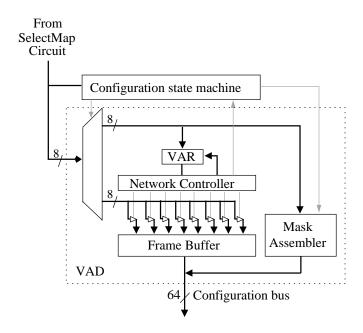

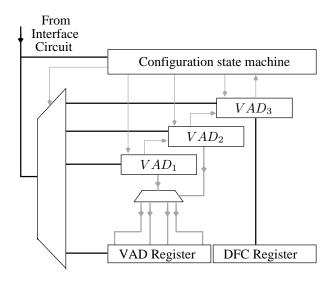

| 5.5  | The vector address decoder (VAD)                                                                                                      | ) |

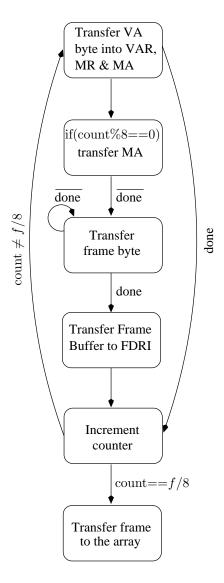

| 5.6  | The control of the VAD                                                                                                                | L |

| 5.7  | The structure of the network controller                                                                                               | 2 |

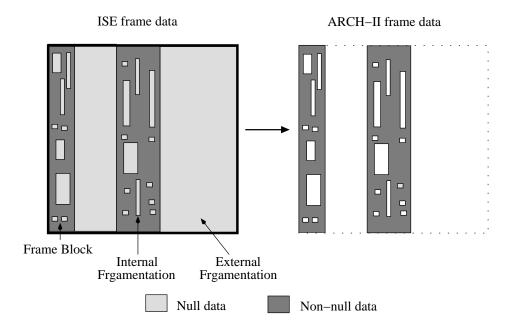

| 5.8  | Internal vs. external fragmentation in a user configuration 105                                                                       | 5 |

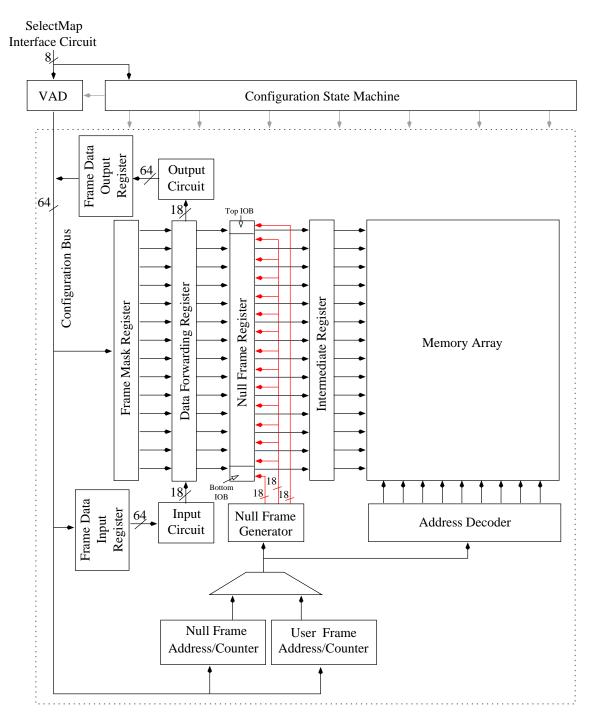

| 5.9  | The design of ARCH-II                                                                                                                 | ) |

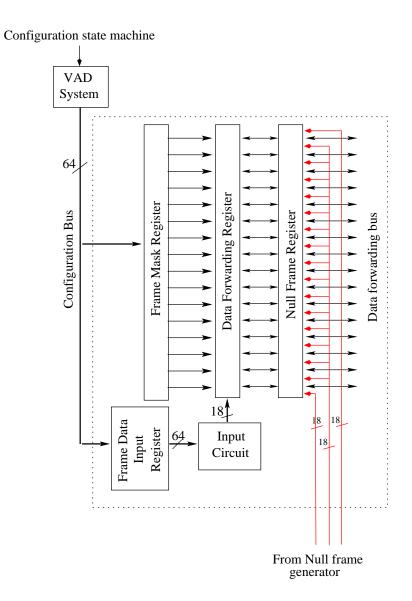

| 5.10 | The VAD-FDRI System                                                                                                                   | 5 |

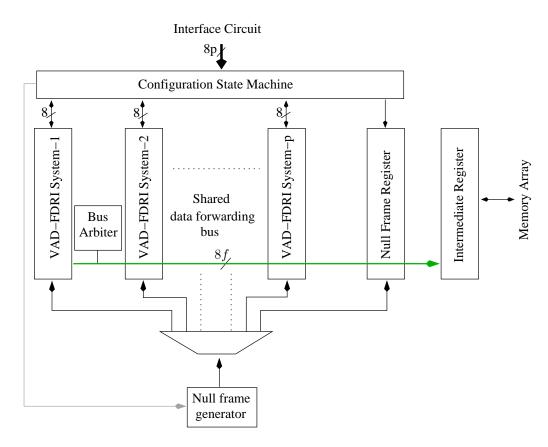

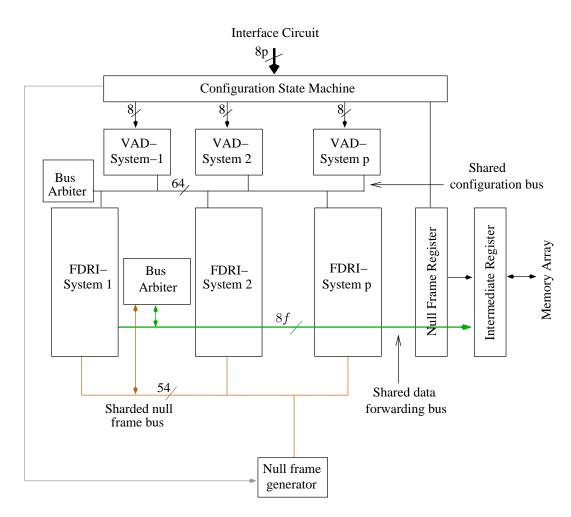

| 5.11 | The parallel configuration system                                                                                                     | 3 |

| 5.12 | The datapath of ARCH-III                                                                                                              | 7 |

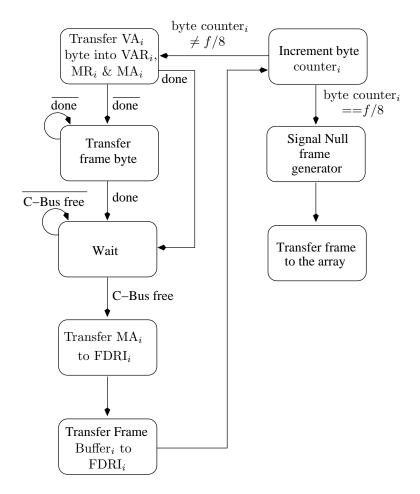

| 5.13 | The control of the $i_{th}$ VAD in ARCH-III                                                                                                                                                                             |

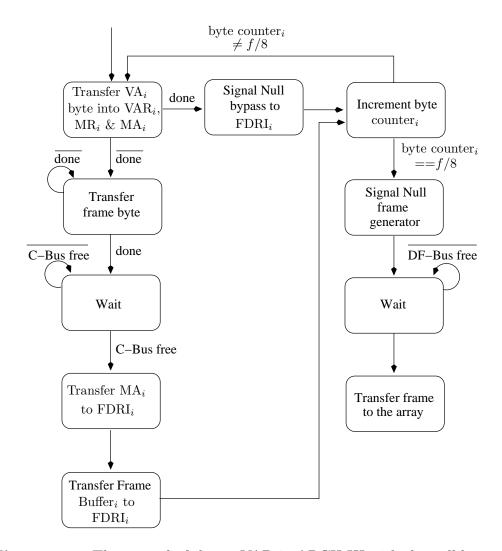

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.14 | The control of the $i_{th}$ VAD in ARCH-III with the null bypass. 122                                                                                                                                                   |

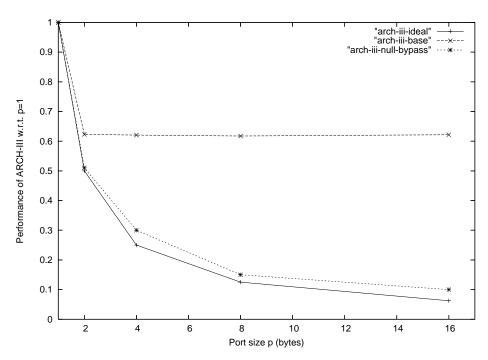

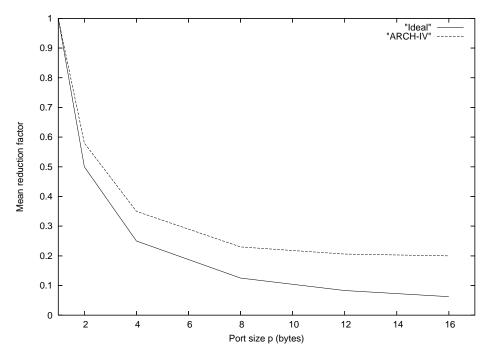

| 5.15 | Evaluating the performance of ARCH-III. Target device = XCV400                                                                                                                                                          |

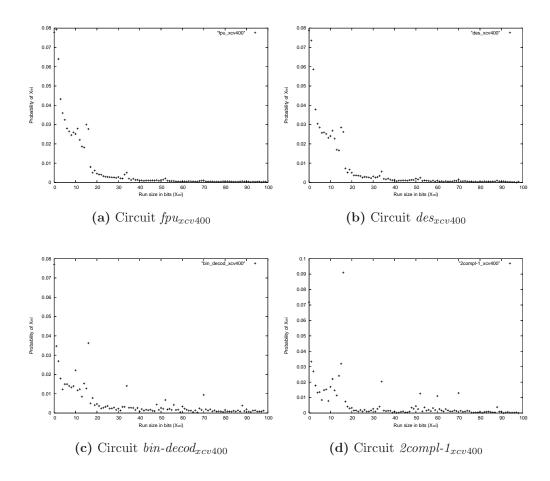

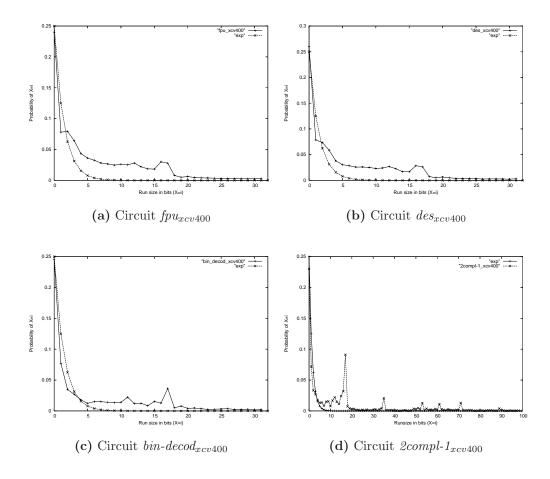

| 6.1  | The relationship between runsize $i$ and $P(X = i), i > 0$ , for four selected circuits on an XCV400                                                                                                                    |

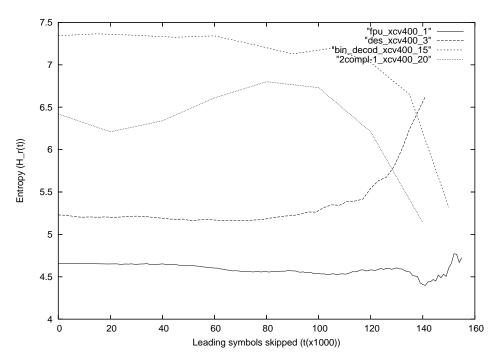

| 6.2  | $H_r^t$ as a function of the number of symbols dropped 134                                                                                                                                                              |

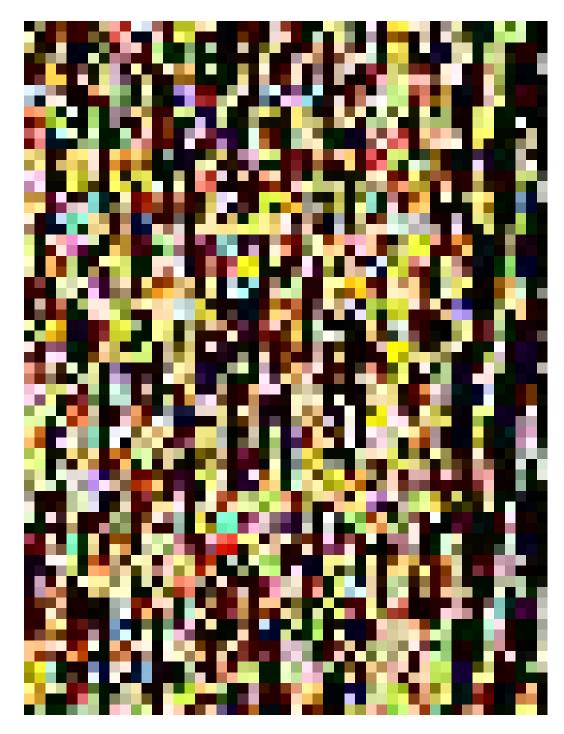

| 6.3  | A slice of configuration data corresponding to circuit $fpu_{xcv400}$ .<br>The image is shown in 24 bits RGB colour space 136                                                                                           |

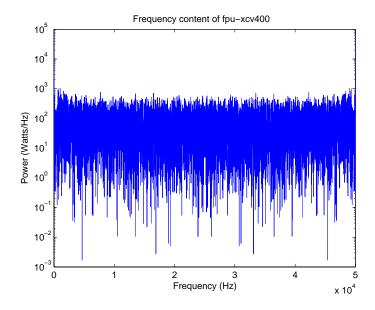

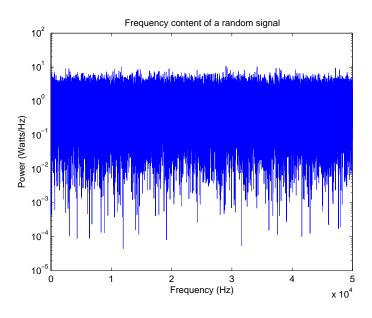

| 6.4  | Comparing the power spectrums of the runlengths in the $\phi'$ of $fpu$ configuration and a random signal                                                                                                               |

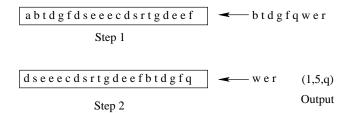

| 6.5  | An example operation of the LZ77 algorithm                                                                                                                                                                              |

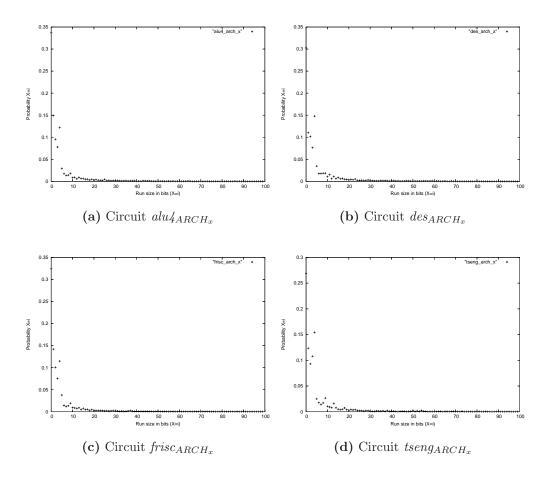

| 6.6  | Comparing probability distribution of the shortes 32 runlengths in four selected $\phi'$ configurations with $exp=2^{-x}$ . Target device = XCV400                                                                      |

| 6.7  | An example of Golomb encoding (taken from [12]) 150                                                                                                                                                                     |

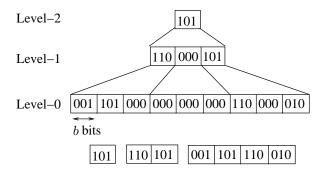

| 6.8  | An example demonstrating the hierarchical vector compression algorithm. The uncompressed vector address is shown at Level-0. The resulting compressed vector is shown below the levels of compression (taken from [14]) |

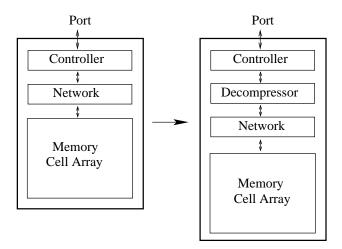

| 6.9  | The environment of the required decompressor 157                                                                                                                                                                        |

| 6.10 | The proposed memory architecture                                                                                                                                                                                        |

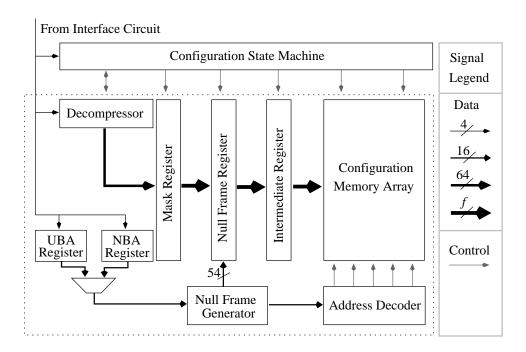

| 6.11 | A high-level view of the decompressor                                                                                                                                                                                   |

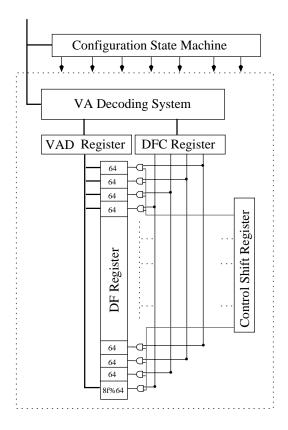

| 6.12 | The architecture of the vector address decoding system 162                                                                                                                                                              |

| 6.13 | The overhead of ARCH-IV for large sized ports 165                                                                                                                                                                       |

| 6.14 | Pipelining the operation of loading the frames                                                                                                                                                                          |

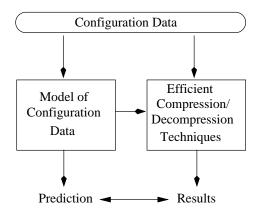

| 7.1  | The approach followed in this thesis                                                                                                                                                                                    |

| 7.2  | The experimental setup                                                                                                                                                                                                  |

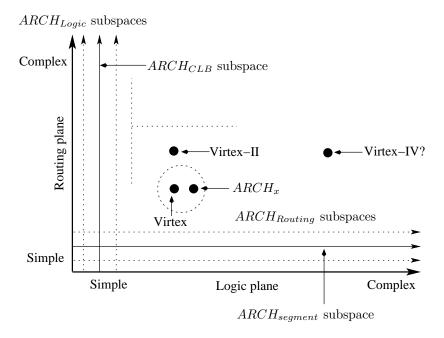

| 7.3  | FPGA architecture space                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.4  | TVPack and VPR simulation flow                                                                                                                                                                                                                                                                                                                                                         |

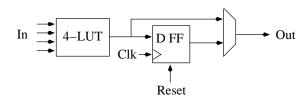

| 7.5  | Basic logic element (BLE)                                                                                                                                                                                                                                                                                                                                                              |

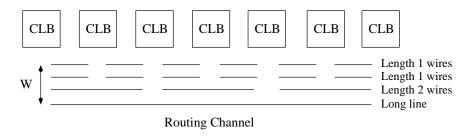

| 7.6  | FPGA architecture definition                                                                                                                                                                                                                                                                                                                                                           |

| 7.7  | Hierarchical routing in an FPGA. Connections between the tracks and the CLBs are not shown                                                                                                                                                                                                                                                                                             |

| 7.8  | An example entry in a .blif file                                                                                                                                                                                                                                                                                                                                                       |

| 7.9  | An example entry in a .net file                                                                                                                                                                                                                                                                                                                                                        |

| 7.10 | An example entry in a .route file                                                                                                                                                                                                                                                                                                                                                      |

|      | The relationship between runsize $i$ and $P(X = i), i > 0$ , for four selected circuits on $ARCH_x$                                                                                                                                                                                                                                                                                    |

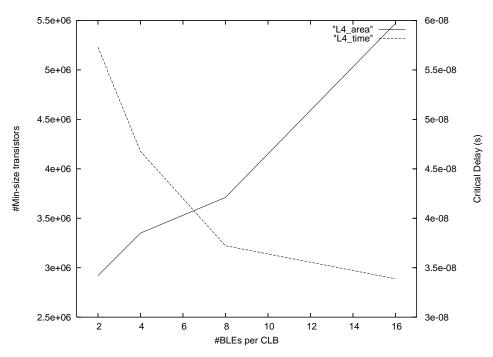

| 7.12 | Mean area and delay for the benchmark circuits with various CLB sizes. L4 signifies that Length-4 wires were used in all architectures                                                                                                                                                                                                                                                 |

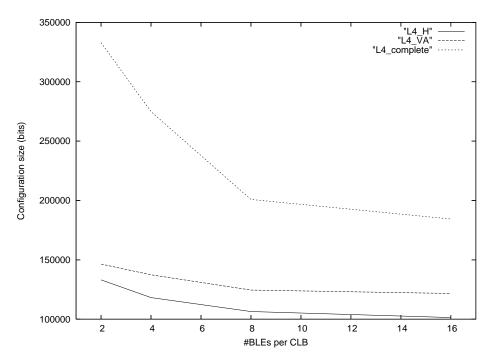

| 7.13 | Mean of complete configuration sizes (L4_complete), mean of minimum possible configuration sizes (L4_H) as predicted by the entropic model of configuration data and mean of vector compressed configuration sizes (L4_VA) for the benchmark circuits under various CLB sizes. L4 means that Length-4 wires were used in each routing channel. Format 1 was used in all configurations |

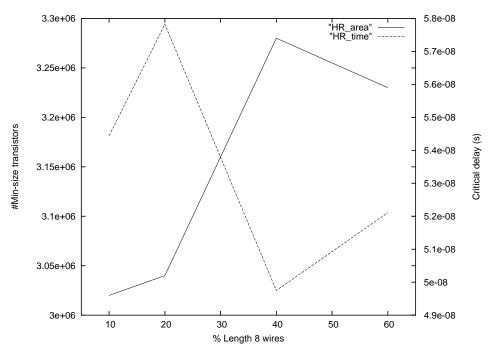

| 7.14 | Mean area and delay for the benchmark circuits for various<br>Length-4:Length-8 wire ratios. HR signifies hierarchical routing.196                                                                                                                                                                                                                                                     |

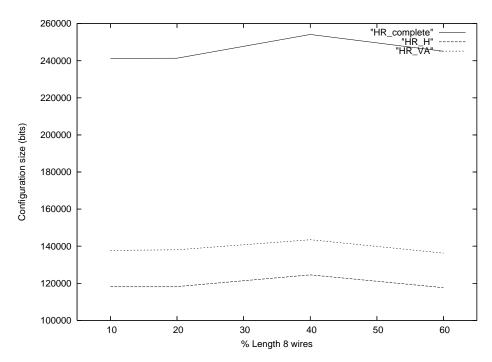

| 7.15 | Mean of complete configuration sizes (HR_complete), mean of minimum possible configuration sizes (HR_H) and mean of vector compressed configuration sizes (HR_VA) for the benchmark circuits under various CLB sizes. HR means hierarchical routing was employed. Format 1 was used in all configurations. 197                                                                         |

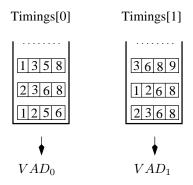

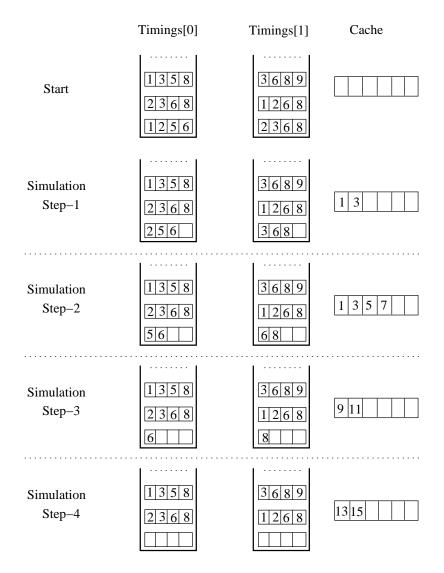

| C.1  | An example Timings[] stacks $(p=2)$                                                                                                                                                                                                                                                                                                                                                    |

| C.2  | An example simulation of ARCH-III $(p = 2), \dots, 221$                                                                                                                                                                                                                                                                                                                                |

## List of Tables

| 3.1 | Number of frames in a Virtex device                                                                                                                                                                                                                          | 24 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Performance comparison of a general purpose vs. specialised                                                                                                                                                                                                  |    |

|     | DES. $x$ denotes the number of configurations generated [24]                                                                                                                                                                                                 | 42 |

| 4.1 | Important parameters of Virtex devices                                                                                                                                                                                                                       | 51 |

| 4.2 | The set of benchmark circuits used for the analysis                                                                                                                                                                                                          | 51 |

| 4.3 | Estimated and actual % reduction in the amount of configuration data for variously sized sub-frames                                                                                                                                                          | 66 |

| 4.4 | Deriving the optimal frame size assuming fixed circuit placements                                                                                                                                                                                            | 67 |

| 4.5 | The size of difference configurations in bits when circuit $b$ was placed over circuit $a$ . The target device was an XCV1000                                                                                                                                | 71 |

| 4.6 | The relative number of $null$ bits in the difference configurations (circuit $a \to \text{circuit } b$ ) as a percentage of the total number of CLB-frame bits in the device. The target device was an XCV1000. All numbers are rounded to one decimal digit | 72 |

| 4.7 | The relative number of $non-null$ bits in the difference configurations (circuit $a \to \text{circuit } b$ ) as a percentage of the total number of CLB-frame bits in the device. The target device was an XCV1000. All numbers are rounded to one decimal   | 70 |

|     | digit                                                                                                                                                                                                                                                        | 73 |

| 48  | The benchmark circuits and their parameters of interest                                                                                                                                                                                                      | 75 |

| 4.9  | comparing the change in the amount of non-null data for the same circuit mapped onto variously sized devices 79        |

|------|------------------------------------------------------------------------------------------------------------------------|

| 4.10 | Comparing various addressing schemes. Granularity = 8 bits. Target device = $XCV100. \dots 87$                         |

| 4.11 | Comparing various addressing schemes. Granularity = 8 bits. Target device = $XCV400.$                                  |

| 4.12 | Comparing various addressing schemes. Granularity = 8 bits.  Target device = XCV1000                                   |

| 5.1  | The contents of CLB null frames                                                                                        |

| 5.2  | Percentage reduction in reconfiguration time of ARCH-II compared to current Virtex                                     |

| 6.1  | Predicted and observed reductions in each $\phi'$ configuration 130                                                    |

| 6.2  | Estimating the maximum performance of the LZSS compression method with frame reordering. Target device $=$ XCV400. 143 |

| 6.3  | Results of executing Algorithm 4 on the benchmark circuits.  Target device = XCV400                                    |

| 6.4  | Golomb Encoding: an example for m=4 (taken from [12]) 150                                                              |

| 6.5  | Comparing theoretical and observed reductions in each $\phi'$ . The target was an XCV200                               |

| 6.6  | Comparing theoretical and observed reductions in each $\phi'$ .<br>The target was an XCV400                            |

| 6.7  | Comparing theoretical and observed reductions in each $\phi'$ .<br>The target was an XCV1000                           |

| 6.8  | Percentage reduction in reconfiguration time of ARCH-IV compared to current Virtex                                     |

| 6.9  | Percentage reduction in mean reconfiguration time for the benchmark set of ARCH-IV compared to current Virtex 166      |

| 7.1  | Various parameters of VPack/VPR and their typical values 179                                                           |

| 7.2  | CAD parameters for FPGA architecture $ARCH_x$ 185                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.3  | Parameters of the benchmark circuits on $ARCH_x$                                                                                                                                            |

| 7.4  | Reductions in bitstream sizes achieved using Format 3 190                                                                                                                                   |

| 7.5  | CAD parameters for FPGA architectures $ARCH_{CLB}$ 191                                                                                                                                      |

| 7.6  | CAD parameters for FPGA architectures $ARCH_{switch}$ 195                                                                                                                                   |

| B.1  | The amount of non-null data in bits. Configuration granularity = 1 bit. $\dots \dots \dots$ |

| B.2  | The amount of non-null data in bits. Configuration granularity = $2$ bits                                                                                                                   |

| B.3  | The amount of non-null data in bits. Configuration granularity = 4 bits                                                                                                                     |

| B.4  | Comparing various addressing schemes. Granularity = 4 bits.  Target device = XCV100                                                                                                         |

| B.5  | Comparing various addressing schemes. Granularity = 8 bits.  Target device = XCV100                                                                                                         |

| B.6  | Comparing various addressing schemes. Granularity = $16$ bits. Target device = $XCV100$                                                                                                     |

| B.7  | Comparing various addressing schemes. Granularity = 4 bits.  Target device = XCV400                                                                                                         |

| B.8  | Comparing various addressing schemes. Granularity = 8 bits.  Target device = XCV400                                                                                                         |

| В.9  | Comparing various addressing schemes. Granularity = $16$ bits. Target device = $XCV400$                                                                                                     |

| B.10 | Comparing various addressing schemes. Granularity = 4 bits.  Target device = XCV1000                                                                                                        |

| B.11 | Comparing various addressing schemes. Granularity = 8 bits.  Target device = XCV1000                                                                                                        |

| B.12 | Comparing various addressing schemes. Granularity = 16 bits.  Target device = XCV1000                                                                                                       |

## Chapter 1

## Introduction

An SRAM-based Field Programmable Gate Array (FPGA) is a form of programmable circuit that is increasingly seen as a target platform for high performance computing. An FPGA consists of an array of logic blocks that are interconnected by a hierarchical network of wires. A user can program the logic blocks and their inter-connectivity by loading device-specific configuration data onto the device. This data is generated using vendor-specific CAD tools. Once configured, the device behaves as the user specified digital system and thus can be used to perform various functions. Current generation FPGAs can be reconfigured by loading the configuration data afresh, or by altering the on-chip configuration data while the device is in operation. The latter process is referred to as runtime reconfiguration. This work examines the problem of reducing the time needed to reconfigure an FPGA at runtime.

This chapter serves as a road-map to the rest of the document. A general introduction to FPGA-based computing is provided in Section 1.1. Section 1.2 presents the background of the problem that is addressed in this work. Section 1.3 lists the main contributions of the thesis. Finally, a brief guide to the following chapters of this document is provided in Section 1.4.

<sup>&</sup>lt;sup>1</sup>Please see Appendix A for a note on the use of the term *configuration*.

#### 1.1 Research Context

The use of FPGAs for general purpose computing has become popular since the mid-1980s (e.g. see [113] for a list of a large number of computers that incorporate one or more FPGAs in their hardware). FPGAs are seen as an intermediate implementation platform between a commodity processor and a custom made chip. The use of FPGAs for general purpose computing has been made possible by the increased transistor density of these devices and the fact that they can be reconfigured while in operation. FPGAs are able to outperform a microprocessor for a wide range of applications. While FPGAs cannot process data as fast as custom made chips, increasing production costs of the latest VLSI processes and time-to-market pressures lead to considering FPGAs as an alternative to custom ICs as well. Thus, FPGAs have found a niche that has been growing steadily over the years.

The ability to reconfigure an FPGA at runtime has opened new opportunities for novel system designs. It is seen as a method to alleviate the constraints of a limited device size since a runtime reconfigurable FPGA of a certain size can emulate a larger FPGA, albeit at the cost of slowing down the overall execution (e.g. [8]). The penalty paid is the time needed to reconfigure the device during which the device performs no computation. Other uses of runtime reconfiguration are to change the function of the implemented circuits as needed during the final operation (e.g. [13, 47]), or to support a multi-tasking environment in which several tasks execute in parallel (e.g. [96, 98]).

The use of runtime reconfigurable FPGAs in a general purpose environment raises several challenging issues. Designing a runtime reconfigurable application is a difficult task and the performance of the application depends greatly on the target architecture and the skill of the designer. The task of designing a runtime reconfigurable application is further complicated by the fact that there is little off-the-shelf software support for managing the device at runtime. Several attempts have been made to introduce new high-level

programming systems (e.g. [34, 58, 57, 66, 3, 55, 84, 65, 22, 106]) and runtime management systems (e.g. [96, 98, 84, 39]). The acceptability of these methods by a wider range of users is yet to be seen.

## 1.2 Problem Background

The motivation for the research described in this thesis emerged from an earlier research effort aimed at using a process algebraic language CirCal (Circuit Calculus) as a high level programming language for FPGA based computers [69]. A Circal compiler targeting an XC6200 FPGA was developed [30]. Later, this compiler was ported to a Virtex board [88] and was modified into an interpreter [29, 26]. The interpreter is capable of implementing large Circal specifications on limited hardware and contains a primitive runtime management system that performs reconfiguration as is required by the environment into which the target system is embedded.

The above exercise of implementing a generic reconfigurable system onto an FPGA led to a realisation that a top-down approach towards the design leads to considerable difficulties in increasing the system performance [63]. In particular, reconfiguration time was found to be quite large. Two factors contributed to this delay. Firstly, the low-level programming interface [121] to the FPGA introduced significant delays. Secondly, the time needed to load configuration data was found to be significant. Thus, the project motivated a need to better understand the potential to reduce reconfiguration overheads. This thesis focuses on one aspect of runtime reconfiguration namely the time needed to perform reconfiguration. This problem is studied at the configuration memory level of an FPGA for which near optimal approaches to exploiting configuration redundancy are presented.

#### 1.3 Thesis Contributions

This thesis examines the role of partial reconfiguration and configuration compression as general methods for reducing reconfiguration time of a Virtex like FPGA. It is shown that a combination of both methods can result in an efficient solution to the problem of reducing the amount of configuration data that must be loaded to configure a typical circuit on a typical device. New configuration memories are presented that allow the device to be reconfigured in time proportional to the time needed to load the compressed partial configuration data.

Partial reconfiguration is a method that allows the user to selectively modify on-chip configuration data. This thesis examines the potential of this technique as a general method for reducing reconfiguration time given a sequence of typical configurations for a general island-style FPGA. It studies the impact of a range of parameters on the amount of data that is common between successive circuit configurations. These parameters include circuit placement, circuit domain and size, configuration granularity, the order of the input configurations and the size of the target device. It is shown that out of all these, configuration granularity, which refers to the size of the unit of configuration data, has the most significant impact on configuration reuse. It is shown that configuration re-use is significantly increased as the size of the configuration unit is reduced. The origin of this inter-configuration redundancy is traced to null configuration data that the CAD tool inserts into the bitstream to reset various resources to their default state. These results are obtained via a detailed analysis of a set of benchmark circuits on a commercial FPGA, the Virtex device family from Xilinx Inc. [123].

The above analysis leads to the idea that it is more useful to construct a configuration in such a way that it allows fine-grained partial reconfiguration and automatically inserts null data where required. For large-scale devices, such as Virtex, reducing the configuration unit size increases the total number of units in the device. The potential amount of address data therefore

increases proportionally, and thus outweighs the benefits achieved from configuration re-use. This thesis analyses various address encoding schemes to minimise this overhead and devises an addressing method that is suited to fine-grained partial reconfiguration. The thesis thus presents various methods to enhance the configuration memory of current commercial FPGAs so as to allow fine-grained access to their memory at a reasonable addressing overhead and automatically insert null data.

The thesis explores the possibilities of further reducing the amount of configuration data. The experiments presented in this work suggest that it is more useful to represent a circuit's configuration as a *null* configuration together with an edit list of the changes needed to implement the circuit. From the perspective of compressing configuration data, the *null* configuration for a device can simply be hard-coded within the decompressor, which is only supplied with the list of changes needed to implement the input circuit. Thus, the problem of compressing configuration data is transformed into a problem of finding a suitable method for encoding the changes made by a circuit to a null bitstream.

A detailed analysis of typical Virtex configuration shows that the non-null data in a typical circuit configuration is small compared to the overall bitstream size. Moreover, the non-null data is almost randomly distributed over the area spanned by a given circuit. This idea is formalised into a model of configuration data. The main use of the model is that it allows one to measure the *information content* of the configuration bitstream and therefore provides an estimate of the size of the smallest configuration needed to configure the input circuit. In the light of this model, various techniques for compressing configuration data are studied and it is shown that simple off-the-shelf methods perform reasonably well in practice. It is shown that vector compression outperforms the popular LZSS-based techniques and is easier to implement in hardware. A scalable decompressor is presented that performs decompression at the same rate at which compressed data is input to the memory.

It is shown that the above results are not tied to a particular FPGA architecture such as Virtex but can be applied to a wider range of island-style FPGA. The impact of the design of an FPGA's computational plane, i.e. its logic and routing architecture, on the total configuration size and its compressibility is studied. It is shown that a medium-sized logic block not only provides a reasonable compromise between silicon area and circuit delay but also helps to minimise reconfiguration time by facilitating good compression. Early studies show that the routing architecture of the device has less of an impact on the variability of reconfiguration time than the logic architecture. The problem of devising a reconfiguration efficient routing architecture is left for a future study.

The main contributions of this thesis are therefore summarised as follows:

- An in-depth empirical analysis of the potential and limitation of partial reconfiguration as a method to reduce reconfiguration time in the context of a general purpose island-style FPGA.

- New methods of partial reconfiguration that are shown to reduce reconfiguration time of existing FPGAs for a wide set of benchmark circuits. New configuration memory architectures that support the required method.

- A model of configuration data that can be used to estimate the information content of an input configuration. This allows us to predict the reduction in the configuration size that is made possible by an optimal compression technique.

- Enhancements to partial reconfiguration to incorporate configuration compression. It is shown that simple off-the-shelf methods, that have not previously been applied to this domain, perform reasonable compression in practice. The performance of these methods is judged by comparing the achieved compression ratio to the smallest possible (which is predicted by the model).

• New configuration memory architectures that support the enhanced methods.

#### 1.4 Thesis Outline

Chapter 2 examines previous work aimed at reducing reconfiguration time at the configuration memory level of an FPGA. These approaches are compared with the methods presented in this thesis and the differences are highlighted.

Chapter 3 provides necessary background material on the FPGA model used in this work and the types of applications that benefit from and exploit runtime reconfiguration. Several examples from the literature are provided to demonstrate the negative impact of long reconfiguration latency in current FPGAs. The problem of reducing reconfiguration time is then formalised.

Chapter 4 provides an in-depth analysis of configuration data corresponding to a set of benchmark circuits mapped onto a Virtex device. This chapter studies the performance of partial reconfiguration in Virtex devices and describes a better method for performing partial reconfiguration. Chapter 5 presents several configuration memory architectures that incorporate these methods in an increasing order of complexity.

Chapter 6 develops a model of configuration data and measures the information content of typical Virtex configurations. Several compression methods are studied and it is shown that simple off-the-shelf methods provide a reasonable compression in practice. The memory architectures from Chapter 5 are then enhanced to incorporate the chosen hardware decompressor.

Chapter 7 studies the architectures of generic island-style FPGA and repeats the previous analysis in a more general setting. It shows that the results obtained for Virtex devices can also be obtained, with reasonable accuracy, on various island-style FPGAs. The impact of CLB and routing architecture on the overall reconfiguration time is briefly examined. The thesis concludes in Chapter 8 with a summary of the research findings and an outline of

directions for further study.

## Chapter 2

## Related Work and Contributions

#### 2.1 Introduction

Several researchers have proposed various methods to reduce the reconfiguration time of an FPGA. Broadly speaking, these methods can be classified into five categories: partial reconfiguration based techniques, configuration compression, specialised FPGA architectures, configuration caching, and circuit scheduling and placement. These methods are discussed in detail below. The survey presented here is broad. Specific comparisons with the work of others are made in the body of the thesis.

## 2.2 Partial Reconfiguration

In early SRAM FPGAs, the user had to reload the entire contents of configuration memory each time a reconfiguration was performed. (e.g. XC4000 series FPGAs [127]). In such devices, reconfiguration time is constant and depends upon the device size. This *complete* reconfiguration approach is suited to cases where reconfiguration is infrequent, e.g. for field upgrades. The

main advantage of this model is that the underlying configuration memory requires a simple architecture, e.g. a scan chain. However, the reconfiguration time becomes a system bottleneck when applications demand frequent reconfiguration. Examples of such applications will be provided in Section 3.4 of this thesis.

Partial reconfiguration allows the user to selectively modify the contents of configuration memory. The XC6200 series devices were among the first to support this concept [128]. This device allows byte-level access to its memory. An XC6200 device has separate address and data pins. The host microprocessor controlling the reconfiguration views the FPGA as a special kind of random access memory. Several applications target XC6200 devices making use of its partial reconfigurability (e.g. [41, 130, 99]). The XC6200 device also offers a wildcarding mechanism through which the user can load the same configuration data to multiple rows of resources. Specialised algorithms have been developed to target this mechanism and have shown compression reduction of up to 70% for various benchmark circuits (e.g. [37]).

The XC6200 devices internally implemented their configuration memory similar to a conventional SRAM, i.e. using horizontal and vertical control wires to select the target byte-wide register. Chapter 3 shows that byte-wise access to configuration memory is a desirable feature but implementing the memory in a RAM-style manner to support this operation is inefficient for large, modern devices. Firstly, the amount of address data needed to access a register becomes significant and secondly, row and column decoders require additional hardware. It should be noted that algorithms that exploit wild-carding in XCV6200 assume that the device supports RAM-style access to its memory ([77]). Similar comments apply to the enhancements of XC6200 devices as presented in [16].

Virtex devices allow partial reconfiguration but the unit of configuration, called a *frame*, is 50-150 times larger than that of XC6200 devices and depends on the device size [123]. Chapter 3 shows that a large unit of configuration is undesirable from the perspective of reducing reconfiguration time and develops new techniques for accessing and modifying configuration data at smaller granularities. The implementation of these methods for Virtex is discussed in Chapter 4.

The successors of Virtex, Virtex-II [125] and Virtex-4 [124] FPGAs are also partially reconfigurable. The exact details of configuration memory in Virtex-II are obscure but it seems to have a larger unit of configuration compared to Virtex devices. The configuration unit of a Virtex-4 device has a fixed size across the family and is almost equal in size to the configuration unit of the largest Virtex device. More details on these devices are presented in Chapter 3.

The additional feature of Virtex-II and Virtex-4 FPGAs is that reconfiguration can be triggered and controlled from inside the device using an internal configuration access port (ICAP). In [5], a method whereby the frame data is internally read into a Block RAM (BRAM) and modified using software running on an on-chip processor is described. As a measure of reducing reconfiguration time, the read-modify-write method helps only if a frame can be read, modified and written back to its destination in less time than it takes the modification data to be loaded onto the device. In all Virtex devices, frames are sequentially read and written from the configuration port (ICAP simply provides an internal access to the configuration port). The method proposed in [5] reads an on-chip frame into a BRAM though ICAP and then writes back the modified data. Thus, irrespective of the time needed to modify a particular frame in a BRAM, it takes the same amount of time to send the frame back to its destination as to load a new frame afresh. While the method does not reduce reconfiguration time, it does allow self-reconfigurable systems to be implemented. Chapter 4 presents a read-modify-write method that does indeed lead to a reduction in reconfiguration time.

The concept of partial reconfiguration has been used to devise many techniques that attempt to reduce reconfiguration latency. One method, called configuration cloning, simply copies the contents of a part of a memory to another on-chip location [72]. The method assumes that an entire memory

row or a user-defined subset of a row can be broadcast across the selected area of the device in a vertical direction. It also assumes a similar mechanism for memory columns across the device. This technique can be regarded as another form of wildcarding. However, this method has not been shown to be effective for applications that target such general purpose devices as Virtex. The analysis presented in this thesis also suggests that the regularity that this method attempts to exploit is less likely to be present in real configuration data.

A somewhat different use of partial reconfiguration is made in a device model called a hyper-reconfigurable architecture [50]. Hyper-reconfigurability is defined as allowing the user to restrict the reconfiguration potential of the underlying FPGA and thus constrain the influence of the size of the configuration memory space. The user first defines a static configuration context (called hyper-reconfiguration) followed by one or more reconfigurations that assume that the device is in the configuration state defined during the hyper-reconfiguration step. It is not clear how hyper-contexts are defined, i.e. what encoding or user control is provided in the architecture to define hyper-contexts. Little work has been done to implement these concepts for real world FPGAs. Chapter 4 of this thesis examines various architectural issues that are relevant in this context.

## 2.3 Configuration Compression

The goal of compression techniques is to transform an input configuration into a compressed configuration of a smaller size. In the context of FPGAs, compression serves a dual purpose. The first purpose of compression is to save memory that is externally needed to store the configuration data for system boot-up. In the context of embedded systems, this means that less memory modules need to be placed on the circuit board, i.e. the system cost can decrease.

The second use of configuration compression is to reduce reconfiguration time. In contemporary FPGAs, configuration data is serially loaded onto the device and thus the data load time is directly proportional to the size of the bitstream. Compression can be applied to reduce the configuration size and hence the load time. If decompression is performed on-the-fly as new compressed data is being loaded then reconfiguration time can be reduced. Methods that perform this decompression before data is loaded onto the device do not reduce reconfiguration time (e.g. [122, 43]). In contrast, the focus of this thesis is on those methods that perform decompression after the compressed data is loaded onto the device. A reduction in transferred data is thereby translated into a corresponding reduction in reconfiguration time.

Several researchers have shown that configuration data corresponding to typical configurations can be compressed to various degrees. The method presented in [20] employes a dictionary-based method on a set of configurations targeting Virtex devices. The reductions in bitstream sizes range from 20% to 60%. The main problem with this approach is that it requires a significant amount of memory to store the dictionary needed by the hardware decompressor (in some cases almost double the size of the existing configuration memory).

The method presented in [53] applies LZ-based compression combined with a re-organisation of the input data to increase the amount of regularity that can be exploited. For a set of benchmark configurations on a Virtex devices, this method demonstrated 20% to 90% reductions in bitstream sizes. A hardware decompressor for this method is described in [75]. This system requires an internal cross-bar whose dimensions depend upon the device size thereby making it less scalable. Section 6.3 of this thesis shows that the quality of compression achieved with LZ is also likely to be lower than the methods proposed in this thesis. The method presented in [71] performs re-ordering of configuration data to enhance regularity. This method is also studied in Section 6.3 and is argued to be sub-optimal.

A different set of compression methods focuses on inter-configuration re-

dundancy. The work done in [46] shows that a large amount of the data present in a variety of Virtex configurations is identical at a bit level. The method suggested in [48] leverages this observation and applies run-length encoding on the differential configurations. A differential configuration simply consists of those bits in the configuration at hand that are different from the on-chip bits at the same location. These approaches are studied in detail in Chapters 3, 4 and 6. It is argued that the above approaches are less efficient than those that focus on compressing each configuration in isolation.

The work presented in this thesis takes into account such hardware issues as the scalability of the hardware decompressor with respect to the device size and the configuration port size. Moreover, considerable attention is paid to measuring the information content of typical circuit configurations in order to assess the quality of various compression techniques and to predict their performance. The author is not aware of any previous study in these directions.

## 2.4 Specialised Architectures

Multi-context FPGAs contain more than one configuration memory plane [94, 11, 86, 16]. At any point in time, only one plane is active. Configuration data can be written to inactive contexts in the background and the device can later be reconfigured by switching the active memory plane with the inactive plane. Ideally, the FPGA can be reconfigured in one cycle. This model has been extensively researched but seems to have dropped out of favour for fine-grained architecture (it has found some applications in coarse-grained FPGAs though [110]). The author believes that the main reason for the demise of this model for fine-grained FPGAs is that it significantly increases the area needed to implement configuration memory. From the perspective of most commercial FPGA users, this area is preferably used to increase the density of the logic and routing blocks.

Architectural techniques such as pipelined reconfiguration [80] and wormhole reconfiguration [74] are only applicable to specialised FPGA architectures and are thus not relevant to the present thesis.

## 2.5 Configuration Caching

Configuration caching refers to a technique that attempts to retain the configuration fragments that are already present on the device in order to construct later circuits. Several cache management schemes have been presented in the literature that attempt to increase the efficiency of the cache [52, 78]. These methods assume such target machines as Garp [40] and Chimaera [36]. These machines view FPGA as a tightly-coupled co-processor executing special instructions (that correspond to circuit configurations on the FPGA). These instructions are assumed to be relocatable on the device and the main focus is on the cache *eviction* strategies. In contrast, this work focuses on a level below the level of configuration caching. However, Chapter 4 does study the impact of placing various circuit cores relative to each other in such a manner so as to increase the amount of configuration overlap. This is again different from the work on configuration caching where no attempt is made to find regularities between the configurations that correspond to successive instructions.

## 2.6 Circuit Scheduling and Placement

Circuit scheduling refers to a set of techniques that define the order in which the target FPGA is to be reconfigured to realise various circuits. Configuration placement refers to defining the final physical placement of the circuit modules on the device. Both techniques are inter-related and have been extensively studied (e.g. [95, 28, 93, 25, 90, 54, 15, 2, 70, 21, 44]). The reported methods operate on various device architectures and at various stages

of design flow. Section 3.3 of this thesis presents a typical design flow and discusses the opportunities of reducing reconfiguration time at each level. In the context of circuit scheduling and placement, the contribution of this thesis is that it examines the issue of circuit ordering and placement at the configuration data level and explores the opportunities of reducing reconfiguration time.

## 2.7 Summary

It is difficult to compare the impact of the various techniques mentioned in this chapter because the target architectures and the chosen benchmarks vary as well. This thesis makes an attempt to assess the performance of a set of techniques with a large set of benchmarks that cover many of those used to derive prior results. Moreover, it examines in detail the dependence of these techniques on the relevant characteristics of the underlying FPGA architecture. In summary, the research described in this thesis draws its inspiration from a variety of research threads and develops a theory of the structure of configuration data. This understanding is employed to develop efficient reconfiguration mechanisms at the FPGA configuration memory system level.

## Chapter 3

# Models and Problem Formulation

#### 3.1 Introduction

This chapter provides necessary background for the rest of the thesis and formulates the problem of reducing reconfiguration time of an FPGA at its configuration data level. Section 3.2 discusses various FPGA hardware platforms and outlines the model assumed later in this thesis. Various programming environments for these platforms are then discussed in Section 3.3 followed by a set of examples of runtime reconfigurable applications in Section 3.4. These examples show that large reconfiguration latencies of current generation FPGAs adversely affect the performance of these applications. In the light of this discussion, Section 3.5 formulates the problem of reducing reconfiguration time at the configuration data level of the device.

#### 3.2 Hardware Platforms

This section introduces the model of FPGA hardware that is used for the rest of this thesis. Section 3.2.1 outlines the internal structure of the target

FPGA. Section 3.2.2 describes various schemes by which the model FPGA is typically integrated with other components, such as a microprocessor, to form a reconfigurable computing platform.

#### 3.2.1 The device model

Fine-grained, island style FPGAs have become popular [4] and have found their use in many application domains. The term *fine-grained* refers to the size of the logic unit of the device while the term *island-style* implies that the interconnect consists of a mesh of wires. FPGAs with coarse-grained logic units [35], such as ALUs, have also been used to accelerate several applications (e.g. [19]). However, fine-grained FPGAs allow greater flexibility in programming. The downside of this is long reconfiguration delays since far greater control over resources is provided. The aim of this work is to study the potential and limitations of this model so as to lead the way for a future study on coarse-grained FPGAs.

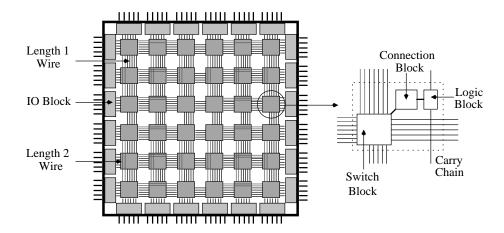

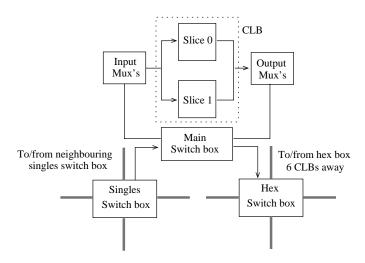

A fine-grained, island style SRAM-based FPGA consists of an array of basic blocks that are connected together by a hierarchical mesh of wires (Figure 3.1). The figure shows a two-level network in which neighbouring basic blocks are connected together using length 1 wires. Length-2 wires bypass one adjacent block and form the second level of interconnect. A ring of IO blocks surrounds the array for external connectivity. Commercial devices contain many more features such as distributed blocks of RAM, special function units such as multipliers, analog to digital converters etc. For the sake of generality and tractability, these are ignored in this work.

Each basic block of the model FPGA can be divided into three subblocks. A *logic block* contains combinational and sequential logic that can be configured to realise boolean functions of varying complexity. The logic block is connected to a *switch block* via a *connection block*. Together they form the routing infrastructure of the device. The switch blocks are connected to each other via the mesh network. As switches can also be configured, larger

**Figure 3.1:** A generic island-style FPGA. A basic block is enlarged to show its internal structure.

circuits can be formed by connecting together various logic blocks. Special wires, such as *carry chains* bypass the switched network and directly connect the neighbouring logic blocks. This allows faster connections for arithmetic circuits such as adders. Every FPGA contains programmable clocks that can generate signals of various rates. On-chip clock distribution networks allow connectivity between the system clock and individual logic blocks.

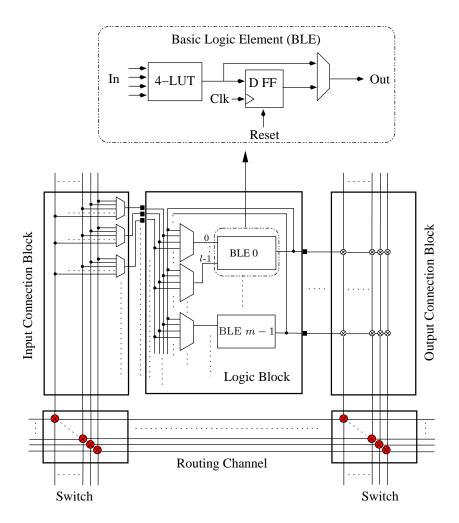

Figure 3.2 shows the internal details of a logic block and its connectivity with the routing architecture. A logic block can be modelled as consisting of a number, m, of basic logic elements (BLEs) [4]. Each BLE contains an l-input Look-up-table (LUT), a one-bit register and a multiplexor to select either the output of the LUT or of the register. The LUT shown in the BLE of Figure 3.2 can implement any boolean function of four inputs (i.e. l=4). The inputs to each LUT can arrive either from the routing channel or from the output of the other LUTs (i.e. feedback connections). A set of multiplexors that are internal to the logic block allow these connections to be made by the FPGA programmer. The LUTs are implemented as multiplexor trees with inputs coming from the configuration SRAM cells.

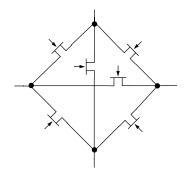

The switch, connection and IO blocks allow communication between the logic blocks and off-chip systems. Associated with each logic block is a switch

Figure 3.2: The internal architecture of the model FPGA.

block that allows arbitrary connection with the network of wires. While such a switch can be modelled as a cross-bar of a certain size, in practice it is quite sparse and allows only a small subset of connections to be made. There exists several types of switches. This work focuses on the disjoint-, or subset-based switch that is found in many commercial devices. This switch will be described later in this section. The connection block associated with a logic block consists of multiplexors that allow arbitrary inter-connection between the wires incident on the switch and the IO of the logic block. In practice, connection blocks are also quite sparse. The control signals to the connection block multiplexor arrive from the configuration SRAM. The input/output blocks connect the arrays with the external pins. These blocks can support various signalling standards and may contain such features as analog to digital converters and serial to parallel shifters.

The entire FPGA can be programmed, or configured, by writing CAD-generated configuration data to its configuration SRAM. The circuit to be implemented on an FPGA is usually described in a high-level parallel programming language augmented with constructs to describe hardware features such as Handle-C [106], hardware description languages such as VHDL/Verilog or graphical languages such as schematics. The CAD tools then automatically transform the input circuit description into a circuit netlist and then into physically mapped configuration data for the target device. This data consists of three components. The first component consists of instructions for the memory controller such as read or write. The second component consists of the register addresses. The last component is the data that will actually reside in the configuration registers. The entire bitstream is serially shifted into the array via a configuration port.