# Repairing FPGA Configuration Memory Errors using Dynamic Partial Reconfiguration

# Nguyen Tran Huu Nguyen

A thesis in fulfillment of the requirements for the degree of

Doctor of Philosophy

School of Computer Science and Engineering

Faculty of Engineering

The University of New South Wales

November 2017

#### THE UNIVERSITY OF NEW SOUTH WALES Thesis/Dissertation Sheet

Surname or Family name: Nguyen

First name: Tran Huu Nguyen Other name/s:

Abreviation for degree as given in the University calendar:  $\ensuremath{\textbf{PhD}}$

School: School of Computer Science and Engineering

Faculty: Faculty of Engineering

Title: Repairing FPGA Configuration Memory Errors using Dynamic Partial Reconfiguration

Abstract

The configuration memory of SRAM-based *Field-Programmable Gate Arrays* (FPGAs) is susceptible to radiation-induced *Single Event Upsets* (SEUs). This has limited their adoption for space applications and led to intensive research to discover techniques for mitigating the radiation effects in such devices.

The reliability of FPGA user circuits is commonly improved by applying *Triple Modular Redundancy* (TMR), whereas configuration memory errors are corrected by reloading a golden bitstream for the design. Two approaches have emerged for doing so. The first, known as scrubbing, periodically refreshes the configuration memory of the entire device. The second makes use of dynamic partial reconfiguration to reload the configuration of an individual circuit module that has been found to be in error. This latter approach, which we refer to as *Module-based Error Recovery* (MER) holds promise for being more responsive and needing less energy than scrubbing, at the cost of greater implementation complexity.

The research work reported in this thesis aims to clarify the design, and improve the reliability of FPGA systems that employ TMR with MER. The research has involved studying and contributing to the development of several aspects of TMR-MER infrastructure, most notably, the design of reliable *Reconfiguration Control Networks* (RCNs) for conveying reconfiguration requests to a central reconfiguration controller, new reliability models for TMR-MER systems and improved scheduling techniques to check for faulty modules.

This thesis evaluates the impact of RCNs on system reliability and performance. Results show that a "hard RCN" is the most reliable despite having the highest network latency. As the order in which voters are checked for errors over the RCN has an impact on overall system reliability, this thesis then proposes a *Voter Scheduling Engine* (VSE) for dynamically prioritizing the TMR component to be checked next. This thesis proposes reliability models for TMR-MER systems suffering multiple SEUs and employing round-robin or *Variable-Rate Voter Checking* (VRVC) and proposes the use of a genetic algorithm to determine a static schedule for maximizing the system reliability. Simulation results indicate that the mean time to failure of TMR-MER systems employing VRVC is up to 400% greater than when the usual round robin is used to check components for errors.

The thesis concludes with directions for further study.

#### Declaration relating to disposition of project thesis/dissertation

I hereby grant to the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or in part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all property rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstracts International (this is applicable to doctoral theses only).

#### Signature Nguyen Tran Huu Nguyen

Witness Oliver Diessel

Date 13 Nov, 2017

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years must be made in writing. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

FOR OFFICE USE ONLY

Date of completion of requirements for Award

## **Originality Statement**

I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.

Nguyen Tran Huu Nguyen 13 Nov, 2017

## **Copyright Statement**

I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only).

I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation.

Nguyen Tran Huu Nguyen 13 Nov, 2017

## Authenticity Statement

I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.

Nguyen Tran Huu Nguyen 13 Nov, 2017

# Abstract

The configuration memory of SRAM-based *Field-Programmable Gate Arrays* (FPGAs) is susceptible to radiation-induced *Single Event Upsets* (SEUs). This has limited their adoption for space applications and led to intensive research to discover techniques for mitigating the radiation effects in such devices.

The reliability of FPGA user circuits is commonly improved by applying *Triple Modular Redundancy* (TMR), whereas configuration memory errors are corrected by reloading a golden bitstream for the design. Two approaches have emerged for doing so. The first, known as scrubbing, periodically refreshes the configuration memory of the entire device. The second makes use of dynamic partial reconfiguration to reload the configuration of an individual circuit module that has been found to be in error. This latter approach, which we refer to as *Module-based Error Recovery* (MER) holds promise for being more responsive and needing less energy than scrubbing, at the cost of greater implementation complexity.

The research work reported in this thesis aims to clarify the design, and improve the reliability of FPGA systems that employ TMR with MER. The research has involved studying and contributing to the development of several aspects of TMR-MER infrastructure, most notably, the design of reliable *Reconfiguration Control Networks* (RCNs) for conveying reconfiguration requests to a central reconfiguration controller, new reliability models for TMR-MER systems and improved scheduling techniques to check for faulty modules.

This thesis evaluates the impact of RCNs on system reliability and performance. Results show that a "hard RCN" is the most reliable despite having the highest network latency. As the order in which voters are checked for errors over the RCN has an impact on overall system reliability, this thesis then proposes a *Voter Scheduling Engine* (VSE) for dynamically prioritizing the TMR component to be checked next. This thesis proposes reliability models for TMR-MER systems suffering multiple SEUs and employing round-robin or *Variable-Rate Voter Checking* (VRVC) and proposes the use of a genetic algorithm to determine a static schedule for maximizing the system reliability. Simulation results indicate that the mean time to failure of TMR-MER systems employing VRVC is up to 400% greater than when the usual round robin is used to check components for errors.

The thesis concludes with directions for further study.

# Acknowledgements

As with any great endeavour, this thesis would not have been possible to complete without the help and support of many others. First and foremost, I would like to express my sincere gratitude to my supervisor, Associate Professor Oliver Diessel. His supervision and expert knowledge have added considerably to my research work. He has also significantly changed my style of thinking in research, and in writing scientific papers. The inherently readerresponsible thinking of a South-East Asian guy has caused me trouble to produce clear, concise and writer-responsible papers. Therefore, with each draft I wrote, Oliver put great effort, not only into commenting on the strengths and the drawbacks, fixing tons of grammar errors and re-wording paragraphs that were not clear, but also in inspiring me in the direction of writing, and suggesting me to read relevant books such as "How to Write and Publish a Scientific Paper" by Robert Day to improve my writing skills. Moreover, I usually found a relief after many meetings we sat together. Perhaps, this was because during every meeting. Oliver's guidance and advice helped me see my research problem clearer. He also encouraged me to express thoughts in the context of an overall big picture and to emphasize WHY instead of HOW. With his support, I have also had many chances to be a demonstrator and a tutor of undergraduate courses. These helped me gain not only teaching experience, but also confidence in speaking in front of a group of students. After all, I deeply appreciate his kindness, patience and continuous guidance throughout my Ph.D. candidature.

I would like to express my gratitude to my co-supervisor, Dr. Ediz Cetin, who helped me discuss my research along with Oliver and reviewing my papers before I submitted them. I would also like to thank my colleagues: Dimitris Agiakatsikas, Zhuoran (Reimond) Zhao, Tong Wu, Lingkan (George) Gong, and Alexander Kroh. They have helped me in one way or another at different periods of time during my 3-year Ph.D. candidature. I would also like to thank my annual progress review panel, including Dr. Hui Annie Guo, Professor Andrew Dempster and Dr. Jorgen Peddersen, who gave me many suggestions on planning my thesis.

I would like to thank my wife, Nguyet Tran, for her love, sympathy and patience during this work. While I was away from home, she went through difficult times without me - the last 6 months of her pregnancy before giving birth to our daughter, raising our daughter, earning money for living and doing her Ph.D. as well, to name just a few. Despite these difficulties, she has been supportive and understanding during my Ph.D. candidature.

Both my wife and daughter have also been an inspiration for me to do better and be better. Of course, I would also like to thank my father-in-law (Nghia Tran), mother-inlaw (Tuyet Nguyen), sister-in-law (Tuong Tran), and brother-in-law (Khanh Tran), who have always supported my wife in raising our daughter. This allowed me to worry less about my wife and daughter, and helped me focus on finishing my thesis.

Without a doubt, gratitude must also be expressed to my Mum (Lai Tran), Dad (Tri Nguyen) and my younger brother (Duc Nguyen). I am so grateful for the support and love they have continually expressed and shown me. My parents have also pushed me to do my best and pulled me along when I needed help. Even if they may not understand this thesis, they are proud of me as they have always been.

Finally, I would like to thank the University of New South Wales, Sydney for the Tuition Fee Scholarship (TFS) and the Research Stipend. Thanks also to the School of Computer Science and Engineering and the Australian Centre for Space Engineering Research (ACSER) for international conference travel funding.

# Contents

| A             | cknov | wledge | ements                          |   |   | iv  |

|---------------|-------|--------|---------------------------------|---|---|-----|

| C             | onter | nts    |                                 |   |   | vi  |

| Li            | st of | Figure | es                              |   |   | xi  |

| Li            | st of | Table  | s                               |   | x | civ |

| $\mathbf{Li}$ | st of | Abbre  | eviations                       |   | x | vi  |

| 1             | Intr  | oducti | ion                             |   |   | 1   |

|               | 1.1   | Why S  | SRAM-based FPGAs in Space?      | • |   | 1   |

|               | 1.2   | Scope  | and Objectives                  |   |   | 3   |

|               |       | 1.2.1  | Scope                           |   |   | 3   |

|               |       | 1.2.2  | Objectives                      |   |   | 5   |

|               | 1.3   | Thesis | s Contributions                 |   |   | 7   |

|               |       | 1.3.1  | Reconfiguration Control Network | • |   | 7   |

|               |       | 1.3.2  | Voter Scheduling Engine         |   |   | 7   |

|               |       | 1.3.3  | Variable-Rate Voter Checking    |   |   | 8   |

|               | 1.4   | Public | cations                         |   |   | 9   |

|               |       | 1.4.1  | Journal Papers                  |   |   | 9   |

|          |     | 1.4.2  | Conference Papers                                           | 9  |

|----------|-----|--------|-------------------------------------------------------------|----|

|          |     | 1.4.3  | Technical Reports                                           | 10 |

|          | 1.5 | Thesis | Outline                                                     | 11 |

| <b>2</b> | Bac | kgrour | nd and Related Work                                         | 12 |

|          | 2.1 | Radiat | tion Effects on SRAM-based FPGAs                            | 13 |

|          | 2.2 | Radiat | tion Environments                                           | 15 |

|          |     | 2.2.1  | Space Environments                                          | 16 |

|          |     | 2.2.2  | Terrestrial Environments                                    | 16 |

|          |     | 2.2.3  | High-Energy Physics Experiments                             | 17 |

|          | 2.3 | SRAM   | FPGA Architectural Vulnerabilities                          | 18 |

|          |     | 2.3.1  | Configuration Memory                                        | 20 |

|          |     | 2.3.2  | Block RAMs                                                  | 22 |

|          |     | 2.3.3  | User Flip-flops                                             | 22 |

|          |     | 2.3.4  | Internal Proprietary State                                  | 23 |

|          |     | 2.3.5  | Final Remarks on FPGA Architectural Vulnerabilities         | 23 |

|          | 2.4 | Mitiga | ting SEUs in SRAM FPGAs                                     | 24 |

|          |     | 2.4.1  | Terminology                                                 | 24 |

|          |     | 2.4.2  | Hardware Redundancy                                         | 25 |

|          |     | 2.4.3  | Dynamic Partial Reconfiguration                             | 26 |

|          |     | 2.4.4  | Error Correction Code for Block RAM Memories                | 28 |

|          |     | 2.4.5  | Flip-flop Mitigation                                        | 29 |

|          |     | 2.4.6  | System-level Mitigation                                     | 29 |

|          |     | 2.4.7  | Final Remarks in Mitigating SEUs on SRAM FPGAs              | 30 |

|          | 2.5 | TMR-   | Scrubbing and TMR-MER Overview                              | 30 |

|          | 2.6 | Relate | d Work on Novel Techniques for Improving System Reliability | 33 |

|   | 2.7             | Measu   | ring FPGA SEU Sensitivity                          | 34 |

|---|-----------------|---------|----------------------------------------------------|----|

|   |                 | 2.7.1   | Fault insertion                                    | 38 |

|   |                 | 2.7.2   | Input Stimulation                                  | 39 |

|   |                 | 2.7.3   | Error Detection                                    | 39 |

|   |                 | 2.7.4   | Error Clearance                                    | 40 |

|   |                 | 2.7.5   | Final Remarks on Measuring FPGA SEU Sensitivity    | 40 |

|   | 2.8             | Reliab  | ility Model                                        | 40 |

|   | 2.9             | Summ    | ary                                                | 43 |

| 3 | $\mathbf{Reli}$ | iable T | MR-MER System Model                                | 44 |

|   | 3.1             | A TM    | R Component                                        | 45 |

|   | 3.2             | Recon   | figuration Controller                              | 48 |

|   |                 | 3.2.1   | Commonly Used Reconfiguration Controllers          | 49 |

|   |                 | 3.2.2   | High Performance Reconfiguration Controllers       | 50 |

|   |                 | 3.2.3   | Reliable Reconfiguration Controllers               | 51 |

|   |                 | 3.2.4   | Programmable Configuration Controllers             | 51 |

|   | 3.3             | Recon   | figuration Control Networks                        | 53 |

|   |                 | 3.3.1   | RCN Survey                                         | 54 |

|   |                 | 3.3.2   | RCN Architecture                                   | 55 |

|   |                 | 3.3.3   | Fault Emulation System                             | 60 |

|   |                 | 3.3.4   | Reliability Evaluation                             | 62 |

|   |                 | 3.3.5   | Experiments and Results                            | 63 |

|   |                 | 3.3.6   | Final Remarks for Reconfiguration Control Networks | 69 |

|   | 3.4             | Summ    | ary                                                | 70 |

| 4 | Dyı | namic   | Scheduling of Voter Checks in TMR-MER Systems                                        | <b>71</b> |

|---|-----|---------|--------------------------------------------------------------------------------------|-----------|

|   | 4.1 | Sched   | uling Voter Checks                                                                   | 72        |

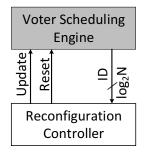

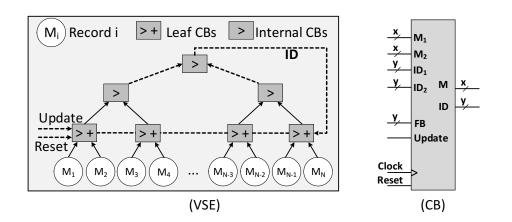

|   |     | 4.1.1   | Voter Scheduling Engine (VSE)                                                        | 72        |

|   |     | 4.1.2   | VSE Implementations                                                                  | 75        |

|   | 4.2 | Exper   | imental Analysis                                                                     | 76        |

|   |     | 4.2.1   | Experiments                                                                          | 77        |

|   |     | 4.2.2   | Results                                                                              | 78        |

|   | 4.3 |         | Remarks on Dynamic Scheduling of Voter Checks in TMR-MER Sys-                        | 82        |

| 5 | Sta | tic Sch | neduling of Voter Checks in TMR-MER Systems                                          | 83        |

|   | 5.1 | Relia   | bility Model                                                                         | 85        |

|   |     | 5.1.1   | General Reliability Model                                                            | 86        |

|   |     | 5.1.2   | Failure Rates of TMR-MER Systems in which Voters are Checked<br>in Round-Robin Order | 88        |

|   |     | 5.1.3   | Failure Rates of TMR-MER Systems Employing VRVC                                      | 94        |

|   | 5.2 | Simul   | ating a 2-Component System                                                           | 100       |

|   | 5.3 | Sched   | uling Voter Checks                                                                   | 101       |

|   |     | 5.3.1   | Genetic Algorithm                                                                    | 102       |

|   |     | 5.3.2   | Scheduling of Voter Checks                                                           | 104       |

|   |     | 5.3.3   | Mean Time To Detect Errors                                                           | 105       |

|   |     | 5.3.4   | Power Consumption                                                                    | 105       |

|   | 5.4 | Simul   | ations                                                                               | 106       |

|   |     | 5.4.1   | Assumptions and Implementation                                                       | 106       |

|   |     | 5.4.2   | Results and Discussion                                                               | 107       |

|   | 5.5 | Exper   | imental Analysis                                                                     | 109       |

|   |     | 5.5.1   | Experiments                                                                          | 109       |

|                           |       | 5.5.2                | Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11 |

|---------------------------|-------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                           |       | 5.5.3                | Further Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13 |

|                           | 5.6   | Final ]              | Remarks on Static Scheduling of Voter Checks in TMR-MER Systems 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

| 6                         | Con   | clusio               | ns 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16 |

|                           | 6.1   | Conclu               | ıding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16 |

|                           | 6.2   | Future               | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

|                           |       | 6.2.1                | Criticality-aware Scheduling of Voter Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19 |

|                           |       | 6.2.2                | Adaptive Scheduling of Voter Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19 |

|                           |       | 6.2.3                | Pre-empting the Recovery of Less Critical Components to Recover<br>Errors in More Critical Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

| $\mathbf{A}_{\mathbf{j}}$ | ppen  | $\operatorname{dix}$ | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21 |

|                           | A.1   | The Q                | B50 RUSH Payload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21 |

|                           | A.2   | TMR-                 | MER Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24 |

|                           |       | A.2.1                | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24 |

|                           |       | A.2.2                | TMR Components    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . | 26 |

|                           |       | A.2.3                | MicroBlaze Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29 |

|                           |       | A.2.4                | MCU Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30 |

|                           | A.3   | Design               | Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

|                           |       | A.3.1                | Floor-planning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

|                           |       | A.3.2                | Full Bitstream and Partial Bitstream Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31 |

|                           | A.4   | Resour               | rce Utilization and Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

|                           | A.5   | Summ                 | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

| Re                        | efere | nces                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35 |

# List of Figures

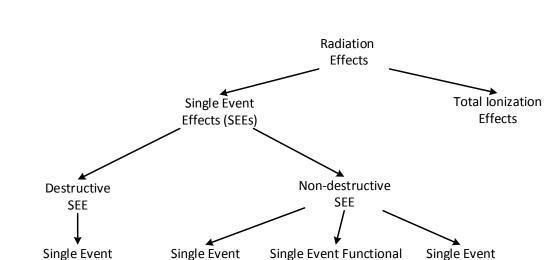

| 2.1  | Common radiation effects on digital circuits [146]                                                                        | 14 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

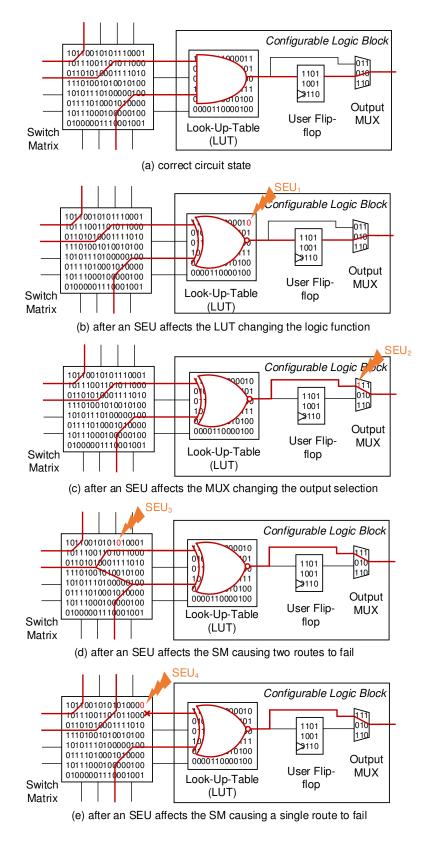

| 2.2  | Examples of SEU effects on different types of logic cells $[11, 61, 136]$                                                 | 21 |

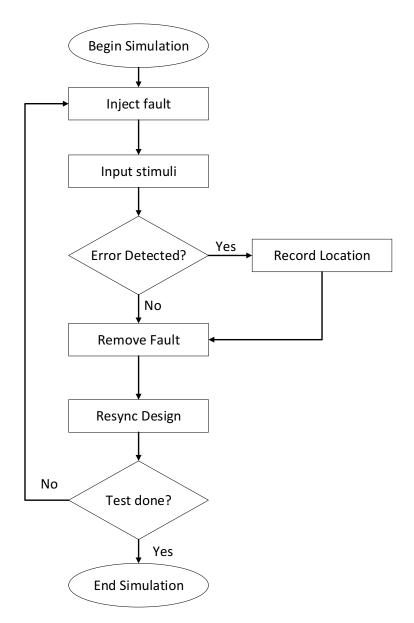

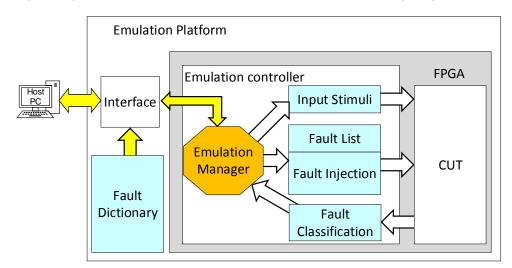

| 2.3  | Basic emulation-based fault injection algorithm $[75, 133]$                                                               | 36 |

| 2.4  | Autonomous Emulation System [47]                                                                                          | 37 |

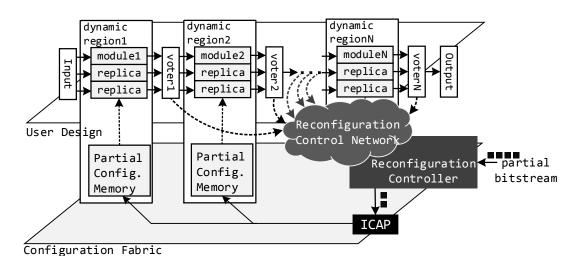

| 3.1  | An example TMR-MER system diagram                                                                                         | 45 |

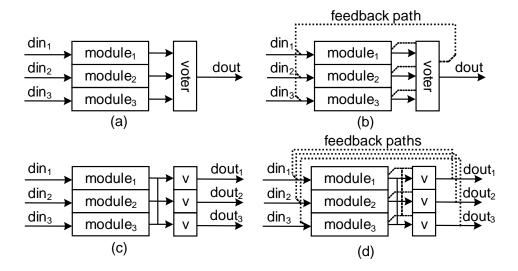

| 3.2  | Triple Modular Redundancy                                                                                                 | 46 |

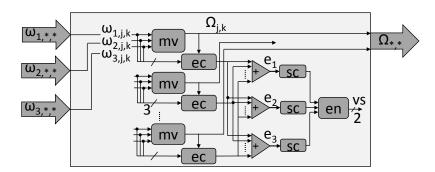

| 3.3  | Voter internal structure                                                                                                  | 47 |

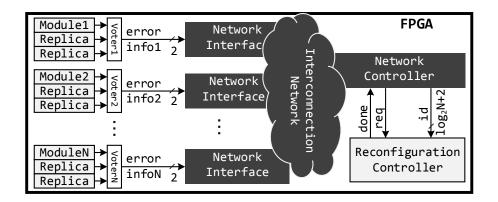

| 3.4  | Components of an RCN                                                                                                      | 56 |

| 3.5  | The architecture of a star network                                                                                        | 56 |

| 3.6  | The architecture of a bus network                                                                                         | 57 |

| 3.7  | The architecture of a token ring network                                                                                  | 57 |

| 3.8  | Extract of a Xilinx logic allocation file                                                                                 | 59 |

| 3.9  | Fault injection flowchart                                                                                                 | 61 |

| 3.10 | RePin architecture for input stimulus                                                                                     | 61 |

| 3.11 | Synthetic layout of a 31-voter design                                                                                     | 64 |

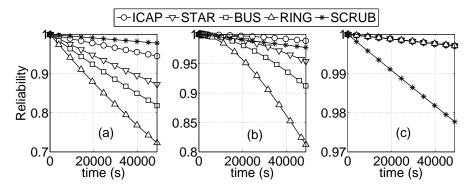

| 3.12 | Reliability of RUSH payload using (a) Unprotected RCN, (b) TMR triplicated RCN, and (c) TMR triplicated RCN with recovery | 68 |

| 4.1  | Example of component records changing places                                                                              | 74 |

| 4.2 | Interface between the VSE and the RC                                                                                                                                                                                                                                                                         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3 | (a) VSE and (b) Conditional Block interface                                                                                                                                                                                                                                                                  |

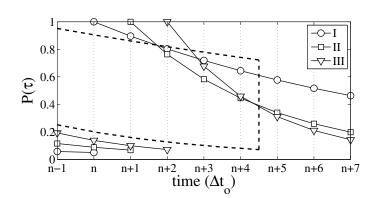

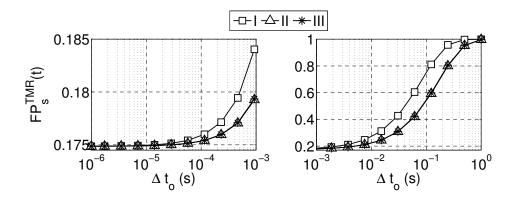

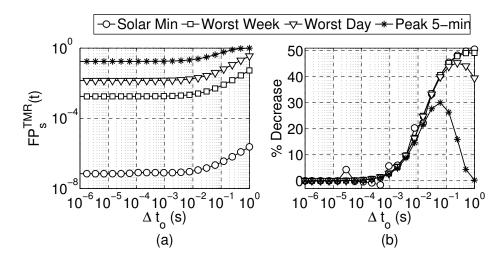

| 4.4 | Failure probabilities of the three configurations in GEO orbit at the peak 5-min condition during a mission of 30 days                                                                                                                                                                                       |

| 4.5 | (a): Failure probabilities of configuration III with four radiation conditions<br>in GEO orbit during a 30-day mission, (b) Percentage decrease in the prob-<br>ability of failure in configuration III versus configuration I                                                                               |

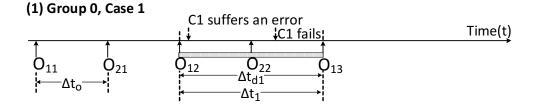

| 5.1 | Failure mode for component 1 in two-component systems in which the voters are checked in round-robin order                                                                                                                                                                                                   |

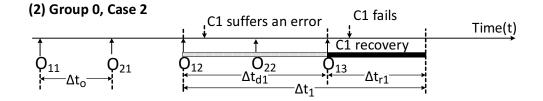

| 5.2 | Failure of component 1 in systems employing variable-rate voter checking $.95$                                                                                                                                                                                                                               |

| 5.3 | $\Delta t_{dkf}^g$ when $f > k$ and $g = 1$                                                                                                                                                                                                                                                                  |

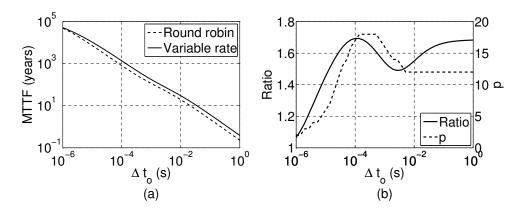

| 5.4 | (a) MTTF (years) of the VRVC and round-robin voter checking approaches.<br>(b) Peak MTTF ratio achieved when varying the voter checking rate relative<br>to checking voters in round-robin order, and the corresponding rate $p$ at<br>which C2 is checked relative to C1 to achieve the peak MTTF ratio 101 |

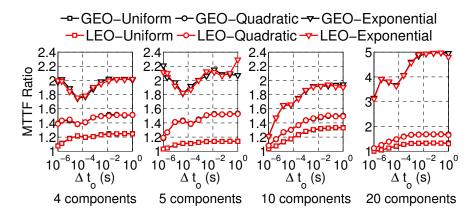

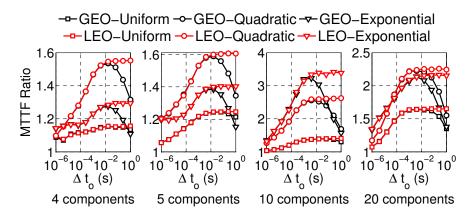

| 5.5 | Average ratios of MTTFs for VRVC to those for round robin for systems consisting of 4, 5, 10 and 20 components in LEO (red) and GEO (black plots)108                                                                                                                                                         |

| 5.6 | Average ratios of MTTFs for VRVC to those for VSE for systems consisting of 4, 5, 10, and 20 components for LEO (red) and GEO (black plots) 108                                                                                                                                                              |

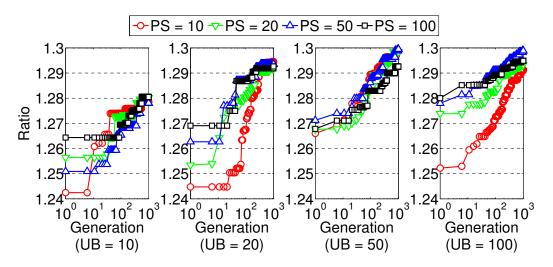

| 5.7 | Ratio of MTTF for VRVC to MTTF for round robin for the exemplar system while the number of generations, the population size (PS), and the upper bound (UB) of the initial check rate is varied                                                                                                               |

| A.1 | UNSW-EC0 CubeSat Structure                                                                                                                                                                                                                                                                                   |

| A.2 | High level block diagram of RUSH payload                                                                                                                                                                                                                                                                     |

| A.3 | High level block diagram of TMR-MER payload                                                                                                                                                                                                                                                                  |

| A.4 | A single accumulator FIR block diagram                                                                                                                                                                                                                                                                       |

| A.5 | BAQ architecture                                                                                                                                                                                                                                                                                             |

| A.6 | Binary Search Tree Architecture                                                                                                                                                                                                                                                                              |

| A.7 | Shift Register Architecture                                                                                                                                                                                                                                                                                  |

| A.8  | Simplified 7-Series Xilinx FPGA layout showing two configuration rows and resources distributed across columns |

|------|----------------------------------------------------------------------------------------------------------------|

| A.9  | The layout of a full bitstream and partial bitstreams in the external flash memory                             |

| A.10 | ) System layout of RUSH payload                                                                                |

# List of Tables

| 2.1 | Memory bits within the Artix-7 XC7A200T Xilinx FPGA                                               |

|-----|---------------------------------------------------------------------------------------------------|

| 2.2 | Bit failure rates in different orbits [67]                                                        |

| 3.1 | Results of mapping four RCNs to a Xilinx Artix-7 XC7A200TFBG-484 65                               |

| 3.2 | Fault injection results                                                                           |

| 3.3 | Results of mapping 9 TMR components to a Xilinx Artix-7 XC7A200TFBG-      484    67               |

| 4.1 | Configurations for the second set of experiments                                                  |

| 4.2 | Area and performance of the VSE mapped to a Xilinx Artix-7 XC7A200TFBG-         484 FPGA       78 |

| 4.3 | Results of mapping 10 TMR components to a Xilinx Artix-7 XC7A200TFBG-484 FPGA79                   |

| 4.4 | Failure probabilities of the three configurations when $\Delta t_o = 10 \text{ ms} \dots 82$      |

| 5.1 | Notation                                                                                          |

| 5.2 | Results of mapping 9 TMR components to a Xilinx Artix-7 XC7A200TFBG-484 FPGA110                   |

| 5.3 | MTTF and power consumption at various RC clock frequencies in GEO $$ 112                          |

| 5.4 | Average number of errors found in components                                                      |

| 5.5 | Mean time to detect errors                                                                        |

| A.1 | Results of mapping 9 TMR components to a Xilinx Artix-7 XC7A200<br>TFBG- $$ |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | 484                                                                         | 133 |

| A.2 | Results of mapping the MBS to a Xilinx Artix-7 XC7A200TFBG-484              | 134 |

# List of Abbreviations

**ADC** Analog to Digital Converter ASIC Application–Specific Integrated Circuit **ASIP** Application–Specific Instruction Set Processor **AXI** Advanced eXtensible Interface **BAQ** Block Adaptive Quantizer **BST** Binary Search Tree CAD Computer Aided Design **CB** Conditional Block **CF** Configuration Frame **CLB** Configurable Logic Block **CMOS** Complementary Metal Oxide Semiconductor **COTS** Commercial, Off-The-Shelf **CRC** Cyclic Redundancy Check **CUT** Component Under Test **DCM** Digital Clock Manager **DICE** Dual Interlocked storage CEll **DMA** Direct Memory Access **DMAC** Direct Memory Access Controller **DPR** Dynamic Partial Reconfiguration **DSP** Digital Signal Processing **DUT** Design Under Test

- $\mathbf{ECC}\xspace$  Error Correcting Code

- **ESA** European Space Agency

- FF Flip-Flop

- **FIR** Finite Impulse Response

- FIFO First-In, First-Out

- FMER Frame- and Module-based Error Recovery

- FPGA Field Programmable Gate Array

- FP European Union Framework Programme

- ${\bf FSM}\,$  Finite State Machine

- ${\bf GA}\,$  Genetic Algorithm

- GCR Galactic Cosmic Ray

- GEO Geostationary Earth Orbit

- GPIO General Purpose Input/Output

- **GPS** Global Positioning System

- **HEP** High–Energy Physics

- HWICAP AXI Hardware Internal Configuration Access Port

- **IC** Integrated Circuit

- ICAP Internal Configuration Access Port

- **INT** INTerconnect column

- **IOB** Input/Output Block

- **IP** Intellectual Property

- **ITAR** International Traffic in Arms Regulations

- **JPL** Jet Propulsion Laboratory

- JTAG Join Test Action Group

- ${\bf LEO}\,$  Low Earth Orbit

- LHC Large Hadron Collider

- ${\bf LUT}$ Look–Up Table

- MAC Multiply ACcumulator

**MB** MicroBlaze **MBS** MicroBlaze System MBU Multiple–Bit Upset MCU Multiple-Cell Upset; Microcontroller Unit **MIU** Multiple–Independent Upset MTTD Mean Time To Detect(ion) **MTTF** Mean Time To Fail(ure) **MTTR** Mean Time To Recover(y) **NA** Network Arbiter NC Network Controller **NI** Network Interface **NP** Non–deterministic Polynomial time **NRE** Non–Recurring Engineering **OBC** On–Board Computer **OTP** One–Time Programmable **PC** Personal Computer PCAP Processor Configuration Access Port PCC Programmable Configuration Controller **PCIe** PCI Express **PIP** Programmable Interconnection Point **PLL** Phase Lock Loop **PS** Population Size **RAM** Random Access Memory **RbC** Readback Capture **RbV** Readback Verify **RC** Reconfiguration Controller **RCN** Reconfiguration Control Network Rdone Reconfiguration done

**RHBD** Radiation–Hardened By Design

**RR** Reconfiguration Request

- **RTVP** Response Time Variability Problem

- **RUSH** Rapid recovery from SEUs in Reconfigurable Hardware

- **R/W** Read/Write

- ${\bf VKI}$ Von Karman Institute

- $\mathbf{VRVC}$ Variable–Rate Voter Checking

- **VSE** Voter Scheduling Engine

- SAA South Atlantic Anomaly

- **SAR** Synthetic Aperture Radar

$\mathbf{SD}$  Standard Deviation

- **SECDED** Single Error Correction, Double Error Detection

- **SEFI** Single–Event Functional Interrupt

- **SEL** Single Event Latch–up

- ${\bf SEM}$  Soft Error Mitigation

- **SEP** Single Event Phenomena

- **SET** Single Event Transient

- **SEU** Single Event Upset

- **SM** Switch Matrix

- $\mathbf{SoC}$  System-on-Chip

- SOI Silicon–On–Insulator

- $\mathbf{SR}$  Shift Register

- **SRAM** Static Random Access Memory

- **TID** Total Ionizing Dose

- **TMR** Triple Modular Redundancy

- **TMR-MER** Triple Modular Redundancy with Module-based configuration memory Error Recovery

- TMR-Scrubbing Triple Modular Redundancy with configuration memory Scrubbing

- **UB** Upper Bound Value

- **UNSW** The University of New South Wales

## Chapter 1

## Introduction

### 1.1 Why SRAM-based FPGAs in Space?

Future satellite-based space missions are expected to acquire and process very high data rates from active and passive instruments [36]. Recent internal studies at NASA's Jet Propulsion Laboratory (JPL) estimate approximately 1–5 Terabytes per day of raw data (uncompressed) are expected, for example, from spectroscopy instruments [120]. Hence, there is the need to implement high performance, on-board processing systems that can handle such data rates and that, for example, are able to perform lossless data compression to reduce data volumes to those within the downlink capabilities of the spacecraft and existing ground stations. Apart from the increase in performance, the next generation of on-board processing is also required to be flexible and re-programmable in-orbit and during active service. This brings about challenging requirements for future on-board processing systems that cannot be met with space-qualified processors available today [50, 88, 160].

The implementation devices most suited to meeting such requirements are *Field Pro*grammable Gate Arrays (FPGAs). FPGAs offer a low Non-Recurring Engineering (NRE) cost alternative to Application-Specific Integrated Circuit (ASIC) technologies for custom hardware. Although FPGAs cannot provide the same level of performance as an ASIC, they offer at least an order of magnitude computational efficiency advantage over generalpurpose processors. FPGAs also offer the flexibility to be reconfigured on-demand for in-field bug fixes, upgrades or entirely new applications.

FPGAs, in general, have demonstrated their benefits in a variety of space-based projects [106, 170]. More examples include Mars Exploration Rovers, which use Xilinx FPGAs for

#### CHAPTER 1. INTRODUCTION

motor control and landing pyrotechnics [138], and the Los Alamos National Laboratory satellite (CFEsat), which uses nine FPGAs as part of its high performance computing payload [137]. Another example is the Sentinel-2 spacecraft, a current mission of the *European Space Agency* (ESA), whose payloads are mostly FPGA based [53].

FPGAs are typically classified into three different types based on the technology used to store the configuration. These include anti-fuse, flash and SRAM-based FPGAs [173]. Until now the most commonly used implementation technology in space has been antifuse, which uses *One-Time Programmable* (OTP) fuses to permanently set the state of each FPGA configuration bit. The advantage of these devices is their relative immunity to radiation-induced effects and they are generally the most reliable type of FPGA to use in space applications [99]. However, the main drawback of anti-fuse FPGAs is that the configuration data cannot be changed once it is configured. This prevents the user from updating the device in-flight or from using them in reconfigurable computing applications.

The second most commonly used technology in space is based on flash memory technology. Recently, flash-memory based FPGAs, such as the ProASIC3 devices from Microsemi, have been considered for use in space-based instruments [102, 107]. Flash cells are generally immune to radiation-induced upsets and, thus the configuration memory of a flash FPGA is protected from upsets [98]. However, the use of flash FPGAs on long-term spacebased missions is problematic due to their rather low immunity to *Total Ionizing Dose* (TID) effects and *Single Event Latch-ups* (SELs) [14, 103]. Although flash FPGAs can be reconfigured and offer good performance, the limitation of the number of times that they can be reconfigured renders them less desirable for use in long-term missions or in reconfigurable systems that are regularly reconfigured.

SRAM-based FPGAs use static memory cells to store the internal FPGA configuration. These static memory cells require power to store configuration state and must be programmed from external memory after the FPGA is powered up. There are two types of SRAM-based FPGAs, including radiation-hardened and *Commercial, Off-The-Shelf* (COTS) FPGAs. Compared to COTS FPGAs, radiation-hardened FPGAs are more commonly used in space because they provide protection against radiation-induced faults in the configuration and application memory. However, apart from the sale and use of these devices being restricted by the *International Traffic in Arms Regulations* (ITAR) rules [37], these devices are orders of magnitude more expensive than equivalently sized COTS FPGAs, consume more power to operate and usually lag a couple of process generations behind current COTS device technologies. Most importantly, because they are much smaller in size and cannot be reconfigured at run time, they are more limited and less flexible than COTS devices [20].

COTS SRAM-based FPGAs offer additional flexibility over OTP FPGAs in both the development and operation of space instruments. In [126], Pingree describes the typical problems of one-time programmable FPGAs that were used in the command and telemetry interface of the key instrument on NASA's Juno spacecraft. To meet requirements, engineers had to design and configure the FPGA two years before launch. The FPGA configuration could not be modified, improved or corrected without significantly impacting on the project cost and schedule. Moreover, the 5-year trip to Jupiter also required calibration activities that had to be performed without altering the FPGA configuration. It is therefore impractical to use an OTP FPGA when the numerous reasons for potentially needing to update the FPGA configuration to better meet mission objectives are considered. This is not the case with SRAM-based FPGAs that can be updated at any stage of a mission.

Due to the benefits of COTS SRAM-based FPGAs, there is growing interest in using them for data-intensive processing applications, such as those that are prevalent in space-based systems, particularly for use in low cost, low orbit, micro- and nano-satellites, which are typified by far lower costs and shorter life-cycles than large-scale, higher orbit satellites designed for communications, scientific and defence applications. In addition to their ready availability, low cost and flexibility, these FPGAs contain abundant programmable logic resources and high-bandwidth on-chip memories that are suitable for complex, highthroughput applications, such as signal-processing. Modern SRAM-based FPGAs can also be reconfigured to allow different applications to be instantiated at different times and for specific mission objectives using the one device. Last but not least, reconfigurability can also be used for uploading new applications and for fixing bugs found in the existing design.

### **1.2** Scope and Objectives

#### 1.2.1 Scope

Current state-of-the-art SRAM-based FPGAs, which can include on the order of a billion configuration memory bits, are being looked to as suitable candidates for hosting complex, high-performance, space-based and extra-terrestrial digital systems due to their low cost, low power consumption, run-time reconfigurability, and their impressive processing

#### CHAPTER 1. INTRODUCTION

performance [50,88]. However, the designers of space-based and extra-terrestrial SRAMbased FPGA applications must consider the impact of ionizing radiation, i.e., high-energy charged particles and cosmic rays, on the device, primarily in the form of *Single Event Upsets* (SEUs) [26]. SEUs may alter the logic state of any static memory element, i.e., configuration latches, user flip-flops, internal block memory and other device-specific control registers. Since millions of configuration latches within an FPGA are programmed to implement the user functionality, an SEU in the configuration memory can adversely and dramatically affect the expected FPGA functionality. Therefore, in this thesis we mainly focus on techniques to mitigate configuration memory SEUs.

Apart from shielding, which may not be feasible in micro- and nano-satellites, the safe use of FPGAs in harsh radiation environments requires the implementation of robust SEU mitigation design techniques. Hardware redundancy, such as Triple Modular Redundancy (TMR), is one of the most commonly used techniques [146, 167]. TMR can mask any single design failure by voting on the result of three functionally equivalent replicas. The TMR technique can be applied at different levels of granularity. At the coarse end of the spectrum, it can be applied to the system as a whole, whereas at the fine end of the spectrum, it can be applied to each individual memory element of a system. More fine-grained application of TMR offers shorter error detection latencies together with higher area overheads due to the additional voters needed. However, TMR is unable to correct errors or eliminate erroneous values that have become trapped within a cyclic user circuit or within the configuration memory. Errors trapped in user circuitry can, though, be corrected by resetting the faulty module or by resynchronizing the module with its functionally equivalent siblings. To deal with configuration memory errors, TMR is usually combined with error recovery techniques, such as scrubbing [26,66], or Module-based Error Recovery (MER) [20]. We use the term TMR-Scrubbing to refer to an FPGA-based TMR system in which configuration memory errors due to SEUs are recovered by scrubbing, whereas TMR-MER is used to refer to FPGA-based TMR systems that rely on module-based error recovery to correct configuration memory errors due to SEUs.

Both TMR-Scrubbing and TMR-MER rely on *Dynamic Partial Reconfiguration* (DPR) to correct configuration memory errors. TMR-Scrubbing is typically initiated periodically and commonly involves reading back each configuration memory frame of the device, checking it for errors using in-built *Error-Correction Code* (ECC) or by comparing it to a golden reference, correcting any errors that are found and writing back any corrected frame (memory segment). In contrast, TMR-MER is commonly triggered when repeated errors are detected by the voter associated with a TMR component and involves rewriting the configuration memory for the specific module that has been found to be in error.

TMR-Scrubbing, which could be referred to as a *frame-based* recovery technique, is thus more fine-grained than TMR-MER in its corrective action, but involves reading or writing the entire configuration memory contents. On the other hand, TMR-MER is more coarse-grained than TMR-Scrubbing, in so far as the configuration memory contents of a complete module are rewritten; multiple configuration memory errors affecting the one frame/module can thus be corrected in a single action, and correction is typically faster with TMR-MER than with TMR-Scrubbing.

In the past couple of decades, more research has focused on the use of TMR-Scrubbing than on TMR-MER to improve the reliability of SRAM-based FPGA systems [146]. However, TMR-MER is being seen as offering certain advantages over TMR-Scrubbing. A significant drawback of TMR-scrubbing is that it results in unnecessary power consumption because it is invoked periodically even when no SEU has occurred [158]. Furthermore, the delay in correcting errors using TMR-scrubbing may be excessive: current state-of-the-art FPGAs, e.g., Xilinx UltraScale XCVU440, can include on the order of a billion configuration bits and the time required to read back the entire configuration memory during a scrub cycle can thus exceed 120 ms. This means that SEUs will be detected in the system after 60 ms on average, which could be too long for time- and safety-critical systems. TMR-MER aims to avoid these costs by reconfiguring just that portion of the device that is suspected of being in error and by providing low-latency error detection via the TMR voters [20]. TMR-MER, thus, aids both the system power consumption and reliability [3,158], which are both desirable outcomes for space-based systems. In this thesis, we explore a new approach to further improve the reliability of TMR-MER systems. We thereby aim to further understand the relative merits of TMR-MER and TMR-Scrubbing.

#### 1.2.2 Objectives

This thesis aims to provide solutions to further improve the reliability of TMR-MER systems. The thesis has three objectives.

Both TMR-Scrubbing and TMR-MER utilize a controller to operate, but TMR-MER also requires a means of relaying *Reconfiguration Requests* (RRs) from the voters in the system to a central *Reconfiguration Controller* (RC) [4]. A star-, bus-, or ring-based *Reconfiguration Control Network* (RCN) is often employed to perform this function [4]. Another alternative is to use the in-built FPGA configuration infrastructure to access distributed status registers containing the RRs [4]. The performance and reliability of the RCN are important for a few reasons. Firstly, the latency of the RCN has a direct impact

#### CHAPTER 1. INTRODUCTION

on the *Mean Time To Recover* (MTTR) from errors in the system, and the sooner the module is recovered, the lower the likelihood that the protection provided by TMR will fail. On the other hand, the RCN is often implemented as a non-redundant component in the system, whereby it introduces a single point of failure that can greatly compromise system reliability. Therefore, the first objective of this thesis is to focus our attention on the design of the RCN for high performance with low resource utilization so as to reduce its sensitivity to SEUs. We investigate possible network topologies for implementing an RCN and compare their area, performance, and upset vulnerability with a view to establishing the best solution for a given operating environment.

Irrespective of the RCN topology and technique employed, the voters, which trigger a module-based reconfiguration by raising a request, cannot be checked in parallel. They must be checked sequentially. Conventionally, the voters are checked in round-robin order [4, 20, 152, 163]. Round robin is appropriate when the system contains similarly sized TMR components, which are equally likely to suffer SEUs. However, when TMR components vary in size, such as in the RUSH (Rapid recovery from SEUs in Reconfigurable Hardware) payload [30], the order in which the voters of TMR components are checked has an inevitable impact on overall system reliability. Intuitively, larger components are more susceptible to configuration memory SEUs, and thus should be checked more frequently than smaller ones. Therefore, the second objective of this thesis is to propose an on-chip *Voter Scheduling Engine* (VSE) to help the RC dynamically adjust the order in which RRs from TMR voters are checked for module errors based on the likelihood of the next checked component being in error [113]. The approach was implemented based on the idea that the RRs from the more vulnerable components, i.e., those comprising a greater number of essential bits [89], are checked more frequently than the less vulnerable ones.

Consequently, the VSE work prompted us to investigate whether a static voter checking schedule could be found to enhance TMR-MER system reliability beyond that possible with the dynamic voter checking method. Therefore, the third objective of this thesis is to explain our approach to developing a static schedule for checking voters that maximizes the reliability of TMR-MER systems. It has also been noted that while TMR-MER is generally effective for mitigating SEUs affecting the configuration memory [4], it is not well suited to protecting systems against multiple coincident SEUs that affect multiple modules of a TMR component and that thereby defeat the protection afforded by redundancy. Therefore, to fulfil the third objective, we investigate the reliability of TMR-MER systems consisting of multiple triplicated components operating in harsh radiation environments, such as in geosynchronous orbit during solar flares and in high-energy physics laboratories like the Large Hadron Collider, where multiple coincident SEUs are more likely to occur [123]. Our main interest in this objective is in determining the impact on overall system reliability of varying the order and rate at which the voters of TMR components are checked for RRs.

To achieve the objectives mentioned above, and to demonstrate their applicability in general, we have conducted experiments both on synthetic systems comprising a variety of TMR components, and on the RUSH micro-satellite payload, which contains 9 differently sized components. The RUSH payload is described in detail in the Appendix of this thesis.

## **1.3** Thesis Contributions

The work described in this thesis aims to improve the reliability of TMR-MER systems. The key contributions of this thesis are:

#### 1.3.1 Reconfiguration Control Network

We compare four RCNs with respect to reliability, latency, scalability and power consumption. Fault injection experiments were conducted to evaluate the impact of each RCN on system reliability. We demonstrate that the hard network, which uses the *Internal Configuration Access Port* (ICAP) of the FPGA to read the voter state, achieves the highest reliability in a case study that is implemented on the RUSH (Rapid recovery from SEUs in Reconfigurable Hardware) payload [30]. We also show that the *Mean Time To Detect* (MTTD) configuration memory errors is greatest for the ICAP-based approach due to the relatively large latency involved in retrieving user state this way, but we demonstrate an effective optimization that significantly narrows the gap in MTTD between this hard approach and the soft RCNs. Finally, we assess the reliability of a real system employing module-based recovery relative to the same system using blind scrubbing. We have determined that scrub-based error recovery results in higher reliability unless the RCN is itself triplicated and repaired when its configuration becomes corrupted.

#### 1.3.2 Voter Scheduling Engine

We propose and evaluate a *Voter Scheduling Engine* (VSE) that dynamically prioritizes and manages the voter checks in an FPGA-based TMR-MER system. The proposed VSE is based on the idea that the currently most vulnerable TMR component needs to be checked next. Moreover, we incorporate the VSE into an ICAP-based RCN to readback configuration frames that contain the health status of the system's TMR components [4,163].

Furthermore, we assess and compare the reliabilities of a TMR system with MER, whereby the TMR voter states are checked in a round-robin fashion, with that of the same system implementing VSE. We demonstrate that TMR systems that utilize the VSE to determine which component to check next are generally more reliable than those using a roundrobin order for checking component voters. This is especially the case when the period between two successive checks is increased, e.g., when there is an increased number of TMR components to check, or when the check frequency is reduced for the purpose of saving energy. Results obtained using four different radiation conditions show that the failure probability of the TMR system incorporating VSE is up to 50% lower than that of the same system using round-robin voter checking during a simulated 30-day mission in *Geostationary Equatorial Orbit* (GEO) and during a simulated 10-year mission in *Low Earth Orbit* (LEO).

#### 1.3.3 Variable-Rate Voter Checking

In the second objective, we developed methods for identifying the next component to check at run time based on the likelihood that the component has failed since the last check [113]. In contrast, the third objective is to report on an off-line approach to determining a fixed voter checking sequence that maximizes system reliability. Our contributions are:

- To derive reliability models of TMR-MER systems that comprise finitely many TMR components whose voters are checked in round-robin order and at a variable rate. We refer to such a schedule as *Variable-Rate Voter Checking* (VRVC). Previous work has primarily focused on the effects of SEUs on SRAM FPGA-based systems while our analysis considers the impact of multiple consecutive events, which is an important consideration in providing a more accurate analysis of the system reliability in high radiation environments.

- To propose a *Genetic Algorithm* (GA) for finding the optimal rate at which to check all components so as to maximize the *Mean Time To Failure* (MTTF) and the reliability of TMR-MER systems.

- To show that power consumed checking for errors can be reduced by reducing the checking frequency. In this case, VRVC is capable of ensuring a higher system

reliability than round robin or VSE.

• To demonstrate that MTTD is reduced by 44% and 30% on average when VRVC is used instead of round robin and VSE, respectively.

### 1.4 Publications

#### 1.4.1 Journal Papers

- N. T. H. Nguyen, D. Agiakatsikas, Z. Zhao, T.Wu, E. Cetin, O. Diessel, and L. Gong, "Reconfiguration Control Networks for TMR Systems with Module-based Recovery," *Microprocessors and Microsystems*, 2017 (under review) [112].

- N. T. H. Nguyen, E. Cetin, O. Diessel, "Improving Reliability of FPGA-based Systems by Scheduling Checks for Configuration Memory Errors," *IEEE Transactions on Aerospace and Electronic Systems*, 2017 (under review) [114].

#### 1.4.2 Conference Papers

- N. T. H. Nguyen, E. Cetin, and O. Diessel, "Scheduling Voter Checks to Detect Configuration Memory Errors in FPGA-based TMR Systems," in *IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT)*, Oct 2017 [116].

- N. T. H. Nguyen, E. Cetin, and O. Diessel, "Scheduling considerations for voter checking in TMR-MER systems," in *IEEE International Symposium on Field Programmable Custom Computing Machines (FCCM)*, April 2017, pp. 30-30 [111].

- N. T. H. Nguyen, E. Cetin, and O. Diessel, "Dynamic scheduling of voter checks in FPGA-based TMR systems," in *International Conference on Field Programmable Technology (FPT)*, Dec 2016, pp. 169–172 [113].

- D. Agiakatsikas, N. T. H. Nguyen, Z. Zhao, T.Wu, E. Cetin, O. Diessel, and L. Gong, "Reconfiguration Control Networks for TMR Systems with Module-based Recovery," in *IEEE International Symposium on Field Programmable Custom Computing Machines (FCCM)*, May 2016, pp. 88–91 [4].

- L. Gong, T. Wu, N. T. H. Nguyen, D. Agiakatsikas, Z. Zhao, E. Cetin, and O. Diessel, "A Programmable Configuration Controller for Fault-tolerant Applications,"

in *IEEE International Conference on Field Programmable Technology (FPT)*, Dec 2016, pp. 117-124 [58].

L. Gong, A. Kroh, D. Agiakatsikas, N. T. H. Nguyen, E. Cetin, and O. Diessel, "Reliable SEU monitoring and recovery using a programmable configuration controller," in *International Conference on Field Programmable Logic and Applications* (FPL), Sep 2017 [57].

#### 1.4.3 Technical Reports

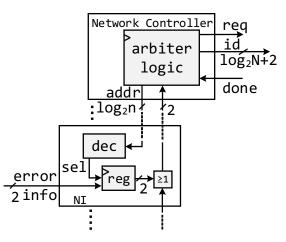

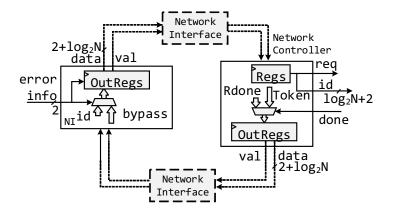

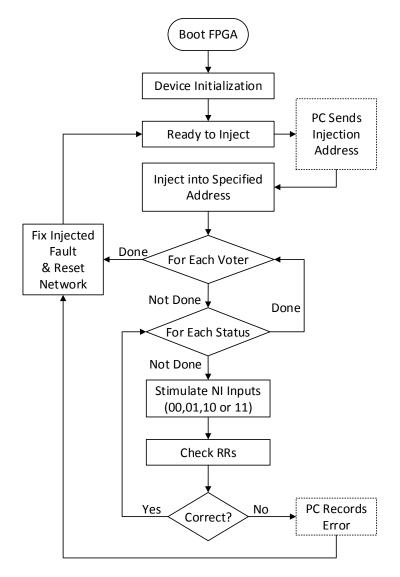

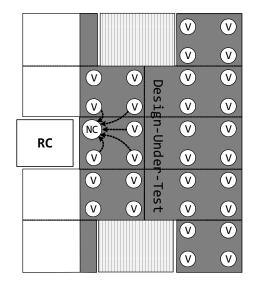

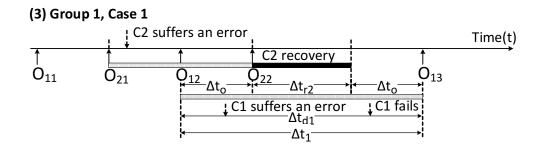

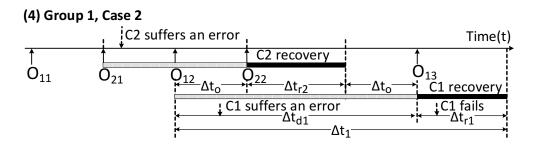

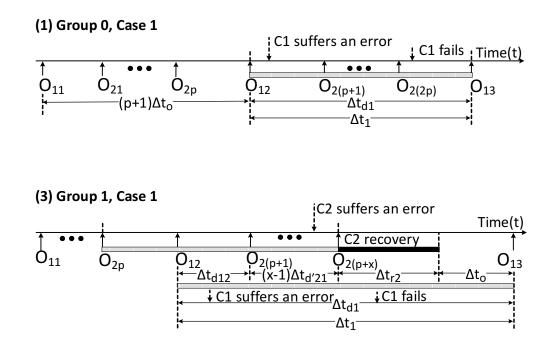

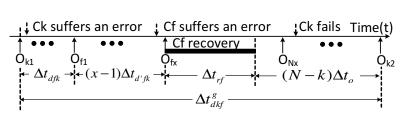

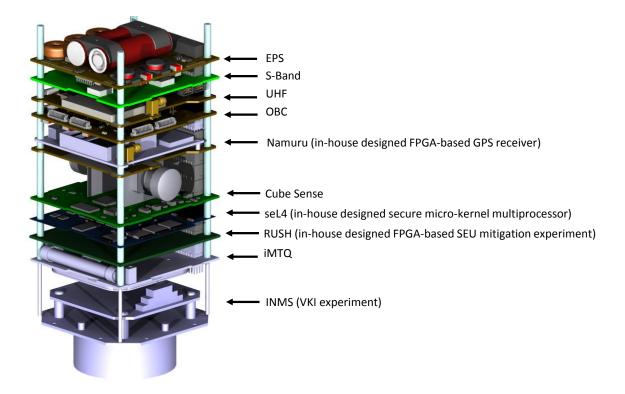

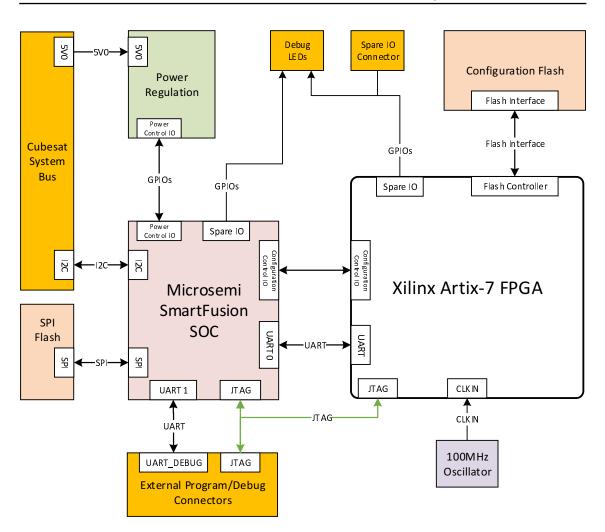

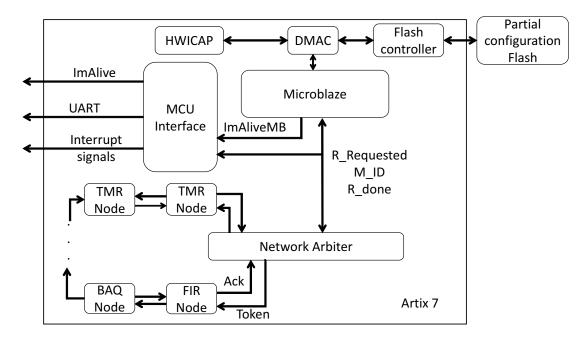

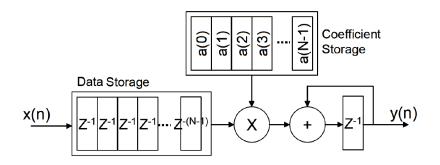

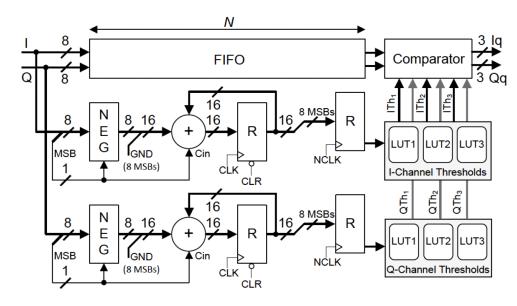

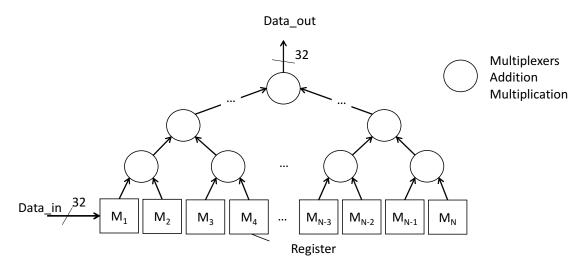

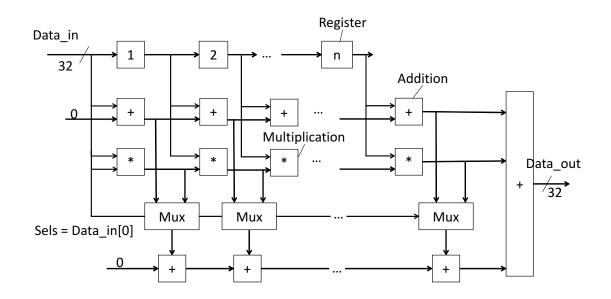

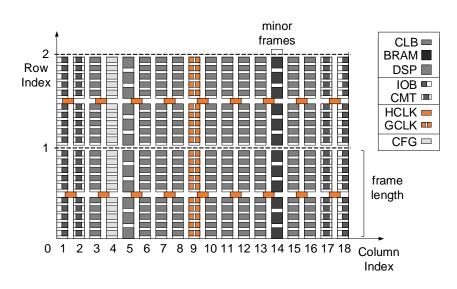

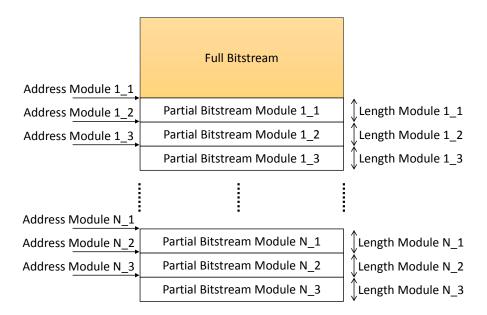

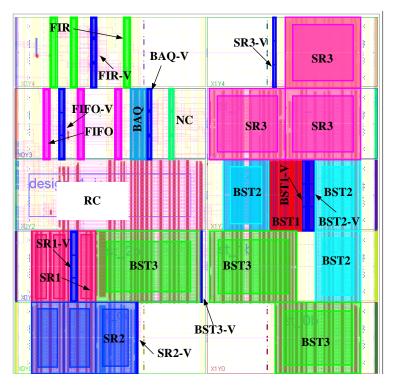

N. T. H. Nguyen, E. Cetin, and O. Diessel, "Scheduling Considerations for Voter Checking in FPGA-based TMR Systems," School of Computer Science and Engineering, UNSW Sydney, Tech. Rep., 05 2017 [115].