# **STUDIENARBEIT**

# FPGA Crossbar Switch Architecture for Partially Reconfigurable Systems

von

#### Till Fischer

Eingereicht am 07.05.2010 beim Institut für Angewandte Informatik und Formale Beschreibungsverfahren am Karlsruher Institut für Technologie

Referent: Prof. Dr. Hartmut Schmeck Betreuer: Dr. Oliver Diessel (UNSW) Studienarbeit am

Institut für Angewandte Informatik und Formale Beschreibungsverfahren

Thema: FPGA Crossbar Switch Architecture for Partially Reconfigurable Systems

Autor: Till Fischer

| Ich versichere hiermit wahrheitsgemäß, die Arbeit bis auf die dem Aufgabensteller bereits bekannte Hilfe selbständig angefertigt, alle benutzten Hilfsmittel vollständig und genau angegeben und alles kenntlich gemacht zu haben, was aus Arbeiten anderer unverändert oder mit Abänderung entnommen wurde. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Karlsruhe, den 07.05.2010                                                                                                                                                                                                                                                                                    |

# Zusammenfassung

In den letzten Jahren haben sich durch immer höhere Integrationsdichten in der Chiptechnologie die verfügbaren Ressourcen auf FPGAs vervielfacht. Damit sind stetig komplexere Implementierungen bis hin zu ganzen System-on-Chips auf einem einzelnen FPGA möglich geworden. Gleichzeitig wurde die Fähigkeit zur Rekonfiguration immer flexibler, womit sich inzwischen genau definierte Bereiche auf dem Chip zur Laufzeit modifizieren lassen, ohne dass eine Unterbrechung der übrigen Hardware nötig ist (modulare dynamische partielle Rekonfiguration). Vorteile dieser Technik sind unter anderem Platz- und Energieeinsparungen durch Auslagern nicht benötigter Komponenten oder die vereinfachte Wartung und Aktualisierung von Hardware. Allerdings sind besondere Maßnahmen erforderlich, um den Betrieb eines derartigen partiell rekonfigurierbaren Systems mit geringem Overhead zu gewährleisten. Dazu zählen insbesondere spezielle Kommunikationsstrukturen, von welchen nun verlangt wird, dass sie sich den weniger statischen Anforderungen anpassen können. Eine derartige Struktur wird in dieser Arbeit vorgestellt.

Aktuelle Plattformen für partielle Rekonfiguration benutzen vorwiegend Busse oder feste Verbindungen, welche durch ihre Inflexibilität der partiellen Rekonfiguration nur bedingt gerecht werden. Daher schlagen neuere Forschungen Networks-on-Chip als sehr flexible Alternative vor. Das größte Problem von diesem Ansatz ist jedoch der hohe Overhead, welcher mit einer derartigen Netzwerkarchitektur einher geht. In dieser Arbeit wird daher eine angepasste Crossbar Switch Architektur vorgestellt, welche eine erhöhte Flexibilität gegenüber einfachen Bussen mit einem geringem Kontrolloverhead verbindet. Informationen werden hier auf dedizierten Kanälen übertragen, welche nach initialer Einrichtung nur ein Minimum an zusätzlichem Aufwand verursachen. Neue Konfigurationen für die Kanäle können in kürzester Zeit eingerichtet werden, es sind also trotzdem häufige Anpassungen möglich. Außerdem wird eine nebenläufige Übertragung auf allen Kanälen angeboten, es kommt also zu keiner gegenseitigen Blockierung der Kommunikationspartner. Da schließlich sämtliche Kommunikation gepuffert wird, ist ein asynchroner Betrieb der Komponenten möglich. Diese Eigenschaften müssen durch den Verbrauch von zusätzlichen Ressourcen erkauft werden. Allerdings berücksichtigt die Implementierung das spezielle Layout von FPGAs und es wird außerdem die allgemeine Crossbar Switch Architektur angepasst, um eine schlechte Skalierung zu vermeiden.

In dieser Arbeit werden zuerst einige alternative Lösungen zur on-chip Kommunikation in partiell rekonfigurierbaren Systemen vorgestellt, bevor der Entwurf und die Implementierung der neuen Architektur genauer beschrieben wird. Abschließend erfolgt eine Auswertung anhand des implementierten Prototyps sowie ein Vergleich mit den alternativen Lö-

sungen. Es zeigt sich, dass der Flächenoverhead gut kontrolliert werden kann und für kleine Systeme eine höhere Performance erreicht wird. Für größere Systeme offenbart sich jedoch ein an Stärke zunehmender Leistungseinbruch. Hier wird neben anderen Vorschlägen zur Verbesserung auch eine einfache Erweiterung vorgestellt, welche dieses Problem behebt.

#### **Abstract**

Partial reconfiguration offers several benefits for a system on chip. But in order to take advantage of this technique, easy access and low overhead must be provided. One key issue therefore is the on-chip communication architecture. Current reconfigurable systems use buses and fixed links, which are quite inflexible; recent proposals suggest using networks on chip instead. The problem of the latter approach is the high overhead which is required to control the dataflow. In this work, XBar is presented: a customized crossbar switch architecture for reconfigurable systems on chip, which provides flexibility without high control overhead. Channels are established in order to transfer data, and once the channel is set up, data can be delivered with a minimum of additional effort. Concurrent transmission is possible on all channels, so interruptions due to blocking cannot occur. Furthermore, new channel configurations can be established in a very short period of time, so frequent changes are possible. Since communication is buffered, the infrastructure may be used asynchronously and components of different clock domains can be connected. The scalability is worse than with a packet-switched network on chip and it is not possible to provide the same amount of flexibility. However, better overall results can be achieved particularly for throughput and latency for small systems. Furthermore, the design of partially reconfigurable modules is eased.

# **Acknowledgements**

First and foremost I would like to thank my supervisor, Dr Oliver Diessel, for his excellent support during my work. His guidance and the helpful notes he provided were a great assistance. Also I'd like to thank you for the offer to attend the FPT'09 in Sydney, which was a unique opportunity to experience the conference at close range.

Furthermore, I should like to thank Prof Hartmut Schmeck from the University of Karlsruhe, who brought me in contact with Dr Diessel. Without your help my internship at the University of New South Wales would not have been possible. My thanks also go to the University of New South Wales for the Practicum Exchange Program, which enabled me to study in Australia.

Last but not least I would like to thank my family, who supported me in any possible way, and of course I am deeply grateful for the enduring encouragements of my girlfriend Ursula during my far too long absence.

# **Table of Contents**

| Li | st of Fig | gures | xii                        | i        |

|----|-----------|-------|----------------------------|----------|

| 1  | Intro     | oduct | tion1                      | L        |

|    | 1.1       | Mot   | ivation1                   | L        |

|    | 1.2       | Con   | tributions                 | <u>)</u> |

|    | 1.3       | Outl  | ine                        | 3        |

| 2  | Fund      | dame  | entals5                    | 5        |

|    | 2.1       | FPG   | As5                        | 5        |

|    | 2.2       | Part  | ial Reconfiguration6       | 5        |

|    | 2.3       | Xilin | x Tools                    | 7        |

|    | 2.3.2     | 1     | ISE Design Suite           | 3        |

|    | 2.3.2     | 2     | XDL                        | )        |

|    | 2.4       | Inte  | rconnectsS                 | )        |

|    | 2.4.2     | 1     | Point-to-Point Connections | )        |

|    | 2.4.2     | 2     | Shared Resource            | )        |

|    | 2.4.3     | 3     | Network                    | )        |

|    | 2.4.4     | 1     | Hybrid Interconnects       | 3        |

| 3  | Rela      | ted \ | Nork15                     | 5        |

|    | 3.1       | ReC   | oBus                       | 5        |

|    | 3.1.3     | 1     | Design and Implementation  | 5        |

|    | 3.1.2     | 2     | Evaluation                 | 7        |

|    | 3.2       | NoC   | : Work of Marescaux et al  | 3        |

|    | 3.2.3     | 1     | Routing19                  | )        |

|    | 3.2.2     | 2     | Routers and Topology       | )        |

|    | 323       | 3     | Network Interface 20       | )        |

|   | 3.2.     | 4     | Evaluation                      | 20 |

|---|----------|-------|---------------------------------|----|

|   | 3.3      | NoC   | : CoNoChi                       | 21 |

|   | 3.3.     | 1     | Routing                         | 21 |

|   | 3.3.     | 2     | Routers                         | 22 |

|   | 3.3.     | 3     | Topology and Adaptability       | 23 |

|   | 3.3.     | 4     | Evaluation                      | 23 |

|   | 3.4      | Xilin | x Crossbar Switch               | 24 |

|   | 3.4.     | 1     | Crossbar Switch basics          | 24 |

|   | 3.4.     | 2     | Design and Implementation       | 25 |

|   | 3.4.     | 3     | Evaluation                      | 26 |

|   | 3.5      | Con   | clusion                         | 27 |

|   |          |       |                                 |    |

| 4 | Des      | Ū     |                                 |    |

|   | 4.1      |       | uirements                       |    |

|   | 4.2      | Desi  | gn Decisions                    | 31 |

|   | 4.3      | Arch  | nitecture                       | 33 |

|   | 4.3.     | 1     | Overview                        | 34 |

|   | 4.3.     | 2     | Interfaces                      | 36 |

|   | 4.3.     | 3     | Switching Structure             | 38 |

|   | 4.3.     | 4     | Control Logic                   | 39 |

|   | 4.4      | Desi  | gn Flow                         | 40 |

| _ | l saa sa | lama  | ntation                         | 45 |

| 5 | •        |       |                                 |    |

|   | 5.1      |       | Hard Macro                      |    |

|   | 5.1.     | 1     | Cross-Points                    | 46 |

|   | 5.1.     | 2     | Maintaining Density             | 48 |

|   | 5.1.     | 3     | I/O, timing and final structure | 48 |

|   | 5.2      | COR   | EGenerator FIFOs                | 50 |

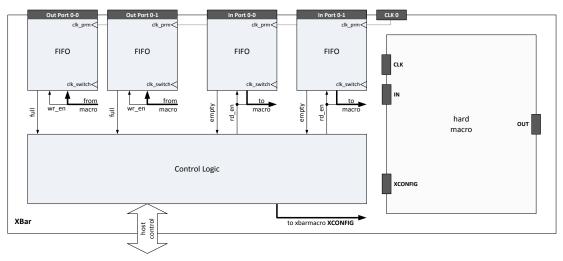

|   | 5.3      | VHC   | PL Top-Level Entity             | 51 |

|   | 5.3.     | 1     | Behavior                        | 51 |

|    | 5.3.    | 3.2 Exemplary Implementation              | 54   |

|----|---------|-------------------------------------------|------|

| 6  | Eva     | aluation                                  | 57   |

|    | 6.1     | Impact of design parameters               | 57   |

|    | 6.1.    | .1 Area                                   | 57   |

|    | 6.1.    | 2 Performance                             | 58   |

|    | 6.1.    | L.3 Comparison                            | 60   |

|    | 6.2     | Reconfiguration and switching performance | 61   |

|    | 6.3     | Scaling and Flexibility                   | 61   |

|    | 6.4     | Field of Use                              | 62   |

| 7  | Con     | nclusion and Future Work                  | 65   |

| A. | Sou     | urce Code                                 | xiii |

| Ad | cronym  | ms                                        | xv   |

| Bi | bliogra | aphy                                      | xvii |

# **List of Figures**

| Figure 2.1: ADM-XRC-4 Board [3]                             | 6  |

|-------------------------------------------------------------|----|

| Figure 2.2: Interconnection methodologies                   | 9  |

| Figure 2.3: Network topologies                              | 12 |

| Figure 3.1: ReCoBus interface [19]                          | 16 |

| Figure 3.2: ReCoBus shared read multiplexer [19]            | 16 |

| Figure 3.3: ReCoBus multiplexer interleaving [19]           | 17 |

| Figure 3.4: ReCoBus delay with no pipelining [14]           | 18 |

| Figure 3.5: ReCoBus delay with pipelining [14]              | 18 |

| Figure 3.6: NoC router with 2 input and 2 output ports [16] | 20 |

| Figure 3.7: CoNoChi router [21]                             | 22 |

| Figure 3.8: CoNoChi architecture [22]                       | 24 |

| Figure 3.9: Xilinx Crossbar cascaded structure [23]         | 26 |

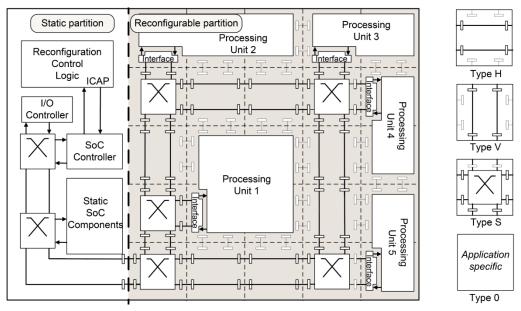

| Figure 4.1: Communication Patterns                          | 30 |

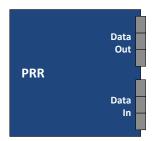

| Figure 4.2: Abstraction of a PRR                            |    |

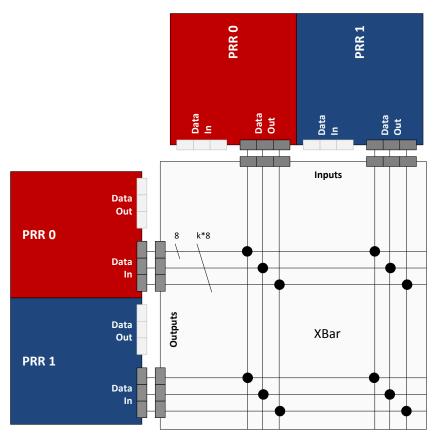

| Figure 4.3: XBar schematic view                             | 35 |

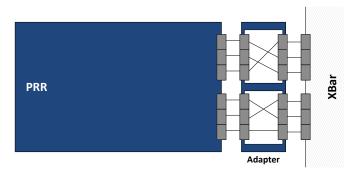

| Figure 4.4: PRR with adapter                                | 36 |

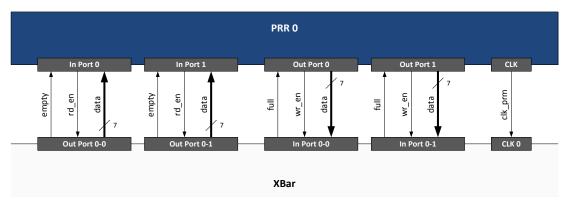

| Figure 4.5: XBar interface                                  | 37 |

| Figure 4.6: Basic switching structure                       | 38 |

| Figure 4.7: XBar FIFO control logic                         | 39 |

| Figure 4.8: XBar block diagram                              | 40 |

| Figure 4.9: EA PR design flow [24]                          | 41 |

| Figure 4.10: XBar design flow                               | 43 |

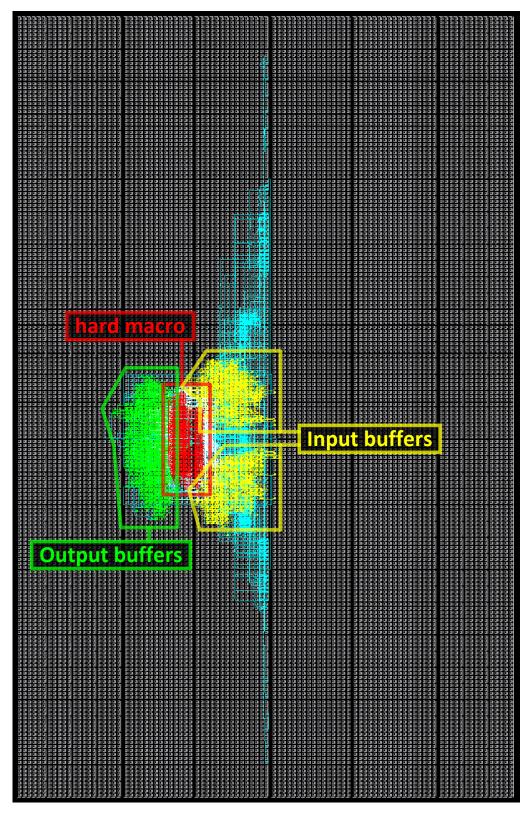

| Figure 5.1: Implementation domains                          | 45 |

| Figure 5.2: Cross-Point implementation                      | 47 |

| Figure 5.3: Interleaving vertical bundles                   | 48 |

| Figure 5.4: Final hard macro implementation                 | 50 |

| Figure 5.5: XBar transfer behavior                          | 52 |

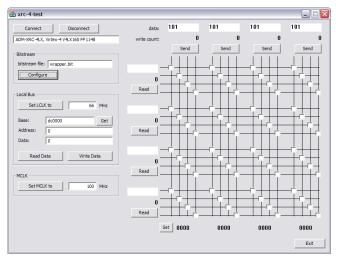

| Figure 5.6: Test application on host machine                | 54 |

| Figure 5.7: Test environment on Virtex-4 VLX160             | 55 |

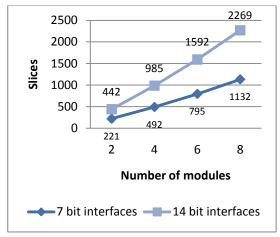

| Figure 6.1: Used slices for varying interface width                     | .58  |

|-------------------------------------------------------------------------|------|

| Figure 6.2: Used slices for varying number of modules                   | .58  |

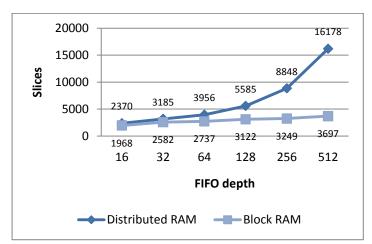

| Figure 6.3: Used slices for varying FIFO depth                          | .58  |

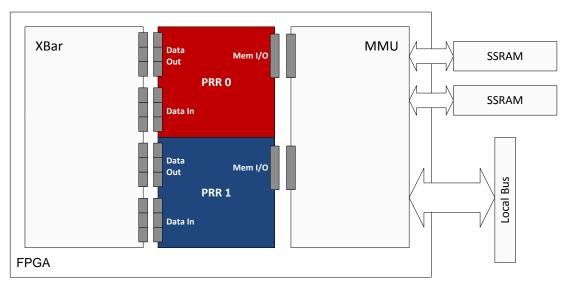

| Figure 6.4: PR system with MMU                                          | . 63 |

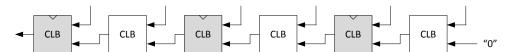

| Figure 7.1: One CLB row of the switching structure with pipeline stages | .65  |

## 1 Introduction

#### 1.1 Motivation

In the course of time, available resources on FPGA devices have increased thanks to continuous advances in integration density. As a result, more and more complex designs can be implemented on a single FPGA, up to whole System-on-Chips (SoC). Simultaneously, reconfiguration capabilities of FPGAs were enhanced and became more flexible; partial reconfiguration evolved. This enabled the possibility to update, add or remove parts of a system while the rest continues to operate. Exploiting this feature has been an area of particular research interest in recent years and this still holds true today.

Obviously, there are several benefits of partial reconfiguration  $[\underline{1}]$ . First of all, it is possible to change parts of the hardware, which might be required due to maintenance for example, without demanding a shutdown of the system. Such updates are possible at any time, both locally and remotely. As a consequence, updates can even be applied in critical situations, when access is not possible under conventional circumstances. Furthermore, hardware can be shared. Only those components, which are necessary at a certain point of time, must be available. This allows realization of even larger systems on smaller FPGA devices. This can lead to reductions in power consumption and overall costs. System performance may increase, since more specialized components can be used. Additionally, reconfiguration times can be reduced by difference-based partial reconfiguration [2]; bitstreams can remain smaller by containing configuration data for parts that effectively change only. Finally, it is expected that partial reconfiguration could significantly reduce iteration times for hardware development. If only small parts of the system had to be re-synthesized, this process could be completed within minutes rather than hours. This would allow use of fast software development methodologies for hardware design, too. However, this is not yet applicable at this point of time, since iteration cycles are still very long.

While the advantages of module-based partial reconfiguration are evident and benefits were shown for several applications, less attention was paid to the communication infrastructure, which is necessary to enable cooperation of separate components in a reconfigurable system. However, special requirements apply to such an infrastructure, since communication partners may change during runtime. Current reconfigurable platforms use buses and fixed links as interconnects which provides neither good performance nor flexibility.

Because of this, current research focuses on Networks-on-Chip (NoC) to satisfy the specific demands of a partially reconfigurable system. Most of these approaches utilize similar techniques to those used in common computer networks (local area networks, internet etc.). Data is split into several packets which are transferred independently between routers until the destination is reached. Because of this, all links in the network can be shared for all connections and a very high flexibility may be achieved. Furthermore, it is possible to serve rapidly changing communication needs: it makes no difference whether two succeeding packets are sent to the same target or if changing destinations are addressed.

However, very high control overhead is introduced at the same time, and in fact the benefits might not be exploited. Without question, highly flexible NoCs are superior to other solutions if completely unpredictable situations occur. But contrary to the computer networks addressed formerly, where nothing is known about the requirements of each participant, the communication needs of a specific system component can be predicted very well in most cases. Because of this, a different approach is considered in this work: a crossbar switch is evaluated as on-chip interconnection between partially reconfigurable modules. Crossbar switches can be treated as networks on chip as well, but instead of providing control headers with every message, connections are set up in advance. On the one hand, this significantly reduces the overhead when data is transferred as long as communication partners are fixed, and on the other hand, throughput will not suffer from concurrent communication, since data can be transferred in parallel. However, a crossbar switch is not a lightweight structure and it has to be examined whether an efficient implementation is possible and if the area overhead can be justified.

#### 1.2 Contributions

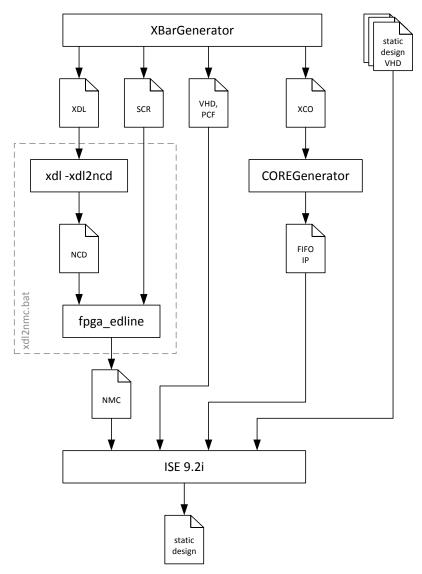

This work focuses on how a crossbar switch might be designed to allow efficient implementation on Xilinx FPGA devices. The special requirements of a module-based partially reconfigurable system are taken into account, as well as resources and capabilities of partially reconfigurable FPGAs.

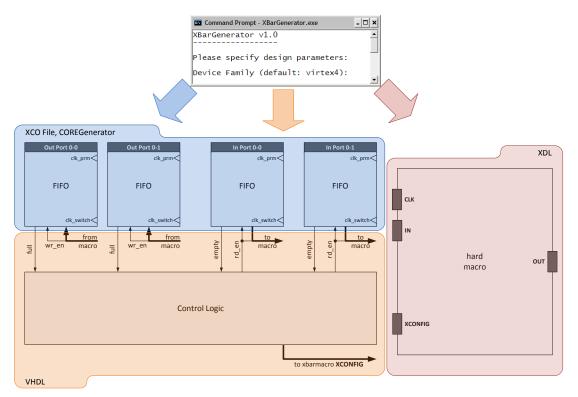

As part of this work a generator application is provided, which is capable of creating custo-mized VHDL entities of the proposed communication infrastructure. A custom design flow is introduced, which explains how the crossbar switch can be instantiated in the static design of a partially reconfigurable system.

The proposed design is implemented on a certain device and evaluated for different parameters. Furthermore, a test environment for a specific parameterization is introduced which can be used to visualize the behavior for different configurations. Benefits and drawbacks are compared to other approaches and reasonable application scenarios are suggested. This work also identifies the weak points of the proposed architecture and recommends improvements to certain problems.

#### 1.3 Outline

The background to this work is summarized in Chapter 2. Some basics about FPGA architectures are explained and the different development tools are introduced. Furthermore, an overview of the different communication models is given.

Chapter 3 reports on related work in the field of on-chip interconnects for reconfigurable systems. Three different approaches are presented for this purpose. Furthermore, a very efficient technique for implementing a crossbar switch on certain Xilinx FPGAs is shown.

In Chapter 4 the new crossbar switch is introduced. Based on several requirements, which are enumerated in the beginning of that chapter, the specific design decisions are explained. Finally, the resulting design is presented in detail.

Implementation specific details are addressed in Chapter 5. This also contains the transfer behavior for a precise example. A test environment is described in this chapter as well.

Chapter 6 provides the results of the evaluation for several different parameters and the proposed architecture is compared to the alternative approaches presented in Chapter 3. Scenarios that may benefit from this approach are identified. Several possible improvements are pointed out, which are discussed briefly in Chapter 7.

# 2 Fundamentals

This chapter explains the fundamentals which are referred to in more detail later on in this work. First, the Field Programmable Gate Array (FPGA), the basic hardware resource used for implementation, is introduced. Afterwards, the ability to partially reconfigure these devices is presented. Subsequently, the tools needed for partial reconfiguration and some more specific tools used for the implementation are described. These tools are provided by the chosen FPGA manufacturer, Xilinx Inc. Finally, an introduction to the different interconnection systems considered for the design or used in related works is given.

#### 2.1 FPGAs

Historically, the main field of use for FPGAs is emulation, evaluation and rapid prototyping of application specific integrated circuits. More recently FPGAs have become the implementation device of choice for small volumes and have proven themselves to be capable of high performance and lowest power as well. They unite the advantages of Programmable Logic Devices (PLDs) and Gate Arrays. The former are logic components, which can be configured to realize a specific but rather simple function. The latter comprise a large number of fixed and non-programmable logic resources, but the routing between these can be defined by the user. The market leader for FPGA technology is Xilinx Inc., and some of the abbreviations and details in the context of FPGA architectures within this work may be specific to Xilinx devices. Actual FPGAs provide both a large number of simple programmable logic resources in Configurable Logic Blocks (CLBs) and a lot of routing resources to individually connect the components. A hardware description can be mapped into the resources of the FPGA to implement the described behavior.

The main component of the CLB is a so-called look-up table (LUT) which is used to store a logic function. For each possible combination of inputs one output value can be configured. So any logic function with the corresponding number of inputs can be implemented within a LUT. Additionally, other resources like multiplexers and flip-flops exist in the CLBs, which are used to combine functions and select combinational or sequential paths.

For interconnection a huge amount of wires must exist within the fabric. To individually connect distinct components, it must be possible to create custom connections. In the FPGA architecture of Xilinx, several *switch matrixes* and *switch boxes* are used for this purpose.

Which wires have to be connected by a switch, and which not, is stored together with the remaining configuration data of the FPGA.

Typically, configuration data is transferred to the FPGA using a bitstream and then stored in SRAM. This means that after cutting the power supply to the device, the data is lost. Because of this, many systems offer nonvolatile memory for configuration data and automatically configure the FPGA on boot up. Furthermore, additional resources that can be accessed from the FPGA are integrated in the most cases. For example, on the development board used in this work (ADM-XRC-4, see Figure 2.1), 6 SSRAM (Synchronous Static Random Access Memory) blocks are arrange around a Virtex-4 VLX160 FPGA.

Figure 2.1: ADM-XRC-4 Board [3]

In addition to external resources, modern devices may also contain several dedicated components within the chip fabric. For example, Xilinx devices offer internal memory blocks (Block RAM), multipliers (DSP Slices), whole processor cores (PowerPC) and several other dedicated resources for quite some time.

Additionally, the capabilities of dynamic reconfiguration are further exploited. An actual research topic is so-called *partial reconfiguration* as it is described in the following section.

## 2.2 Partial Reconfiguration

Partial reconfiguration describes the ability to change the configuration of a certain area of the chip, while the rest of the implemented design continues operation. Partial reconfiguration became available to the user with the XC4000 device family. Theoretically, it was always possible to partially reconfigure FPGAs, if configuration data is stored in SRAM. How-

ever, if configuration bitstreams for the device have to be transferred as a whole, operation has to be stalled during the update process. This changed with the Virtex-II device family, where distinct *frames* could be addressed for reconfiguration. This was further enhanced with Virtex-4 devices and much more flexibility is provided nowadays: only 1-dimensional partial reconfiguration was possible with Virtex-II devices; more recent devices support almost any rectangular shape as a *partially reconfigurable region* (PRR). The smallest reconfiguration *frame* is now constrained only by the height of a clock region of the FPGA device (Virtex-4: 16 CLBs [4], Virtex-5: 20 CLBs [5], Virtex-6: 40 CLBs [6]) and can be as narrow as 1 CLB. The modules, which can be loaded into a PRR, are referred to as *partially reconfigurable modules* (PRMs).

An important issue when working with PRMs is to ensure correct communication between the reconfigurable regions and the remaining design. Xilinx handles the problem by enforcing every signal from/to a PRR to be routed through so-called *bus macros*. These are prerouted components placed to fixed locations on the FPGA during design time. Basic bus macros are provided for all devices capable of partial reconfiguration, but creating a user-defined bus macro is possible as well [7].

The benefit of partial reconfiguration is obvious and several advantages were already listed in the introduction. For example, it is possible to add or remove parts of a system as necessary; similar to swapping out pages from main memory to the hard drive. As a result, more functionality can be implemented while utilizing the same area, and overall power consumption can be reduced – as long as removing a component does not disrupt correct operation of the system.

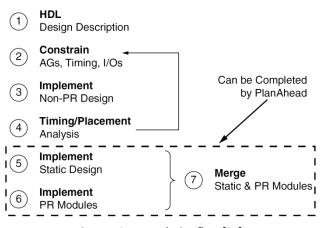

#### 2.3 Xilinx Tools

Since in this work a Xilinx FPGA was used, the provided tools for implementation are briefly described in this section. The main development environment is the Integrated Software Environment (ISE) Design Suite described in 2.3.1. Because the communication infrastructure has to be embedded into a partially reconfigurable design, the Early Access Partial Reconfiguration (EA PR) overlay is needed. In order to floorplan the PRRs and to create the distinct bitstreams for each module and the static design, PlanAhead has to be used. Anoth-

\_

<sup>&</sup>lt;sup>1</sup> During this work, Xilinx announced ISE 12.1, which will support partial reconfiguration designs out of the box and EA PR will become deprecated.

er utilized part of the ISE Design Suite is COREGenerator, which provides specialized IP-cores for Xilinx FPGAs.

In order to implement the low-level part of the design, the Xilinx Design Language (XDL) was used, which is described in section 2.3.2.

#### 2.3.1 ISE Design Suite

The ISE Design Suite is a suite of tools supporting the complete design flow for integrated systems from a high-level description via synthesis and implementation down to final bit-stream generation for the FPGA device. Most of the tools can be accessed out of the Project Navigator which is the main interface to the user. Nevertheless, there are some additional tools like COREGenerator (2.3.1.1), PlanAhead (2.3.1.2) and FPGA Editor (2.3.1.3) which provide their own, complex interfaces.

However, the ISE Design Suite was intended for conventional (static) designs not involving partial reconfiguration, so some changes have to be made. Xilinx introduced the EA PR overlay for this purpose. The most important modification applied by this patch is to check whether for all signals, which pass the border of a PRR, a bus macro is used.

#### 2.3.1.1 COREGenerator

COREGenerator is a design tool that delivers parameterizable IP-cores optimized for Xilinx FPGAs. The documentation for COREGenerator is split into several independent guides for the separate cores. For this work the FIFOGenerator [8] was used to create FIFO buffers as described in section 4.3.2. COREGenerator is an easy way to include IPs into an ISE design and provides a lot of licensed as well as free IP-cores.

#### 2.3.1.2 PlanAhead

PlanAhead is a powerful layout and floorplanning tool for FPGA designs. The steps between synthesis and place-and-route are streamlined in order to provide more control over how the design is implemented. In particular, the complicated handling of partially reconfigurable designs is eased via a hierarchical design methodology.

#### 2.3.1.3 FPGA Editor

The FPGA Editor provides a detailed graphical view of all FPGA components and the routing resources. It can be used to view and explore a placed and routed design, and facilitates low-level modifications on the logic configuration and interconnections.

#### 2.3.2 XDL

XDL was intended to be a human readable low-level design language providing full control over all FPGA primitives and connections [9]. Although XDL was never developed further and all documentation vanished with the release of version 7 of the ISE suite, the original functionality and the conversion tool are still available in current releases. Basically, XDL provides the same level of access to FPGA resources as the FPGA Editor does, but unlike using the FPGA-Editor it is feasible to create large designs efficiently. XDL source code should not be written directly; instead any scripting language can be used to create the XDL code for the design.

The result can be converted to a Xilinx NCD file, which can contain all placement and routing information. If designed with care, direct conversion into a bitstream and configuration of the FPGA is possible. A more useful approach is to convert the NCD into a *hard macro* (NMC file). Hard macros can be instantiated as black box modules within ISE using any hardware description language like Verilog or VHDL. See section 4.4 for more information about this design flow.

#### 2.4 Interconnects

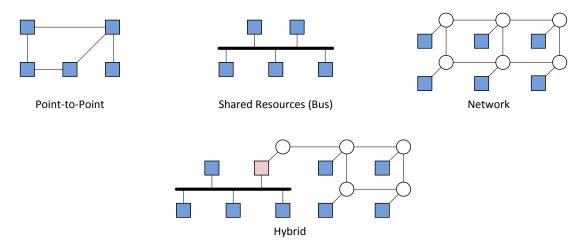

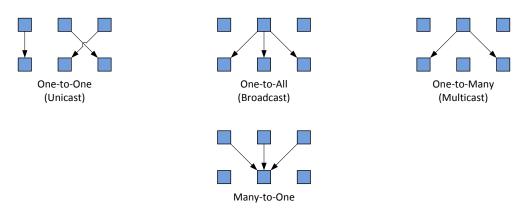

Several possible interconnection methodologies exist to provide communication between different modules. Basically, they can be distinguished between four groups: point-to-point connections, shared resources, networks and hybrids of the former as sketched in Figure 2.2.

Figure 2.2: Interconnection methodologies

#### 2.4.1 Point-to-Point Connections

The simplest interconnection methodology is to provide separate wires for every connection that has to be made. Since nothing has to be shared this approach promises to achieve the best performance. On the other hand a huge amount of resources is needed and this approach scales poorly for larger numbers of modules.

#### 2.4.2 Shared Resource

A typical shared resource is a bus. All modules are connected to this shared element, but access is provided exclusively to one element only and arbitration is necessary. Furthermore, all communication is synchronized by a certain clock, so all modules are either restricted to use the same clock, or retiming has to be performed by the modules. Additionally, shared resources are characterized by poor scaling as well, since the infrastructure is saturated if a certain number of components is reached: throughput may be high for a small number of elements, but performance will significantly decrease when the components block each other from communication. Furthermore, assuring fairness is another issue that cannot be solved easily. Complex mechanisms like priority levels must be introduced; otherwise a less important module could prevent on-time delivery of critical messages just by continuously requesting the communication resource.

#### 2.4.3 Network

In a network, the distinct modules are no longer connected directly by one or more wires, but a series of switching elements in between is introduced. Networks are much more flexible and scalable than point-to-point interconnects or shared resources. A popular example for a network involving a huge number of heterogeneous components is the internet. However, due to advances in integration density and increasing chip complexity networks are becoming an appropriate solution for on-chip interconnects as well. Such a network is referred to as Network-on-Chip (NoC).

The group of network-based interconnects can be further distinguished by mainly three characteristics as proposed by Salminen et al. in  $[\underline{10}]^2$ : switching characteristic (2.4.3.1), topology (2.4.3.2) and routing (2.4.3.3).

\_

<sup>&</sup>lt;sup>2</sup> Salminen et al. refer to point-to-point connections and buses as network topologies. In this work they are not considered to be networks due to the lack of switching elements.

#### 2.4.3.1 Switching Characteristics

The switching characteristics can either be *circuit*- or *packet-switching*. Circuit switching means that before sending data, a dedicated path which is referred to as *channel* has to be established from the source to the target. Every network segment used for a certain channel cannot be used for another channel at the same time. As long as no changes are made to this allocation, the network behaves and performs similarly to point-to-point interconnections. Nevertheless, there is some overhead to construct the channel.

When using packet-switching, the segments within the network are shared by several connections. Therefore, the data is split into several *packets* and additional information about the source, target and the content is added within a *header* to allow correct delivery. The switching elements forward packets according this information and are referred to as *routers*. This technique promotes high flexibility and optimizes the utilization of the resources: connections are not bound to a specific channel and alternative routes may be taken. Workload can be distributed evenly throughout the network, failing components can be avoided and advanced features such as different priority levels are easy to implement. However, this comes with a lot of overhead: with every packet, additional data for the header is required and the packets have to be processed by every router along the path. This results in low throughput, and latency increases. Furthermore, routers are rather complex and require more area and power than the switches of the former approach. Finally, additional issues like packets arriving in the wrong order may have to be considered.

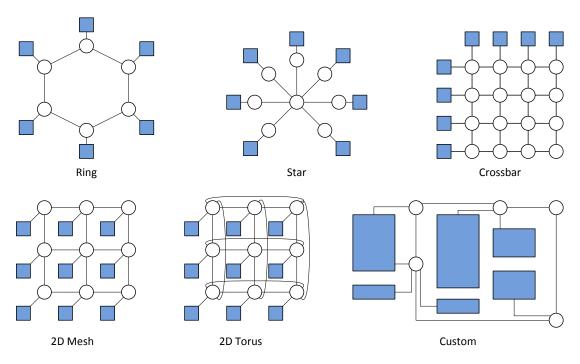

#### 2.4.3.2 Topology

A wide variety of network topologies has been studied. Some popular examples are given in Figure 2.3.

Figure 2.3: Network topologies

Each topology can be implemented using either circuit- or packet-switching. However, some topologies suggest a specific approach. The ring, for example, behaves poorly if implemented using circuit switching: if, without loss of generality, a channel is established to connect the modules on top and bottom, the remaining modules on the left or the right are completely blocked from communicating since there is no segment available to connect them. On the other hand, the crossbar as depicted in Figure 2.3 should be implemented using circuit-switching, since otherwise the overhead due to packet processing is needlessly large.

#### 2.4.3.3 Routing

According to [10] routing can be *deterministic* or *adaptive*. Deterministic means that all data routed between two given modules always follows the same path through the network. When adaptive routing is implemented, different packets between the same modules may take different routes. It is obvious that routing in circuit switched networks is always deterministic, as long as the channels remain established. However, if a channel between two modules is torn down and then reestablished, other segments may be used. If this is the case, a circuit-switched network may be adaptive to a certain extent. As always, adaptive routing offers more flexibility and fault tolerance but also involves additional issues like out-of-order delivery as mentioned previously.

#### 2.4.4 Hybrid Interconnects

Hybrid interconnects combine one or more of the former approaches. For example, in order to create a hierarchy within a multiprocessor system, a bus could be used to connect each processor with a local cache, peripherals and a network interface, and a network could be used to interconnect all of these interfaces to provide inter-processor communication.

The main advantage is that positive attributes of several architectures are combined. In the example above, the bus can provide low-latency access to the components, but only as long as the number is small. Thus, a network is introduced in order to overcome scaling problems of the bus architecture. For another example it may be assumed that a system requires high throughput for application data, but low latency is necessary for some synchronization messages as well. In this case several point-to-point connections could be used for the time-critical messages, while a high bandwidth network is responsible for the application data.

The main drawback is reduced flexibility of the architecture. When several methodologies are combined like in the examples above, the resulting interconnect is optimized for a certain situation but may be inappropriate for other cases.

## 3 Related Work

In the field of interconnects for partially reconfigurable systems, several solutions have already been proposed. Although a Network-on-Chip may be favored for flexibility and scalability reasons over rather simple structures like buses, actual platforms for partial reconfiguration like the Erlangen Slot Machine (ESM) [11] and the work of Ullmann et al. [12] are still using less complex approaches. The reason is the following: in order that benefits can outweigh the drawbacks introduced by a NoC, a system of more than just a few modules has to be designed: as long as the number of modules involved in communication remains small, the overhead introduced by additional switches and management is comparatively high. But actual systems being implemented on FPGAs currently do not utilize more than a low number of PRMs; using a NoC is disadvantageous not only in respect of implementation complexity but also in bandwidth, delay and area.

Because of this, the communication infrastructure used by the ESM is introduced in section 3.1 as an example. This infrastructure is called Reconfigurable Multiple Bus (RMB) [13] and was further developed into an easy-to-use solution for both dynamically reconfigurable and static System-on-Chips referred to as ReCoBus [14]. Subsequently, two different Network-on-Chips are analyzed. The first proposal by Marescaux et al. presented in section 3.2 was published in [15] 2002 and further developed in [16] one year later, while CoNoChi (Configurable Network-on-Chip, [17]) surveyed in section 3.3 is a more recent approach, which really exploits the capabilities of partial reconfiguration. Finally, in section 3.4 the implementation of a high-performance crossbar-switch targeting Xilinx FPGAs [18], just like the subject of this work but in a static context, is examined.

#### 3.1 ReCoBus

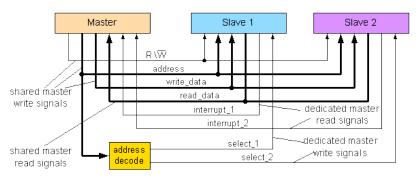

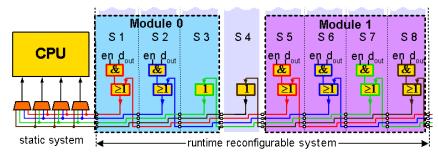

The ReCoBus architecture was designed to provide inter-module communication within a partially reconfigurable platform, but can also be used in static SoCs. All classes of bus signals that follow established on-chip standards such as AMBA and CoreConnect (*shared* and *dedicated read/write*) are supported. The interface of the bus is depicted in Figure 3.1.

For each module, dedicated interrupt and selection signals are supplied. Furthermore, shared read/write data buses as well as an address bus exists, and one signal specifies whether in the current cycle the bus is driven by the master (write) or by slaves (read).

Figure 3.1: ReCoBus interface [19]

For the PRRs into which modules can be placed, it is proposed to divide the reconfigurable FPGA area into several *slots*. These slots should be rather narrow, to provide a higher placement flexibility for modules that span one or more slots. Furthermore, narrow slots reduce the internal fragmentation of the modules, since the region boundaries can be tightly placed around the module. An interface has to be given at an exactly known location within each slot, so that any of them is universally valid for all arbitrary modules.

The ReCoBus is delivered as one single hard macro, which is completely placed and routed. In doing so, adding and removing modules is similar to plugging/unplugging boards into the fixed PCI slots of some desktop computer. This provides a simple abstraction for working with partially reconfigurable modules. On the other hand, the place and route process of the remaining static design is made more difficult, since several resources are unavailable. For example, if a certain hard macro wire is also required for a critical connection in the static design, it is not possible to consider reallocation of this wire. Upon other terms, different allocations of this wire could be evaluated in order to optimize overall performance.

#### 3.1.1 Design and Implementation

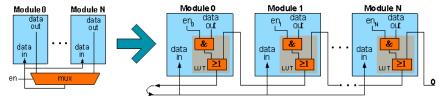

A special issue has to be solved when implementing the shared read signal. For a shared read, a bus multiplexer has to be provided for each data line. A possible implementation for several slots can be a multiplexer chain as shown in Figure 3.2.

Figure 3.2: ReCoBus shared read multiplexer [19]

But because it is desired to have narrow slots, the slot count will be higher than the number of modules. As a consequence, the logic overhead for the chained structure is very high, and

even more important, the combinational path is long and signal propagation takes more time. This issue was solved using interleaved multiplexer chains such as in Figure 3.3.

Figure 3.3: ReCoBus multiplexer interleaving [19]

In this example, four interleaved multiplexer chains are provided. Although 8 slots exist in the system, each chain is only 2 segments deep. It is also clear from this example, that in order to provide a specific interface width, the module has to span a minimum number of slots. Assuming that each multiplexer chain represents a set of 8 signal wires, the bus provides a total width of 32 bits and at least four slots have to be used by a module, to access the full bandwidth. However, this is considered to be noncritical, since practical experience showed that the interface width is usually related to the complexity of a module. So if a wide interface is needed, the module is probably complex (=large) and will utilize several slots anyway.

#### 3.1.2 Evaluation

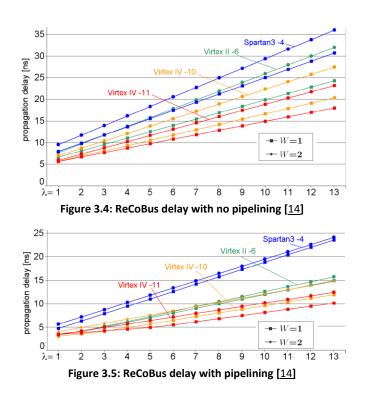

Despite using interleaved multiplexer chains, the worst-case delay is still very high. In [14] the propagation delay of this critical path for a 32-bit wide bus with 4 interleaved multiplexer chains is evaluated as shown in Figure 3.4. The entered parameter  $\lambda$  resolves to  $\frac{R}{N}-1$ , whereby R is the number of available slots and N is the number of interleaved chains. W in the graph refers to the width of each slot in number of CLBs.

For a high-performance bus clocked at a frequency of at least 100 MHz, the propagation delay must be lower than 10 ns. With no further optimization, this bus could not be used to connect more than 16 slots on most FPGA devices. To overcome this problem, pipeline stages were added. After applying this enhancement, the propagation delay was reduced considerably as visible in Figure 3.5. A test system has been implemented on a Virtex-II device using the enhancements just mentioned. The system consisted of 8 slots being 2 CLBs wide and a bus of 32 bits. Each slot contained a very simple test module like a counter or an adder. The achieved data rate was reported to be 800 MB/s at a clock speed of roughly 100 MHz.

### 3.2 NoC: Work of Marescaux et al.

The Network-on-Chip proposed by Marescaux et al. is intended to be a communication infrastructure within a SoC for application data only. This means control and configuration data for the system is supposed to use other infrastructures concurrently existing on the chip. Control of these networks is achieved by a so-called operating system for reconfigurable systems (OS4RS) [20].

Only the network for application data is examined here. It uses packet-switching and the topology can be chosen, but is fixed during runtime. In addition, a specific routing algorithm is realized. As always, the main network components are the routers. But besides these, separate network interfaces called *net cells* are used to wrap each module.

According to [15], the tightest constraint for an on-chip network is the limited space on the single chip. Most network interconnects realized in the past target multi-chip circuits and can be found in the world of multi-processor computing. In this case, however, the communication architecture has to be implemented together with all remaining components within a single FPGA. So the main challenge for the NoC design is to keep the resource overhead

low. Therefore, the components were designed to be as simple as possible. The following design decisions are affected by these restrictions.

#### 3.2.1 Routing

According to the classification in section 2.4.3.3, a deterministic routing algorithm is implemented; nevertheless a decent amount of adaptability is provided. This is offered by routing tables attached to each router (see section 3.2.2) which can be modified during run-time by the operating system. Virtual cut-through is used as the switching technique: when a packet arrives at some router, forwarding can already be started before the packet has been received completely. In this way, the latency of the network is reduced. Virtual cut-through is commonly implemented by splitting the packet into several so-called *flits*, prepended by a header. Wormhole routing is a very similar approach; the major difference is that with virtual cut-through it must always be guaranteed that a packet can be transferred as a whole. This allows flow control at packet level, but large buffers capable of containing a complete packet must exist throughout the network, since forwarding may be blocked: if packets from different sources have to be forwarded to the same target this cannot occur simultaneously. Because of this, each router has to check whether the target is ready to receive, before transfer can be started. This is done by dedicated handshake signals between adjacent routers.

#### 3.2.2 Routers and Topology

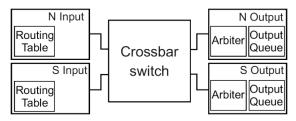

As mentioned before, the routers are the main building blocks in the network. Each router is individually parameterizable in the number of input- and output-ports. All of these ports are fully identical; no distinction is made whether another router or the network interface of a module is connected to a given port. This means that all functionality required for higher levels of communication than physical addressing can be implemented within the network interface of the module, which keeps the routers simple. By leaving the number of ports customizable for every router, different topologies can be created. For example in order to realize a 2D-Torus as shown in Figure 2.3, every router would have 5 input and 5 output ports: 4 are needed to connect the adjacent routers, and one port is used for the interface of the corresponding module.

Packet forwarding to the next router is implemented by a crossbar switch, which is contained within every router and can connect any input to any output port. An example is given in Figure 3.6 for a 2 input/2 output router.

Figure 3.6: NoC router with 2 input and 2 output ports [16]

It is also shown in this picture that one arbiter and one output queue is attached to each output port. The arbiter is needed to select the input port, which is currently allowed to store data in the output queue if multiple inputs have to be connected to the same output. The output queue is necessary, since packets have to be stored when blocked. This can occur because of the chosen routing algorithm, which is also the reason for having one routing table attached to every input port.

#### 3.2.3 Network Interface

The purpose of the network interface is to decouple the module from the communication network, which allows using different clock speeds for the distinct components of the system. Therefore, buffers capable of containing several messages are provided. Furthermore, high-level services like virtual addressing and packet redirection can be implemented in the interface. In the first version of this architecture, even the routing tables were included in the network interface and routers were forwarding the packets only by a given number of hops in X and Y direction.

#### 3.2.4 Evaluation

Not much information was provided about the resources, used to implement one router on a Virtex-II Pro device. According to [16], somewhat more than 500 slices are used to implement one router having 5 input and 5 output ports, but additionally BlockRAMs are needed for the message queues. However, the amount of slices used increases quadratically with the number of ports due to the growing crossbar switch size and the arbiters needed for each output port. Unfortunately, nothing is said about the bit with of each provided port. Furthermore, no statistical data is given for the network interfaces (net cells).

The network latency is kept low by using virtual cut through switching. Processing the header flit including handshakes and setting the crossbar switch takes three clock cycles. Every following clock cycle one flit is transferred. So the latency is equal to three times the number of hops plus the number of flits for the packet. This appears to be rather low, but is valid only as long as the packet is never blocked. Latency decreases considerably, as soon as con-

current traffic occurs in the network. However, this is exactly what has to be expected when a packet-switched network is chosen instead of less flexible infrastructures. According to [16] the maximum clock speed for the network is 50 MHz, which results in data rates of around 100 MB/s between adjacent routers when a bit width of 16 is assumed per port.

# 3.3 NoC: CoNoChi

Contrary to the approach of Marescaux et al, CoNoChi is intended to be the only communication infrastructure within a given SoC. Thus, it has to be flexible enough to satisfy both the needs for application- and configuration data<sup>3</sup>. A high degree of flexibility is achieved via a complex routing mechanism, which includes several network layers and supports different message classes for prioritization and quality of service (QoS).

The routers are the main components of the network, again, and packet-switching is used to distribute the data as well. A separate network interface exists for each module, but not much is said about this element, apart from the fact that it is module-dependent and thereby implemented within the PRM.

However, the main difference to the former approach is adaptability of the topology. This is not only possible by parameterization during design time, but can be done dynamically during runtime. This allows the number of overall routers to be minimized in order to keep the area overhead low.

#### **3.3.1** Routing

A much more complex network protocol is implemented compared to the work of Marescaux et al. First of all, two different addressing methodologies exist: physical addressing, which refers to a specific router within the network topology, and logical addressing, which specifies a so-called *processing unit*. This can either be a PRM or part of a PRM. Routing is based on the physical address only and similar to the former approach, routing tables are used again. Furthermore, a deterministic algorithm is implemented, and adaption is enabled by updating the tables. However, in this case the same network is used to distribute routing tables as for the application data. Packets containing configuration data belong to a special message class and can be distinguished from common application data. Routers recognize these packets and update their routing table if the physical address of the packet matches their own address. Some details are given about the algorithm that is used to calculate the

\_

<sup>&</sup>lt;sup>3</sup> While application data usually requires high bandwidth and may suffer from some latency, configuration data must be delivered in the shortest possible time but consists of only a few bits

routing tables: the Floyd-Warshall-Algorithm is executed by a dedicated control instance<sup>4</sup> which maintains a global view of the network. So routes are optimized in respect of the number of hops by this technique; however the algorithm is very complex<sup>5</sup>. But if the PowerPC, which is embedded on some Xilinx FPGAs, can be utilized, calculation time is noncritical, since updates of the routing tables are only necessary if some reconfiguration has to be done, which will take longer anyway [17].

Packets are always forwarded as a whole, and no technique like virtual cut-through or wormhole routing is implemented in order to reduce latency. Receiving, processing and forwarding the packet takes 5 clock cycles in any case.

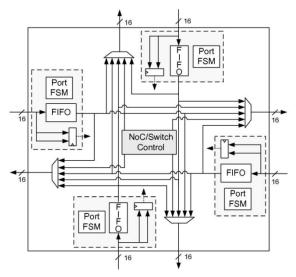

#### 3.3.2 Routers

The basic structure of the router is depicted in Figure 3.7, which is quite similar to the proposal of Marescaux et al. However, only the bit width provided at each port can be customized; the number of ports is restricted to the fixed value of 4 (both for inputs and outputs).

Figure 3.7: CoNoChi router [21]

Because of this, the topology is restricted to a 2 dimensional structure. On the other hand, this goes with the reconfiguration capabilities of recent FPGAs. This is important since the topology is supposed to be adapted during runtime as described in section 3.3.3. Furthermore, all ports are homogeneous and can be connected either to another router or the interface of one module. However, not more than one module can be connected to the same router.

-

<sup>&</sup>lt;sup>4</sup> part of an OS4RS or a static hardware component

<sup>&</sup>lt;sup>5</sup> O( $n^3$ ), whereby n is the number of edges in the graph ( $\lambda$  links in a network)

Corresponding to the message queues in the work of Marescaux et al, FIFOs are provided as buffers, which are large enough to store a complete packet. However, packets are stored at the input and not at the output port. Thus only one arbiter is needed per router (labeled as *switch control* in Figure 3.7). Furthermore, there is only one routing table and no distinction on which port a packet has arrived is possible. But multiplexers are used again to connect every input port with all possible outputs.

# 3.3.3 Topology and Adaptability

As already stated in the previous section, only 2-dimensional topologies can be realized, since the number of ports is fixed. In return, CoNoChi supports adaption of the network topology during runtime by dynamically adding or removing routers from the network. Even the size and location of PRRs can be changed. A detailed description of how this technique is realized can be found in [22]; the specific design flow for Xilinx FPGAs is described in this paper as well. Since several limitations exist for the few tools available to create a partially reconfigurable design, it is an extensive process to create such a system. It might be argued that the additional effort is not justified by the gained flexibility.

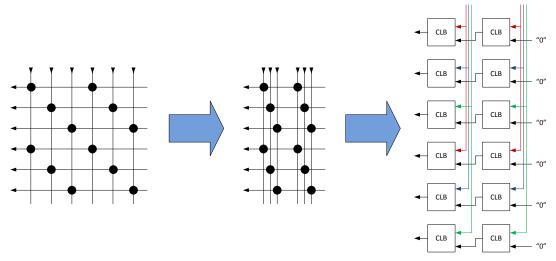

The basic procedure is to initially divide the FPGA area into several PRRs of the same shape and size, which results in so-called *tiles* as shown in Figure 3.8. These tiles represent the smallest reconfiguration granularity and must be large enough to contain a router. In addition, some static components might reside in a separate region of the chip. Any tile can be configured to be one of four basic building blocks: horizontal or vertical connection wires, a router or the part of a module. Afterwards, bitstreams have to be created for every component and for every tile that is a possible target of this component.

#### 3.3.4 Evaluation

A prototype of the network was implemented on a Virtex-4 device and revealed that 480 slices are needed for the router, which is hardly affected by the bit width provided. In addition, 4 BlockRAMs are required for the FIFOs and routing tables. Because of this, one tile was chosen to be 12 by 16 CLBs large, which is aligned to the reconfiguration capabilities of the Virtex-4 and provides enough resources to contain a router: 192 CLBs contain 768 slices; furthermore 8 BlockRAMs were available on the specific device per tile. However, a significant area overhead is introduced by this approach: especially if a tile contains horizontal or vertical connection wires, the resources are poorly exploited.

The maximum clock speed that could be achieved for the routers of the prototype system was 159 MHz.

Figure 3.8: CoNoChi architecture [22]

# 3.4 Xilinx Crossbar Switch

The network architectures introduced so far use packet switching. As mentioned before, this technique introduces some control overhead with every packet that is sent. Circuit switching, on the contrary, introduces overhead only for establishing the channel, afterwards data is transferred more efficiently. A typical example for a circuit-switched network is the crossbar switch. In this work it is examined whether this approach is an adequate solution for partially reconfigurable systems, and a custom crossbar switch is designed for this purpose. However, there are several crossbar switch implementations available, which do not target a reconfigurable environment. The Xilinx Crossbar Switch introduced in this section was motivated by a customer's need for a very large crossbar switch, and a very efficient implementation technique was required.

## 3.4.1 Crossbar Switch basics

An  $n \times m$  crossbar switch refers to a structure that is capable of connecting n inputs to m outputs in a matrix manner: traditionally, several switches are arranged in a matrix (see Crossbar in Figure 2.3) and can be switched to short-circuit a horizontal and a vertical wire in order to connect one output with one input. For an  $n \times m$  crossbar being capable of connecting any input with any output simultaneously, the considerable number of  $n \times m$  so-called *cross-points* must exist. A straightforward implementation uses large multiplexers for every output which is used to select one of the inputs. However, this requires enormous

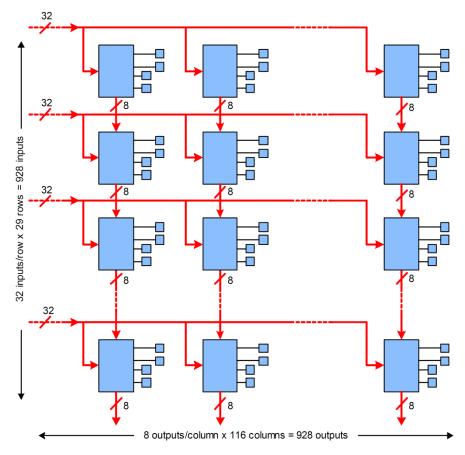

resources and when regular FPGA logic is utilized (slices and LUTs), limits are quickly reached: As described in [18], a 928 × 928 crossbar switch was required, which had to be capable of connecting any input with any output. Within one 4-input LUT a 2:1 multiplexer can be implemented by using one input as select line determining which of the two other inputs is mirrored to the output. Since there are 8 LUTs within one CLB, a 16:1 multiplexer can be implemented within this CLB. Accordingly 58 CLBs are needed for a 928:1 multiplexer. Replicating this multiplexer for every input, 58 × 928 = 53.824 CLBs would be needed. One of the largest FPGAs available at that time, a Virtex-II XC2V6000, provides 8.448 CLBs; the more recent Virtex-4 VLX160 used in this work, as well one of the largest devices in his family, has 16.896 CLBs. Obviously this is not enough for the required design.

In [18] the issue was solved using the routing fabric as logic resource. The main component responsible for flexible routing in Xilinx' FPGA architecture is the so-called *switch box*. Actually, this component is getting close to the original idea of a crossbar switch with horizontal and vertical wires. On Xilinx FPGAs these cross-points are called *programmable interconnect points* (PIP), and their state is selected within the configuration bitstream.

## 3.4.2 Design and Implementation

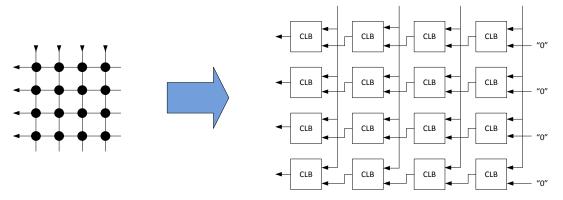

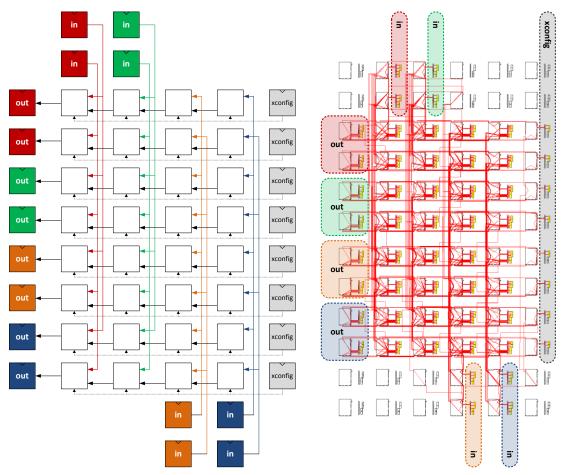

A detailed description of how the Xilinx Crossbar Switch was implemented can be found in [23]. Basically, by utilizing the switch box attached to every CLB, any of the 33 inputs can be connected to at least one pin of every LUT in the CLB. When the remaining inputs of the LUT are tied to logic "1" and the LUT is configured as an *and*-gate at the same time, any of the 33 inputs of the switch box can be selected for the LUT output. Following this technique, every LUT can represent a 33:1 multiplexer together with the switch box. If only 32 of the 33 inputs are utilized the  $928 \times 928$  crossbar switch can be implemented using only  $29 \times 116$  CLBs as depicted in Figure 3.9 ( $29 \times 32 = 928$  inputs,  $116 \times 8 = 928$  outputs). However, this structure was further modified in order to improve the aspect ratio of the utilized are. As a result, a square region of  $58 \times 58$  CLBs could be achieved. Furthermore, pipeline stages were included, which enabled higher clock speeds. The netlist for the specific FPGA was created using XDL (see section 2.3.2).

Since the cross-points are not implemented using conventional logic, updating the switch configuration cannot be realized by changing register values or by any other straightforward approach. Instead, the FPGA must be reconfigured in order to change the state of the PIPs and content of the LUTs. But using the convenient flow for partial reconfiguration (EA PR) is not possible: a bitstream had to be generated for every possible combination of switch set-

tings (928<sup>928</sup> altogether), which is not feasible. If bitstreams were generated in advance, a lot of space would be needed for storing. But complete bitstream generation during runtime is not feasible as well, since the place and route process is very complex and time consuming. The solution was to use JBits, which is a java-based application that is capable of manipulating bitstreams. However, JBits is deprecated and does not support bitstreams for devices more recent than Virtex-II.

Figure 3.9: Xilinx Crossbar cascaded structure [23]

# 3.4.3 Evaluation

The final 928  $\times$  928 crossbar switch was successfully implemented on a XC2V6000 device and occupied 60% of the resources on this FPGA model. A clock speed of 155.5 MHz could be achieved on all channels. This results in an aggregated throughput of 144.3 Gbits/sec, but unfortunately no value is specified for the latency of the structure. A new switch configuration could be written to the device within 220  $\mu$ s.

# 3.5 Conclusion

Specific architectures were described in this chapter for the basic bus and network interconnection methodologies. It is apparent that each of the proposals introduces certain pros and cons.

The bus implementation stands out for implementing established standards beeing used in real partially reconfigurable platforms and exceeding the stage of a prototype. This corresponds with the fact that buses are the most widely used structure for static system-on-chips. There is no reason to expect a completely different trend for partially reconfigurable systems (PR systems) which are now emerging. It is merely logical that familiar structures are explored in the very beginning. Furthermore, a bus is quite a simple structure, causing a minimal area overhead and it is easy to use, since just a few fundamental protocol definitions have to be obeyed. But on the other hand, buses are neither scalable nor very flexible, as pointed out in 2.4.2. However, scalability becomes more important with larger SoCs which involve a larger number of more varied components. Flexibility, on the other hand, is needed particularly in a partially reconfigurable system: since certain parts can be changed during runtime, the communication structure should be able to satisfy changing requirements.

Because of this, Networks-on-Chip have appeared as another approach. They provide a much greater scalability and flexibility. Just like the architectures described in this chapter, most other NoC proposals use packet switching, which further enhances these characteristics. Obviously, the major drawback of this approach is the overhead that is introduced both for area and packet processing. But there are still other problems which have not yet been mentioned. Not only is the interconnection more extensive, but the complexity of the connected modules also increases, since the involved overhead applies to them as well. Besides identifying the source of a packet in order to recombine data belonging together, reordering might be necessary within the module, since just a few NoCs provide mechanisms for this. Accordingly, splitting messages into several parts to comply with the maximum packet size is often delegated to the module. The same applies to creating the appropriate headers. Furthermore, it is still an open question whether this higher flexibility is actually needed: it might be argued that even in a partially reconfigurable SoC the communication needs remain predictable to a certain extent, since modules are still working together to execute certain, well-known tasks. But packet-switched networks can play out their strengths particularly in the case of a very large number of participants being completely independent from each other. This does not apply to current PR designs, just because the required integration density for such large systems cannot yet be achieved on FPGAs.

Circuit-switched networks can be considered as an intermediate solution. In contrast to packet-switched networks, sophisticated module interfaces are not required and the control overhead is considerably lower. In addition, more flexibility is possible than with a bus. On the other hand, a new problem may arise as already stated in 2.4.3.2: depending on the network topology, certain components might be prevented from receiving or sending data, even though both communication partners are idle. The crossbar topology circumvents this situation. However, the area overhead is worse again, since it scales as the square of the number of connected modules. Otherwise, it was shown by Xilinx that implementing a very large crossbar switch is possible on FPGAs. Because of this, the behavior of a crossbar switch in a partially reconfigurable system is explored in more depth within this work.

Unfortunately, the Xilinx Crossbar Switch is not applicable for a practical analysis. First of all, it was not designed to be used in a PR design. While this issue could be solved by some modifications, another more serious problem prevents the usage of this solution: the Xilinx Crossbar Switch architecture is incompatible with recent FPGA devices, since partial reconfiguration has to be accessed in an extraordinary manner. As stated in section 3.4.2, bit-stream modifications are done during runtime using JBits, which is deprecated. It seems to be rather futile to use an old Virtex-II with limited partial reconfiguration capabilities for present day investigations. Decoding the appropriate parts of the bitstream for the provided Virtex-4 FPGA was also considered to be going beyond the scope of this work. Instead, a custom architecture, as discussed in the next chapter, was designed.

# 4 Design

For the reasons given in section 3.5, it was chosen to investigate the use of a crossbar switch as an interconnection in a PR system. A new crossbar switch, referred to as *XBar*, was therefore designed and is described in this chapter. First, the requirements for the interconnection are explained, followed by the major design decisions and a reasoning of the choice. Subsequently, the architecture is explained in detail and information is provided on how to embed the crossbar switch into a custom design.

# 4.1 Requirements

Several requirements apply to the communication infrastructure. Some of them address the unique requirements of partial reconfiguration; others apply to conventional inter-module communication as well. Furthermore, some additional conditions were assumed, which have no general validity, but are required as a consequence of the current state of technological development. However, some requirements are mutually contradictory, and a tradeoff has to be made.

**Small area overhead.** The FPGA area utilized for the communication infrastructure should remain as small as appropriate. Even though devices are getting larger, the possible modules to be implemented do so as well. Furthermore, less area overhead results in higher speed, since delays are reduced and lower costs follow when smaller FPGAs can be used. Finally, power consumption is reduced as well. On the other hand, constraining the available resources always affects the maximum bandwidth that can be achieved.

**High bandwidth.** Communication between modules may require high bandwidth. In particular, accelerators for multimedia or network applications are often processing data streams that cannot be buffered for a long period of time, since new data arrives constantly. Bandwidth can be increased by providing more wires per interface (= area overhead) or raising the clock speed, which requires additional pipeline stages (= higher latency).

**Low latency.** Communication between modules may require low latency. If modules perform handshakes for synchronization, the appropriate signals must have a low delay in order to work efficiently. For example, a buffer-full-signal is useless when it arrives several cycles too late.

**Fast switching.** The time, which is required to establish a new channel or change the destination of an existing one should be short in order to avoid large overheads when communication patterns change frequently. However, at this stage rather fixed channels are assumed, but more flexible switching to new configurations must not be prevented by the architecture (see also *external control* below).

**Support for different communication patterns.** There are four basic communication patterns that may occur between modules as depicted in Figure 4.1. Any of these cases should be supported without introducing high overheads like sending the same information multiple times.

**Figure 4.1: Communication Patterns**

**Support for different clock speeds.** The connected modules might run with different clock speeds, so the communication infrastructure must provide asynchronous interfaces. Any module should be able to send or receive data depending on its local clock, and should not be constrained by a global communication clock.

**Uniform PRRs.** It should be possible to configure a module into any PRR using the same module implementation<sup>6</sup>. This can be achieved by providing a universally valid interface, which is independent of the associated region.

\_

<sup>&</sup>lt;sup>6</sup> This does not mean that the respective bitstreams are also equal. This may not be possible, because signals of the static design might cross the PRRs at different locations.

Limited number of PRRs. It is assumed that the number of partially reconfigurable regions does not exceed 8. The main reason for this assumption is to ease the prototype implementation, which would be much more complex if more regions would exist: several additional precautions would have to be taken which might be neglected with this simplification. Other reasons for this rather conservative assumption are the problems that occur when a higher number of PRRs is involved on a single FPGA. First of all, available resources are still a limiting factor and it is not possible to provide a high number of partially reconfigurable regions without the need to split some modules to span over more than one region. But this would lead to a complex module design, which should be avoided. Secondly, actual constraints that apply to partial reconfiguration require a distinct bitstream for every PRR. When the number of regions is increased, the number of bitstreams that has to be stored for every module grows accordingly. Furthermore, actual application scenarios for partial reconfiguration only involve a certain number of modules which operate *in parallel*. This assumption does not mean that the overall number of different modules has to be small.

**External control.** At this stage of the work it is assumed that reconfiguration management and setting up the connections is dedicated to an external controller. However, this is not applicable in all cases. It may be necessary that a module can establish a new channel to another module on demand and without introducing high communication overhead. The architecture of the crossbar should be designed in such a way that adding a module-driven control interface is feasible at a later date.

# 4.2 Design Decisions

The final design, which is described in section 4.3, is affected by some fundamental decisions which are discussed below. Predominantly they are justified by the requirements defined in the first section of this chapter.

**Use circuit switching.** Circuit switching was chosen as the switching characteristic of the design. This option is quite obvious because of the topology associated with a crossbar – there are many more interconnection wires and switches than modules. Actually, the number of cross-points and links grows quadratically. This only makes sense if communication is realized by exclusive channels between the modules: since alternative links exist, other components are not prevented from communicating despite the fact that some links are already assigned to other channels. In contrast, if packet-switching was

used, interconnections could be shared, and the additional links would not be exploited efficiently.

Parameterize interface width and number of PRRs. As mentioned before, providing a high bandwidth affects the utilized area and vice versa. This issue cannot be solved in general and is tackled by providing a parameter for the bit width of the interface, which is the crucial factor. This allows the trade-off to be done by the user according to his constraints. However, the value applies to the interface of all PRRs, because all of them have to be equal in order that modules can be similarly placed in any PRR. The overall number of PRRs is parameterized for analogous reasons.

Bundle wires to reduce complexity. Channels cannot be established on a per-wire level. Instead, if one module should be connected with another one, a channel providing a bit width of a multiple of 7 must be established. This particular value results from some constraints arising during implementation: an efficient cross-point implementation exists for bundles of 8 wires (see section 5.1). However, one wire is needed for indicating data presence (see section 4.3.4). As a result, each interface of n bits is divided into  $k = n \div 7$  bundles which can be switched independently. However, this removes some flexibility and channels might not be fully exploited, for example when a bundle is used to implement a single handshake signal. On the other hand, the overhead to manage connections is significantly reduced. An efficient implementation of the control logic would be hindered by a finer grained switching mechanism. Furthermore, it can be expected that the proportion of modules requiring only a very narrow channel will be low: very short messages usually contain control information, which are typically associated with some additional payload. Because of this, cannels often have to be wider anyway.

Remove certain cross-points to reduce area and wire delay. A crossbar switch consists of a large array of cross-points. If there is one of these switching elements for every pair of wires or wire groups, their number will be large: if N is the number of modules and k is the number of bundles per module,  $k^2 \times N^2$  cross-points are needed. Unfortunately, every additional switch not only causes an increase in area, but also in propagation delay. However, it might be feasible to improve this structure: in the case that it does not have to be possible to connect every input with every output, several cross-points may be removed. Of course, this precondition does not apply without constraints: it must always be possible to connect any module with any other module, regardless in which PRR it is placed. Furthermore, the interface must remain universally valid: if bit n of interface i can be connected to bit i of interface i, it must be possible to access bit i of

any other interface in some way as well. According to these requirements, certain cross-points were excluded as described in section 4.3. Afterwards, only  $k \times N^2$  cross-points remain, which is still quadratically dependent on the number of modules, but only linearly dependent on the provided link width.

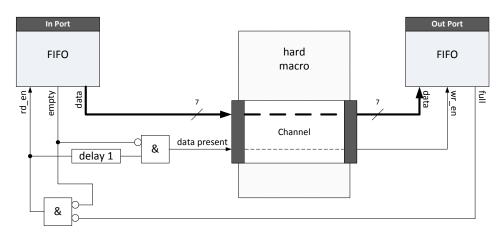

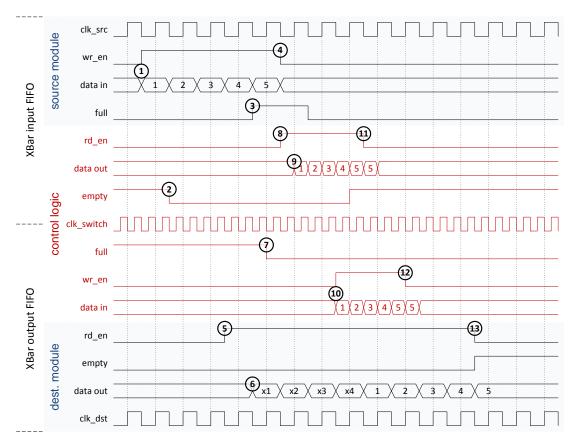

Use buffers between clock regions to allow asynchronous operation. In order to support asynchronous operation of the interconnected modules, data has to be buffered before and after being transferred through the switch. Simple FIFO message queues were chosen for this purpose, because the additional control cost is low. However, distinct FIFOs for the different bundles of each interface are required, because bundles may need to remain independent.