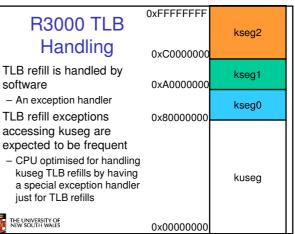

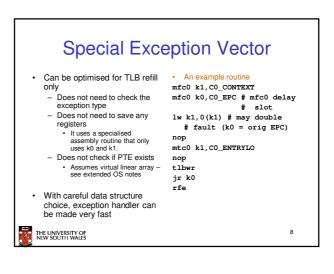

#### **MIPS VM Related Exceptions** TLB refill - Handled via special exception vector - Needs to be very fast · Others handled by the general exception vector TLB Mod · TLB modify exception, attempt to write to a read-only page - TLB Load · Attempt it load from a page with an invalid translation TLB Store · Attempt to store to a page with an invalid translation - Note: these can be slower as they are mostly either caused by an error, or non-resident page. We never optimise for errors, and page-loads from disk dominate the fault resolution cost. 9 THE UNIVERSITY OF NEW SOUTH WALES

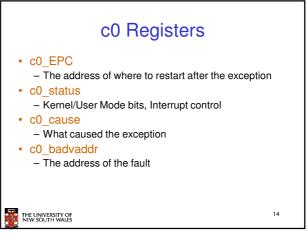

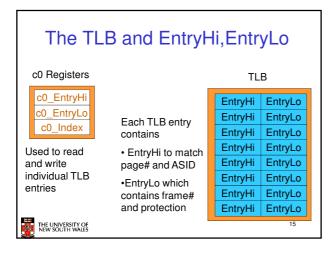

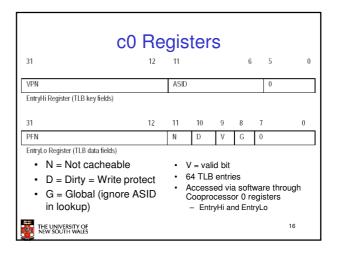

## Cooprocessor 0 registers on a refill exception

### $c0.EPC \leftarrow PC$

c0.cause.ExcCode ← TLBL ; if read fault c0.cause.ExcCode ← TLBS ; if write fault c0.BadVaddr ← faulting address c0.EntryHi.VPN ← faulting address  $c0.status \leftarrow$  kernel mode, interrupts disabled. **c0.PC** ← 0x8000 0000

THE UNIVERSITY OF NEW SOUTH WALES

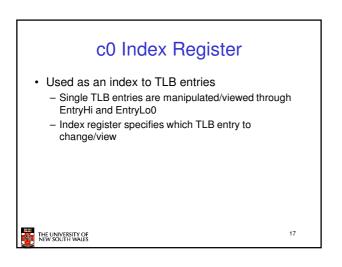

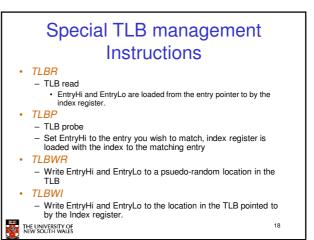

#### Outline of TLB miss handling · Software does: - Look up PTE corresponding to the faulting address - If found: · load c0\_EntryLo with translation load TLB using TLBWR instructions · return from exception - Else, page fault • The TLB entry (i.e. c0\_EntryLo) can be: - (theoretically) created on the fly, or - stored completely in the right format in page table more efficient 20 THE UNIVERSITY OF NEW SOUTH WALES

19

THE UNIVERSITY OF NEW SOUTH WALES

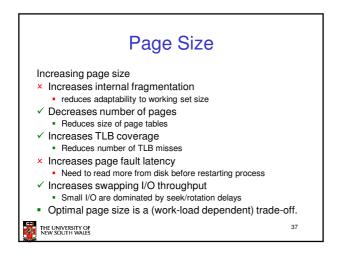

# Working Set Size Generally Increases with Increasing Page Size: True/False?

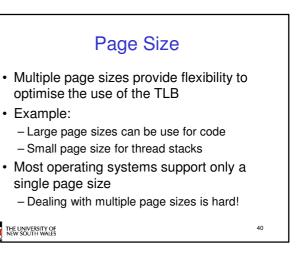

| Atlas             | 512 words (48-bit)             |

|-------------------|--------------------------------|

| Honeywell/Multics | 1K words (36-bit)              |

| IBM 370/XA        | 4K bytes                       |

| DEC VAX           | 512 bytes                      |

| IBM AS/400        | 512 bytes                      |

| Intel Pentium     | 4K and 4M bytes                |

| ARM               | 4K and 64K bytes               |

| MIPS R4000        | 4k – 16M bytes in powers of 4  |

| DEC Alpha         | 8K - 4M bytes in powers of 8   |

| UltraSPARC        | 8K – 4M bytes in powers of 8   |

| PowerPC           | 4K bytes + "blocks"            |

| Intel IA-64       | 4K – 256M bytes in powers of 4 |

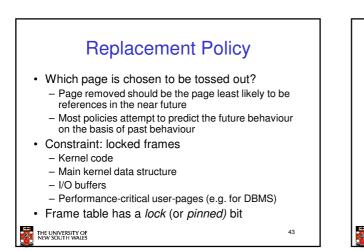

## *Optimal* Replacement policy

- Toss the page that won't be used for the longest time

- · Impossible to implement

- Only good as a theoretic reference point:

The closer a practical algorithm gets to *optimal*, the better

- Example:

- Reference string: 1, 2, 3, 4, 1, 2, 5, 1, 2, 3, 4, 5

- Four frames

- How many page faults?

THE UNIVERSITY OF NEW SOUTH WALES