### Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

**Developer's Manual**

March 2005

Document Number: 252480-005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

The Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Chips, Dialogic, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel Centrino logo, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, Sound Mark, The Computer Inside, The Journey Inside, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation. All Rights Reserved.

| 1 | Introc  | luction.                                         |           |                                                       | 27 |  |  |

|---|---------|--------------------------------------------------|-----------|-------------------------------------------------------|----|--|--|

|   | 1.1     | About 7<br>1.1.1                                 |           | nent<br>ead This Document                             |    |  |  |

|   | 1.2     |                                                  |           | ocuments                                              |    |  |  |

|   | 1.3     |                                                  |           | Conventions                                           |    |  |  |

|   | 1.0     | 1.3.1                                            |           | Representation                                        |    |  |  |

|   |         | 1.3.2                                            |           | s and Terminology                                     |    |  |  |

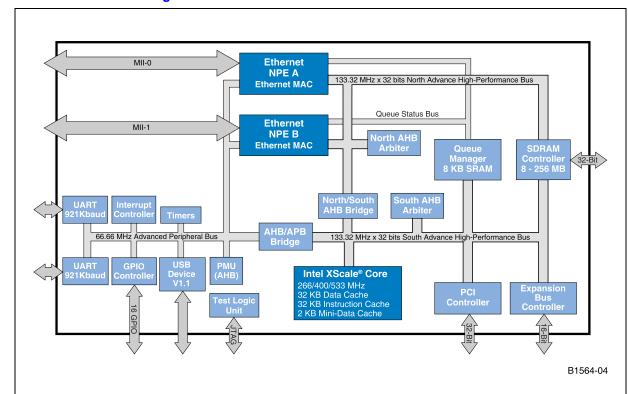

| 2 | Over    |                                                  | •         | .ine                                                  |    |  |  |

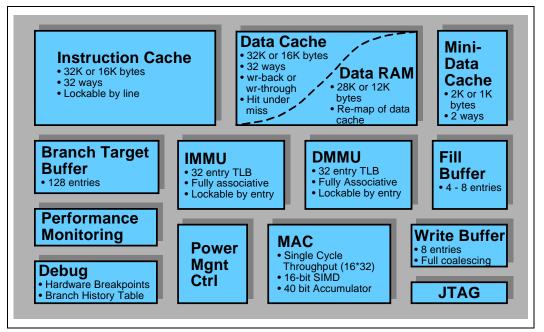

|   | 2.1     | Intel XScale <sup>®</sup> Microarchitecture Core |           |                                                       |    |  |  |

|   |         | 2.1.1                                            |           | ale <sup>®</sup> Core Overview                        |    |  |  |

|   |         |                                                  | 2.1.1.1   | ARM <sup>*</sup> Compatibility                        |    |  |  |

|   |         |                                                  | 2.1.1.2   | Multiply/Accumulate (MAC)                             |    |  |  |

|   |         |                                                  | 2.1.1.3   | Memory Management                                     |    |  |  |

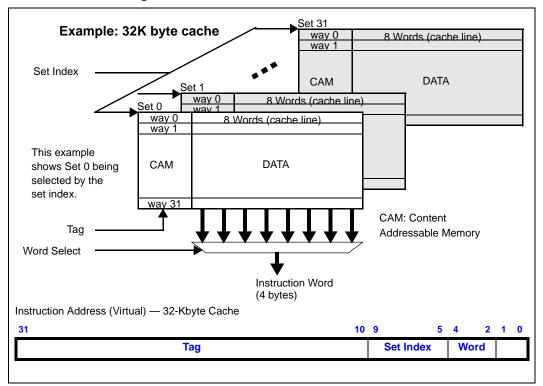

|   |         |                                                  | 2.1.1.4   | Instruction Cache                                     |    |  |  |

|   |         |                                                  | 2.1.1.5   | Branch Target Buffer                                  |    |  |  |

|   |         |                                                  | 2.1.1.6   | Data Cache                                            |    |  |  |

|   |         |                                                  | 2.1.1.7   | Intel XScale <sup>®</sup> Core Performance Monitoring |    |  |  |

|   | 2.2     |                                                  |           | or Engines (NPE)                                      |    |  |  |

|   | 2.3     |                                                  |           |                                                       |    |  |  |

|   | 2.4     |                                                  |           |                                                       |    |  |  |

|   | 2.5     |                                                  |           |                                                       |    |  |  |

|   | 2.6     |                                                  |           |                                                       |    |  |  |

|   | 2.7     |                                                  |           |                                                       |    |  |  |

|   | 2.8     |                                                  |           |                                                       |    |  |  |

|   | 2.9     |                                                  |           | er                                                    |    |  |  |

|   | 2.10    |                                                  |           |                                                       |    |  |  |

|   | 2.11    |                                                  |           | al Interfaces                                         |    |  |  |

|   | 2.12    | Universal Asynchronous Receiver Transceiver      |           |                                                       |    |  |  |

|   | 2.13    |                                                  |           |                                                       |    |  |  |

|   | 2.14    |                                                  |           | er                                                    |    |  |  |

|   | 2.15    |                                                  |           |                                                       |    |  |  |

|   | 2.16    | JIAG                                             |           |                                                       |    |  |  |

| 3 | Intel ) |                                                  |           |                                                       |    |  |  |

|   | 3.1     |                                                  |           | ment Unit                                             |    |  |  |

|   |         | 3.1.1                                            |           | Attributes                                            |    |  |  |

|   |         |                                                  |           | Page (P) Attribute Bit                                |    |  |  |

|   |         |                                                  | 3.1.1.2   | Cacheable (C), Bufferable (B), and eXtension (X) Bits |    |  |  |

|   |         | 3.1.2                                            |           | n of the MMU, Instruction Cache, and Data Cache       |    |  |  |

|   |         | 3.1.3                                            |           | ntrol                                                 |    |  |  |

|   |         |                                                  | 3.1.3.1   | Invalidate (Flush) Operation                          |    |  |  |

|   |         |                                                  | 3.1.3.2   | Enabling/Disabling                                    |    |  |  |

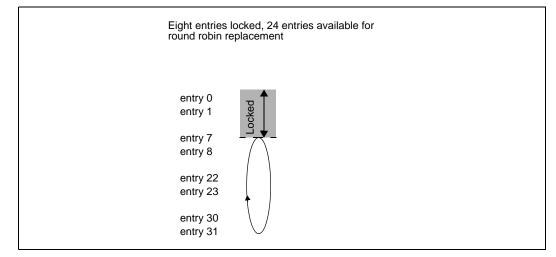

|   |         |                                                  | 3.1.3.3   | Locking Entries                                       |    |  |  |

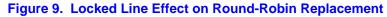

|   | 2.0     | Inctruct                                         | 3.1.3.4   | Round-Robin Replacement Algorithm                     |    |  |  |

|   | 3.2     |                                                  |           | When Instruction Cache is Enabled                     |    |  |  |

|   |         | 3.2.1                                            | Operation |                                                       |    |  |  |

|     |        | 3.2.1.1    |                                                     |    |

|-----|--------|------------|-----------------------------------------------------|----|

|     |        | 3.2.1.2    | Instruction-Cache Line-Replacement Algorithm        |    |

|     |        | 3.2.1.3    | Instruction-Cache Coherence                         |    |

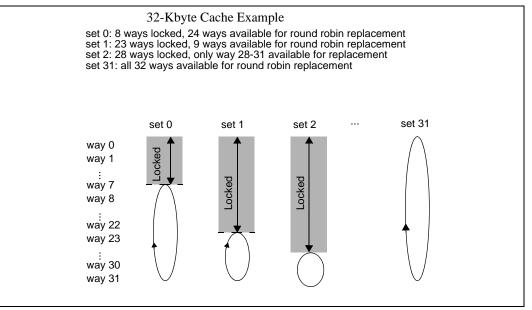

| 3.3 | Branch |            | uffer                                               |    |

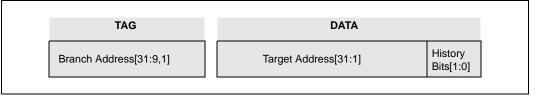

|     | 3.3.1  | Branch T   | Farget Buffer (BTB) Operation                       | 58 |

|     |        | 3.3.1.1    | Reset                                               | 59 |

| 3.4 | Data C | ache       |                                                     | 60 |

| -   | 3.4.1  |            | che Overview                                        |    |

|     | 3.4.2  |            | ility                                               |    |

|     | 3.4.3  |            | uring the Data Cache as Data RAM                    |    |

| 3.5 |        |            |                                                     |    |

| 3.5 | 0      |            | egisters                                            |    |

|     | 3.5.1  |            |                                                     |    |

|     |        | 3.5.1.1    |                                                     |    |

|     |        | 3.5.1.2    | Register 1: Control and Auxiliary Control Registers |    |

|     |        | 3.5.1.3    | Register 2: Translation Table Base Register         |    |

|     |        | 3.5.1.4    | Register 3: Domain Access Control Register          |    |

|     |        | 3.5.1.5    | Register 4: Reserved                                |    |

|     |        | 3.5.1.6    | Register 5: Fault Status Register                   |    |

|     |        | 3.5.1.7    | Register 6: Fault Address Register                  |    |

|     |        | 3.5.1.8    | Register 7: Cache Functions                         |    |

|     |        | 3.5.1.9    | Register 8: TLB Operations                          |    |

|     |        |            | Register 9: Cache Lock Down                         |    |

|     |        | 3.5.1.11   | 0                                                   |    |

|     |        |            | Register 11-12: Reserved                            |    |

|     |        | 3.5.1.13   |                                                     |    |

|     |        |            | The PID Register Affect On Addresses                |    |

|     |        |            | Register 14: Breakpoint Registers                   |    |

|     |        |            | Register 15: Coprocessor Access Register            |    |

|     | 3.5.2  |            | egisters                                            |    |

|     |        |            | Performance Monitoring Registers                    |    |

|     |        | 3.5.2.2    |                                                     | 85 |

|     |        | 3.5.2.3    | Software Debug Registers                            | 86 |

| 3.6 | Softwa | are Debug. |                                                     | 87 |

|     | 3.6.1  | Definitior | ٦S                                                  | 87 |

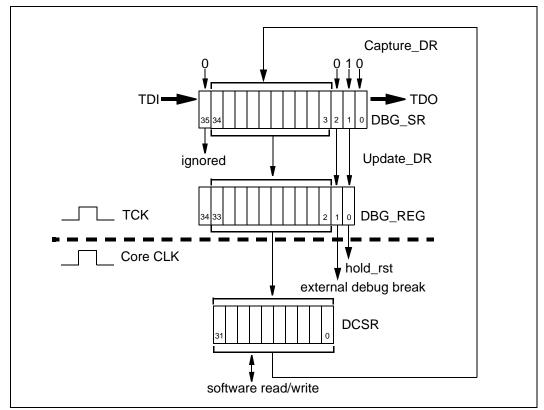

|     | 3.6.2  | Debug R    | egisters                                            | 87 |

|     | 3.6.3  |            | lodes                                               |    |

|     |        |            | Halt Mode                                           |    |

|     |        | 3.6.3.2    | Monitor Mode                                        |    |

|     | 3.6.4  |            | control and Status Register (DCSR)                  |    |

|     | 5.0.4  | 3.6.4.1    | Global Enable Bit (GE)                              |    |

|     |        | 3.6.4.2    | Halt Mode Bit (H)                                   |    |

|     |        | 3.6.4.3    | Vector Trap Bits (TF,TI,TD,TA,TS,TU,TR)             | 00 |

|     |        | 3.6.4.3    | Sticky Abort Bit (SA)                               |    |

|     |        | 3.6.4.5    | Method of Entry Bits (MOE)                          | 91 |

|     |        | 3.6.4.6    | Trace Buffer Mode Bit (M)                           |    |

|     |        | 3.6.4.0    | Trace Buffer Enable Bit (E)                         |    |

|     | 2 G F  |            |                                                     |    |

|     | 3.6.5  | •          | xceptions                                           |    |

|     |        | 3.6.5.1    | Halt Mode                                           |    |

|     |        | 3.6.5.2    | Monitor Mode                                        |    |

|     | 3.6.6  |            | akpoint Resources                                   |    |

|     |        | 3.6.6.1    | Instruction Breakpoints                             |    |

|     |        | 3.6.6.2    | Data Breakpoints                                    | 95 |

|     | 3.6.7                                  | Software Breakpoints9  |                                                                       |     |  |  |  |

|-----|----------------------------------------|------------------------|-----------------------------------------------------------------------|-----|--|--|--|

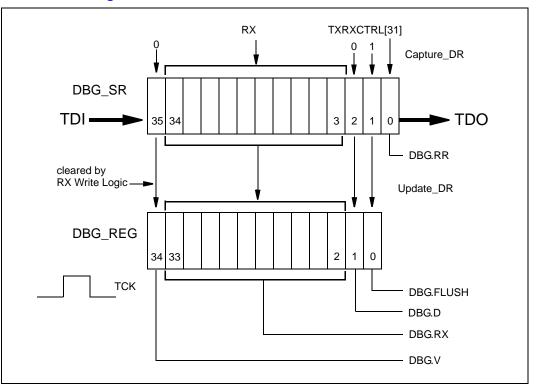

|     | 3.6.8                                  | Transmit               | Receive Control Register                                              | .97 |  |  |  |

|     |                                        | 3.6.8.1                | RX Register Ready Bit (RR)                                            |     |  |  |  |

|     |                                        | 3.6.8.2                | Overflow Flag (OV)                                                    |     |  |  |  |

|     |                                        | 3.6.8.3                | Download Flag (D)                                                     |     |  |  |  |

|     |                                        | 3.6.8.4                | TX Register Ready Bit (TR)                                            | 100 |  |  |  |

|     |                                        | 3.6.8.5                | Conditional Execution Using TXRXCTRL                                  |     |  |  |  |

|     | 3.6.9                                  |                        | Register                                                              |     |  |  |  |

|     | 3.6.10                                 |                        | Register                                                              |     |  |  |  |

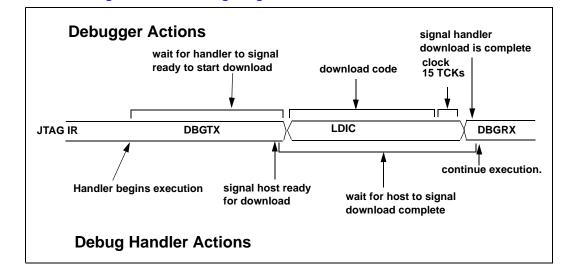

|     | 3.6.11                                 | 0                      | TAG Access                                                            |     |  |  |  |

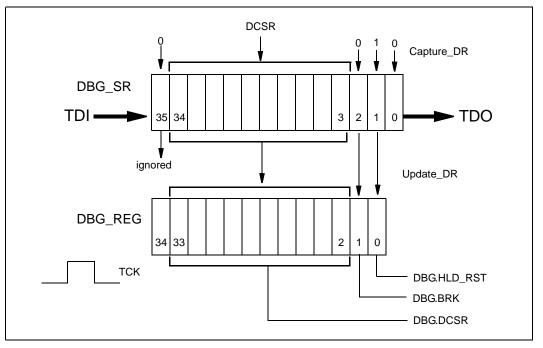

|     |                                        |                        | SELDCSR JTAG Command                                                  |     |  |  |  |

|     |                                        | 3.6.11.2               | SELDCSR JTAG Register                                                 | 103 |  |  |  |

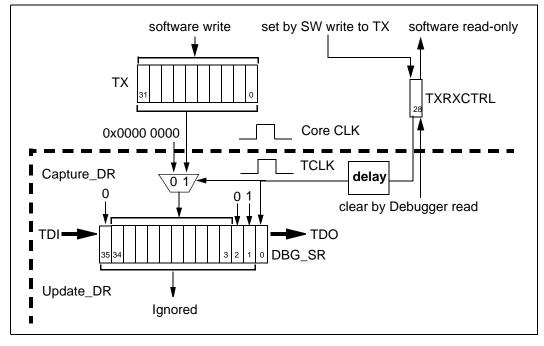

|     |                                        |                        | DBGTX JTAG Command                                                    |     |  |  |  |

|     |                                        |                        | DBGTX JTAG Register                                                   |     |  |  |  |

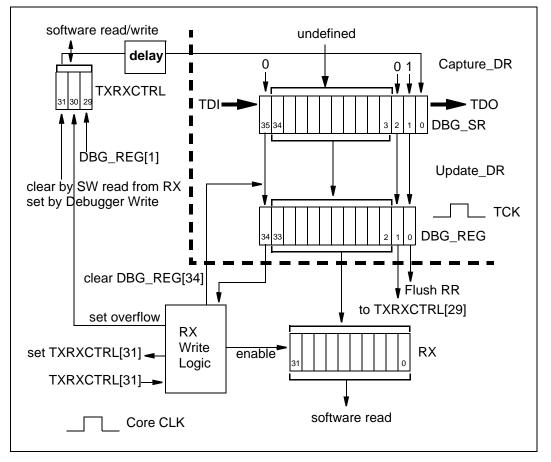

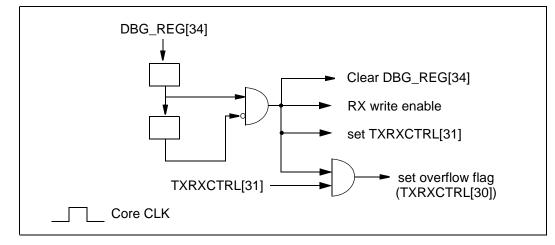

|     |                                        |                        | DBGRX JTAG Command                                                    |     |  |  |  |

|     |                                        | 3.6.11.6               | DBGRX JTAG Register                                                   | 106 |  |  |  |

|     | 0 0 4 0                                |                        | Debug JTAG Data Register Reset Values                                 |     |  |  |  |

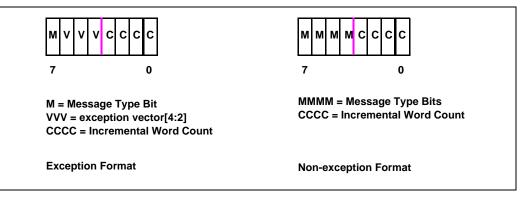

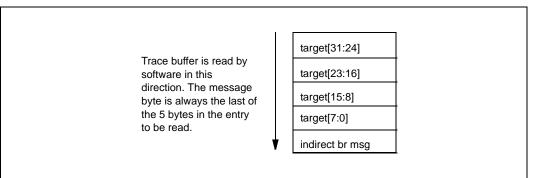

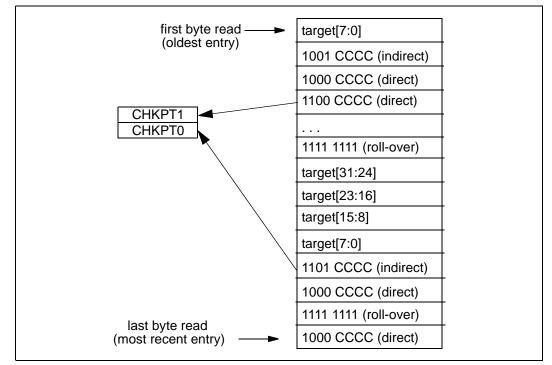

|     | 3.6.12                                 |                        | ffer                                                                  |     |  |  |  |

|     |                                        |                        | Trace Buffer CP Registers                                             |     |  |  |  |

|     | 3.6.13                                 |                        | ffer Entries                                                          |     |  |  |  |

|     |                                        |                        | Message Byte                                                          |     |  |  |  |

|     |                                        |                        | Trace Buffer Usage                                                    |     |  |  |  |

|     | 3.6.14                                 |                        | ding Code in ICache                                                   |     |  |  |  |

|     |                                        |                        | LDIC JTAG Command                                                     |     |  |  |  |

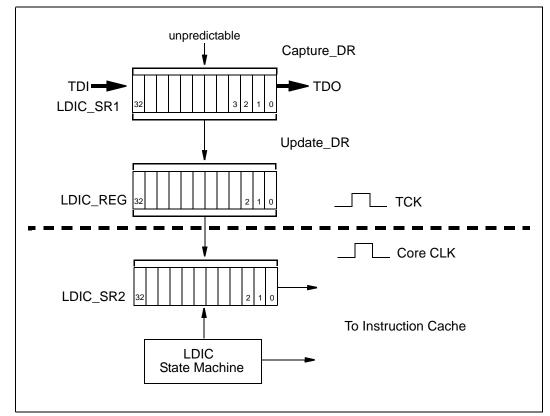

|     |                                        |                        | LDIC JTAG Data Register                                               |     |  |  |  |

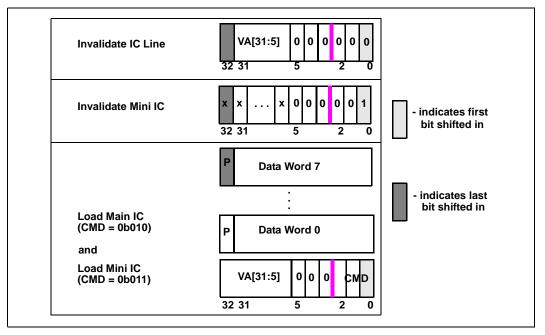

|     |                                        |                        | LDIC Cache Functions                                                  |     |  |  |  |

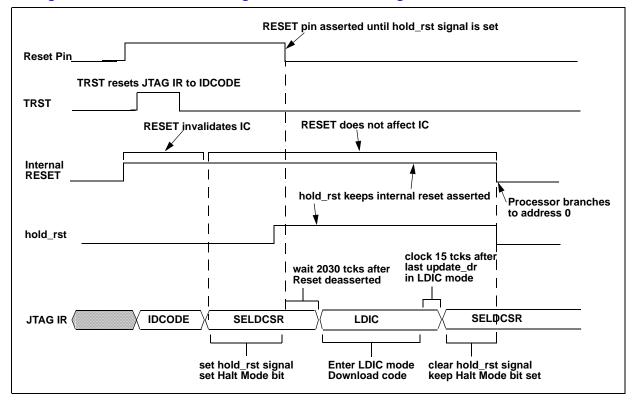

|     |                                        |                        | Loading IC During Reset.                                              |     |  |  |  |

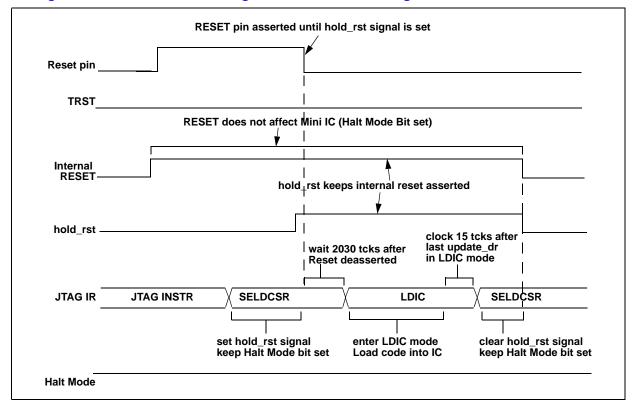

|     |                                        | 3.6.14.5               | Dynamically Loading IC After Reset<br>Mini-Instruction Cache Overview | 124 |  |  |  |

|     | 2615                                   |                        | e Software Protocol                                                   |     |  |  |  |

|     | 3.6.15                                 |                        |                                                                       |     |  |  |  |

|     |                                        |                        | Starting a Debug Session                                              |     |  |  |  |

|     |                                        |                        | Implementing a Debug Handler<br>Ending a Debug Session                |     |  |  |  |

|     | 2616                                   |                        |                                                                       |     |  |  |  |

| 3.7 | 3.6.16 Software Debug Notes and Errata |                        |                                                                       |     |  |  |  |

| 3.7 | 3.7.1                                  | Performance Monitoring |                                                                       |     |  |  |  |

|     | •                                      |                        | l                                                                     |     |  |  |  |

|     | 3.7.2                                  | -                      | Description                                                           |     |  |  |  |

|     |                                        | 3.7.2.1<br>3.7.2.2     | Clock Counter (CCNT)                                                  |     |  |  |  |

|     |                                        | 3.7.2.2                | Performance Count Registers<br>Performance Monitor Control Register   |     |  |  |  |

|     |                                        | 3.7.2.3                | Interrupt Enable Register                                             |     |  |  |  |

|     |                                        | 3.7.2.5                | Overflow Flag Status Register                                         |     |  |  |  |

|     |                                        | 3.7.2.6                | Event Select Register                                                 |     |  |  |  |

|     | 3.7.3                                  |                        | g the Performance Monitor                                             |     |  |  |  |

|     | 3.7.4                                  | • •                    | Ince Monitoring Events                                                |     |  |  |  |

|     | 0.7.4                                  | 3.7.4.1                | Instruction Cache Efficiency Mode                                     |     |  |  |  |

|     |                                        | 3.7.4.2                | Data Cache Efficiency Mode                                            |     |  |  |  |

|     |                                        | 3.7.4.3                | Instruction Fetch Latency Mode                                        |     |  |  |  |

|     |                                        | 3.7.4.4                | Data/Bus Request Buffer Full Mode                                     |     |  |  |  |

|     |                                        | 3.7.4.5                | Stall/Write-Back Statistics                                           |     |  |  |  |

|     |                                        | 3.7.4.6                | Instruction TLB Efficiency Mode                                       |     |  |  |  |

|     |                                        | 3.7.4.7                | Data TLB Efficiency Mode                                              |     |  |  |  |

|      | 3.7.5          | Multiple I          | Performance Monitoring Run Statistics         | 144 |  |  |

|------|----------------|---------------------|-----------------------------------------------|-----|--|--|

|      | 3.7.6 Examples |                     |                                               |     |  |  |

| 3.8  | Program        | mming Mo            | del                                           | 145 |  |  |

|      | 3.8.1          | ARM <sup>*</sup> Ar | chitecture Compatibility                      | 145 |  |  |

|      | 3.8.2          | ARM <sup>*</sup> Ar | chitecture Implementation Options             | 145 |  |  |

|      |                | 3.8.2.1             | Big Endian versus Little Endian               |     |  |  |

|      |                | 3.8.2.2             | 26-Bit Architecture                           |     |  |  |

|      |                | 3.8.2.3             | Thumb                                         | 145 |  |  |

|      |                | 3.8.2.4             | ARM <sup>*</sup> DSP-Enhanced Instruction Set | 146 |  |  |

|      |                | 3.8.2.5             | Base Register Update                          | 146 |  |  |

|      | 3.8.3          | Extensio            | ns to ARM <sup>*</sup> Architecture           | 147 |  |  |

|      |                | 3.8.3.1             | DSP Coprocessor 0 (CP0)                       | 147 |  |  |

|      |                | 3.8.3.2             | New Page Attributes                           | 153 |  |  |

|      |                | 3.8.3.3             | Additions to CP15 Functionality               |     |  |  |

|      |                | 3.8.3.4             | Event Architecture                            |     |  |  |

| 3.9  | Perforn        | nance Cor           | nsiderations                                  | 159 |  |  |

|      | 3.9.1          |                     | Latency                                       |     |  |  |

|      | 3.9.2          | Branch F            | Prediction                                    | 160 |  |  |

|      | 3.9.3          | Addressi            | ng Modes                                      | 160 |  |  |

|      | 3.9.4          | Instructio          | n Latencies                                   | 161 |  |  |

|      |                | 3.9.4.1             | Performance Terms                             |     |  |  |

|      |                | 3.9.4.2             | Branch Instruction Timings                    |     |  |  |

|      |                | 3.9.4.3             | Data Processing Instruction Timings           |     |  |  |

|      |                | 3.9.4.4             | Multiply Instruction Timings                  |     |  |  |

|      |                | 3.9.4.5             | Saturated Arithmetic Instructions             |     |  |  |

|      |                | 3.9.4.6             | Status Register Access Instructions           |     |  |  |

|      |                | 3.9.4.7             | Load/Store Instructions                       |     |  |  |

|      |                | 3.9.4.8             | Semaphore Instructions                        |     |  |  |

|      |                | 3.9.4.9             | Coprocessor Instructions                      |     |  |  |

|      |                |                     | Miscellaneous Instruction Timing              |     |  |  |

| 3.10 | Ontimiz        |                     | de                                            |     |  |  |

| 5.10 | •              |                     | ion                                           |     |  |  |

|      | 5.10.1         |                     | About This Section                            |     |  |  |

|      | 2 10 2         |                     |                                               |     |  |  |

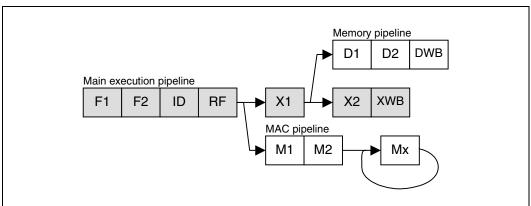

|      | 3.10.2         |                     | ors' Pipeline                                 |     |  |  |

|      |                |                     | General Pipeline Characteristics              |     |  |  |

|      |                |                     | Main Execution Pipeline                       |     |  |  |

|      |                |                     |                                               |     |  |  |

|      |                | 3 10 2 5            | Memory Pipeline                               | 173 |  |  |

|      | 3.10.3         |                     | timizations                                   |     |  |  |

|      | 0.10.0         |                     | Conditional Instructions                      |     |  |  |

|      |                |                     | Bit Field Manipulation                        |     |  |  |

|      |                |                     | Optimizing the Use of Immediate Values        |     |  |  |

|      |                |                     | Optimizing Integer Multiply and Divide        |     |  |  |

|      |                |                     | Effective Use of Addressing Modes             |     |  |  |

|      | 3.10.4         |                     | nd Prefetch Optimizations                     |     |  |  |

|      |                |                     | Instruction Cache                             |     |  |  |

|      |                |                     | Data and Mini Cache                           |     |  |  |

|      |                |                     | Cache Considerations                          |     |  |  |

|      |                |                     | Prefetch Considerations                       |     |  |  |

|      | 3.10.5         | Instructio          | n Scheduling                                  | 192 |  |  |

|   |            |                | <ul> <li>3.10.5.1 Scheduling Loads</li> <li>3.10.5.2 Scheduling Data Processing Instructions</li> <li>3.10.5.3 Scheduling Multiply Instructions</li> <li>3.10.5.4 Scheduling SWP and SWPB Instructions (MRRC/MCRR)</li> <li>3.10.5.5 Scheduling the MRA and MAR Instructions (MRRC/MCRR)</li> <li>3.10.5.6 Scheduling the MIA and MIAPH Instructions</li> <li>3.10.5.7 Scheduling MRS and MSR Instructions</li> <li>3.10.5.8 Scheduling CP15 Coprocessor Instructions</li> <li>Optimizations for Size</li> <li>2.40.74 Space/Bactemenes Trade Off</li> </ul> | 196<br>197<br>197<br>198<br>199<br>199<br>200<br>200<br>200 |

|---|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 4 | Netw       | ork Proc       | 3.10.7.1 Space/Performance Trade Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

| 5 |            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 5 |            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

|   | 5.1        |                | Bus Arbiters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |

|   | <b>F</b> 0 | 5.1.1<br>Maman | Priority Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

|   | 5.2        | wemory         | у Мар                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 206                                                         |

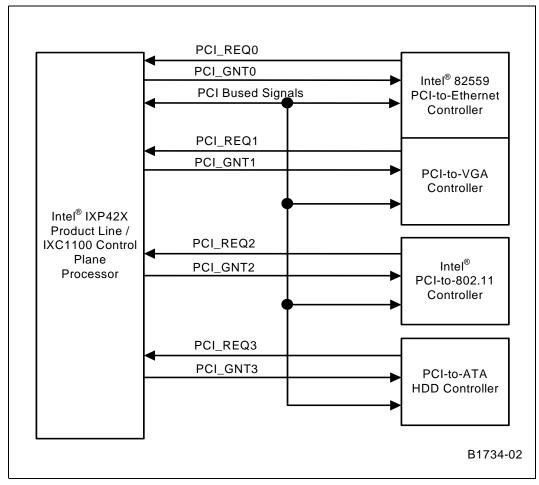

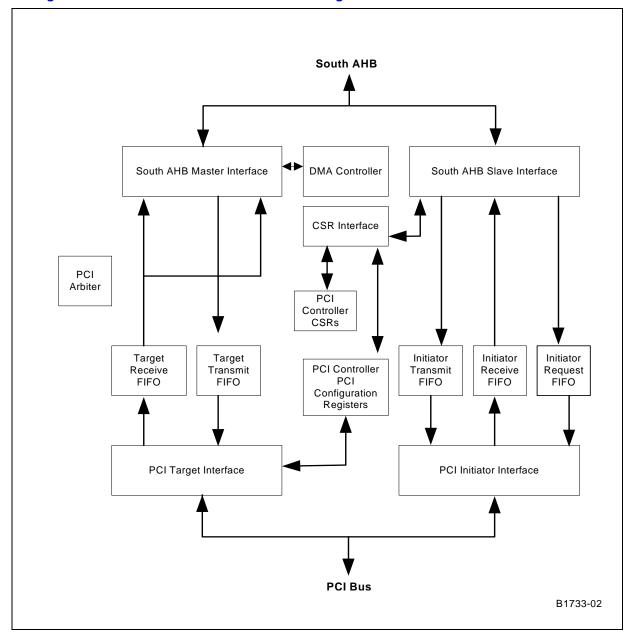

| 6 | PCI C      | controlle      | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 209                                                         |

|   | 6.1        | PCI Co         | ntroller Configured as Host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 214                                                         |

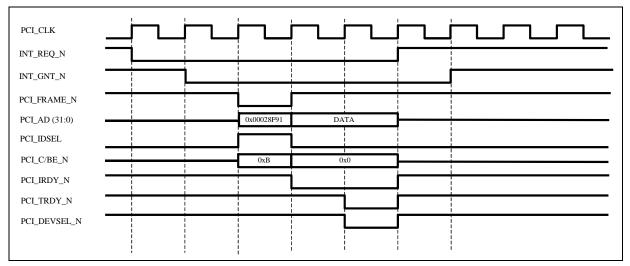

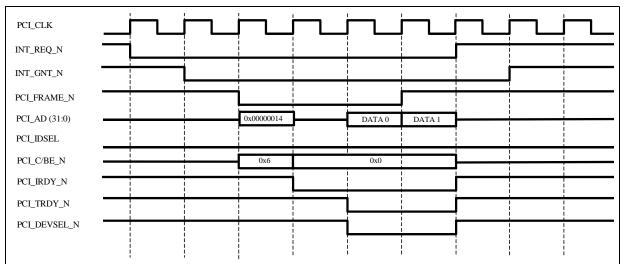

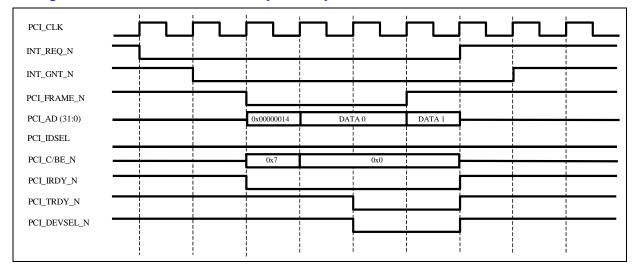

|   | 0.1        | 6.1.1          | Example: Generating a PCI Configuration Write and Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

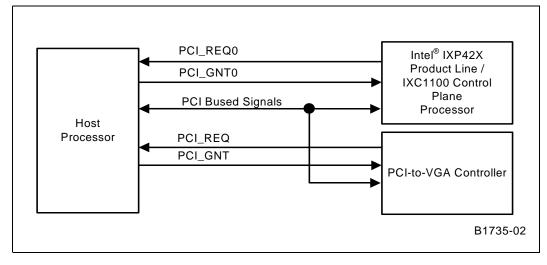

|   | 6.2        | -              | ntroller Configured as Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |

|   | 6.3        |                | ng PCI Controller Configuration and Status Registers for Data Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

|   |            | 6.3.1          | Example: AHB Memory Base Address Register, AHB I/O<br>Base Address Register, and PCI Memory Base Address<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

|   |            | 6.3.2          | Example: PCI Memory Base Address Register and South-AHB Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |

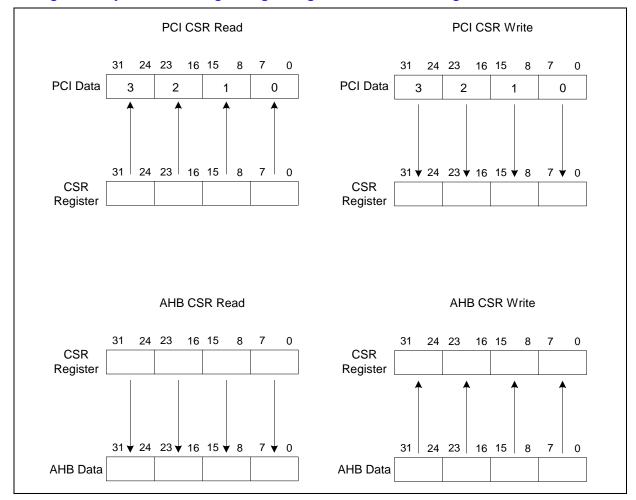

|   | 6.4        |                | ng the PCI Controller Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |

|   | 6.5        |                | ntroller South AHB Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

|   | 6.6        |                | ntroller Functioning as Bus Initiator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

|   |            | 6.6.1          | PCI Byte Enables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |

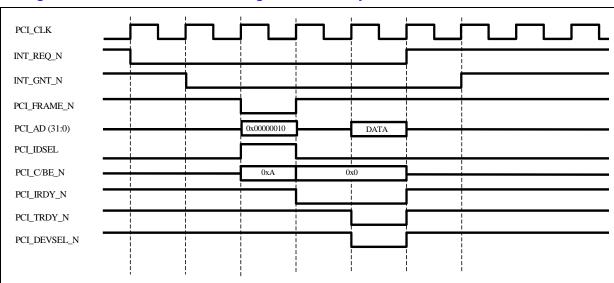

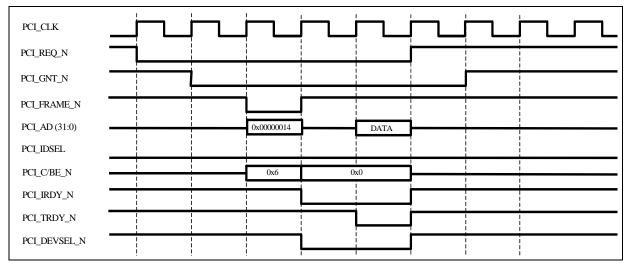

|   |            | 6.6.2          | Initiated Type-0 Read Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

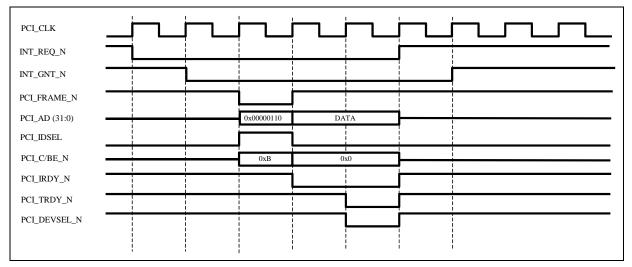

|   |            | 6.6.3          | Initiated Type-0 Write Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

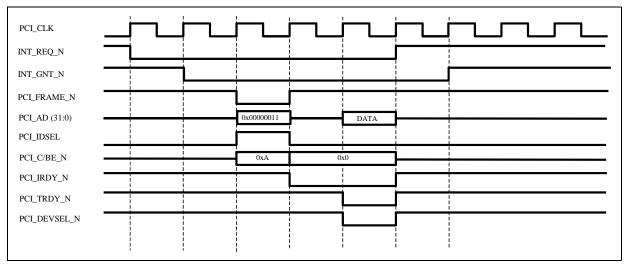

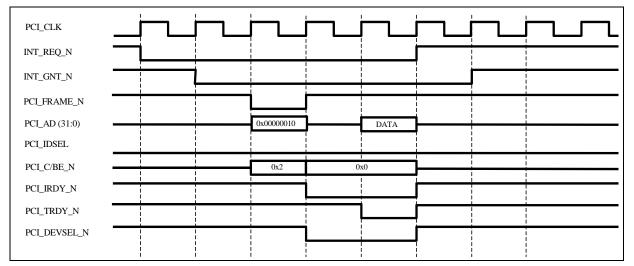

|   |            | 6.6.4          | Initiated Type-1 Read Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

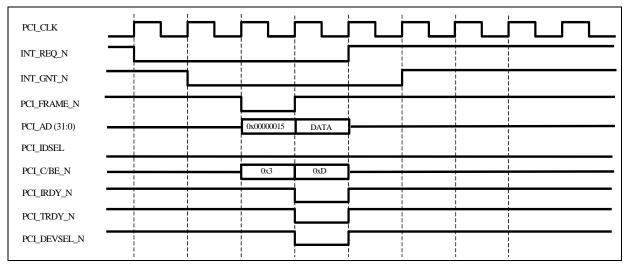

|   |            | 6.6.5          | Initiated Type-1 Write Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

|   |            | 6.6.6          | Initiated Memory Read Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

|   |            | 6.6.7          | Initiated Memory Write Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

|   |            | 6.6.8          | Initiated I/O Read Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |

|   |            | 6.6.9          | Initiated I/O Write Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

|   |            | 6.6.10         | Initiated Burst Memory Read Transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

|   | 07         | 6.6.11         | Initiated Burst Memory Write Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

|   | 6.7        |                | ntroller Functioning as Bus Target<br>ntroller DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |

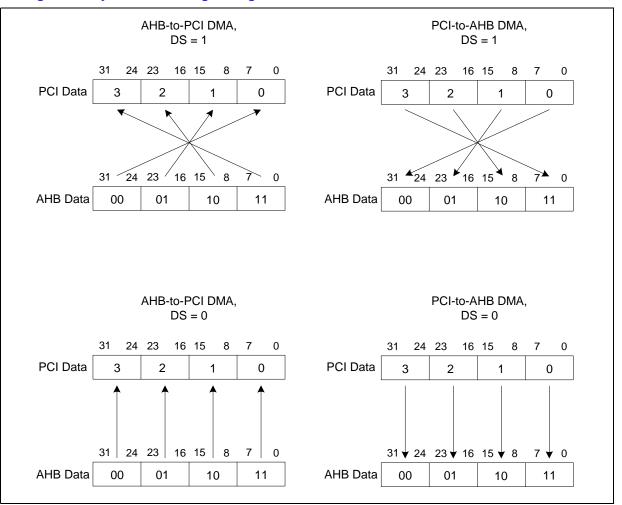

|   | 6.8        | 6.8.1          | AHB to PCI DMA Channel Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |

|   |            | 6.8.2          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

|   | 6.9        |                | PCI to AHB DMA Channel Operation<br>ntroller Door Bell Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

|   | 6.10       |                | ntroller Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |

|   | 0.10       |                | PCI Interrupt Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

|   |            |                | Internal Interrupt Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |

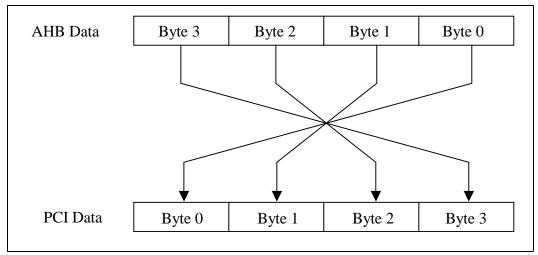

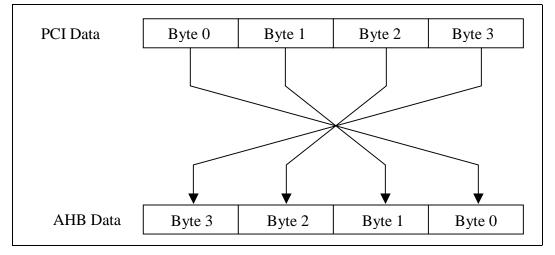

|   | 6.11       |                | ntroller Endian Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |

|   |            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 6.12 | PCI Controller Clock and Reset Generation                              | 250 |

|------|------------------------------------------------------------------------|-----|

| 6.13 | PCI RCOMP Circuitry                                                    | 251 |

| 6.14 | Register Descriptions                                                  | 251 |

|      | 6.14.1 PCI Configuration Registers                                     |     |

|      | 6.14.1.1 Device ID/Vendor ID Register                                  |     |

|      | 6.14.1.2 Status Register/Control Register                              | 253 |

|      | 6.14.1.3 Class Code/Revision ID Register                               |     |

|      | 6.14.1.4 BIST/Header Type/Latency Timer/Cache Line Register            |     |

|      | 6.14.1.5 Base Address 0 Register                                       |     |

|      |                                                                        |     |

|      | 6.14.1.6 Base Address 1 Register                                       |     |

|      | 6.14.1.7 Base Address 2 Register                                       |     |

|      | 6.14.1.8 Base Address 3 Register                                       |     |

|      | 6.14.1.9 Base Address 4 Register                                       |     |

|      | 6.14.1.10 Base Address 5 Register                                      |     |

|      | 6.14.1.11 Subsystem ID/Subsystem Vendor ID Register                    |     |

|      | 6.14.1.12 Max_Lat, Min_Gnt, Interrupt Pin, and Interrupt Line Register |     |

|      | 6.14.1.13 Retry Timeout/TRDY Timeout Register                          |     |

|      | 6.14.2 PCI Controller Configuration and Status Registers               |     |

|      | 6.14.2.1 PCI Controller Non-pre-fetch Address Register                 |     |

|      | 6.14.2.2 PCI Controller Non-pre-fetch Command/Byte Enables Register    | 262 |

|      | 6.14.2.3 PCI Controller Non-Pre-fetch Write Data Register              | 263 |

|      | 6.14.2.4 PCI Controller Non-Pre-fetch Read Data Register               |     |

|      | 6.14.2.5 PCI Controller Configuration Port Address/Command/            |     |

|      | Byte Enables Register                                                  | 264 |

|      | 6.14.2.6 PCI Controller Configuration Port Write Data Register         | 265 |

|      | 6.14.2.7 PCI Controller Configuration Port Read Data Register          |     |

|      | 6.14.2.8 PCI Controller Control and Status Register                    |     |

|      | 6.14.2.9 PCI Controller Interrupt Status Register                      |     |

|      | 6.14.2.10 PCI Controller Interrupt Enable Register                     | 268 |

|      | 6.14.2.11 DMA Control Register                                         |     |

|      | 6.14.2.12 AHB Memory Base Address Register                             |     |

|      | 6.14.2.13 AHB I/O Base Address Register                                |     |

|      | 6.14.2.14 PCI Memory Base Address Register                             |     |

|      | 6.14.2.15 AHB Doorbell Register                                        |     |

|      |                                                                        |     |

|      | 6.14.2.16 PCI Doorbell Register                                        |     |

|      | 6.14.2.17 AHB to PCI DMA AHB Address Register 0                        | 272 |

|      | 6.14.2.18 AHB to PCI DMA PCI Address Register 0                        |     |

|      | 6.14.2.19 AHB to PCI DMA Length Register 0                             |     |

|      | 6.14.2.20 AHB to PCI DMA AHB Address Register 1                        |     |

|      | 6.14.2.21 AHB to PCI DMA PCI Address Register 1                        | 274 |

|      | 6.14.2.22 AHB to PCI DMA Length Register 1                             |     |

|      | 6.14.2.23 PCI to AHB DMA AHB Address Register 0                        |     |

|      | 6.14.2.24 PCI to AHB DMA PCI Address Register 0                        |     |

|      | 6.14.2.25 PCI to AHB DMA Length Register 0                             |     |

|      | 6.14.2.26 PCI to AHB DMA AHB Address Register 1                        | 277 |

|      | 6.14.2.27 PCI to AHB DMA PCI Address Register 1                        |     |

|      | 6.14.2.28 PCI to AHB DMA Length Register 1                             | 278 |

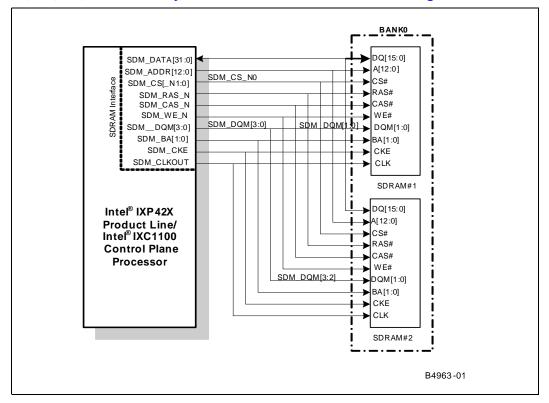

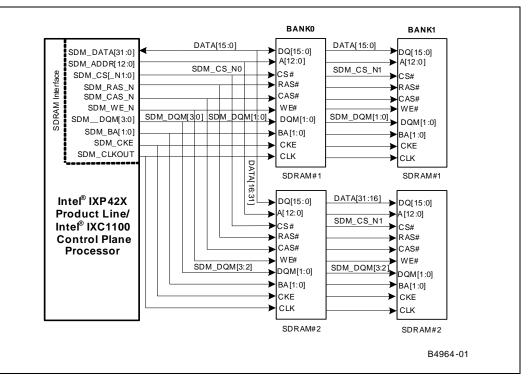

| SDR/ | AM Controller                                                          | 279 |

| 7.1  | SDRAM Memory Space                                                     | 282 |

|      |                                                                        |     |

| 7.2  | Initializing the SDRAM Controller                                      |     |

| _    | 7.2.1 Initializing the SDRAM                                           |     |

| 7.3  | SDRAM Memory Accesses                                                  |     |

|      | 7.3.1 Read Transfer                                                    | 288 |

7

|    |       | 7.3.2          | 7.3.1.1       Read Cycle Timing (CAS Latency of Two Cycles)         7.3.1.2       Read Burst Transfer (Interleaved AHB Reads)         Write Transfer       Transfer | 289<br>290 |

|----|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    | 7.4   | Pogiate        | 7.3.2.1 Write Transfer<br>er Description                                                                                                                            |            |

|    | 7.4   | 7.4.1          | Configuration Register                                                                                                                                              |            |

|    |       | 7.4.2          | Refresh Register                                                                                                                                                    |            |

|    |       | 7.4.3          | Instruction Register                                                                                                                                                |            |

| 8  | Expa  |                | us Controller                                                                                                                                                       |            |

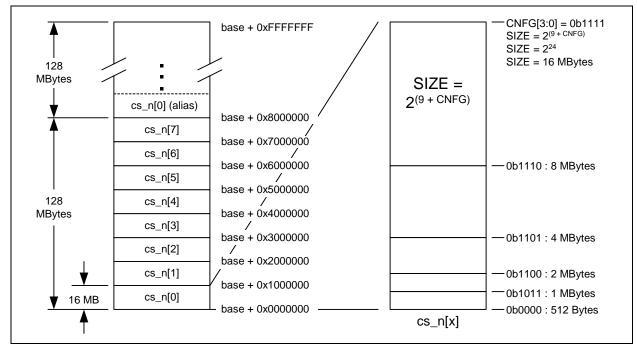

|    | 8.1   | Expans         | sion Bus Address Space                                                                                                                                              |            |

|    | 8.2   |                | elect Address Allocation                                                                                                                                            |            |

|    | 8.3   | Addres         | ss and Data Byte Steering                                                                                                                                           |            |

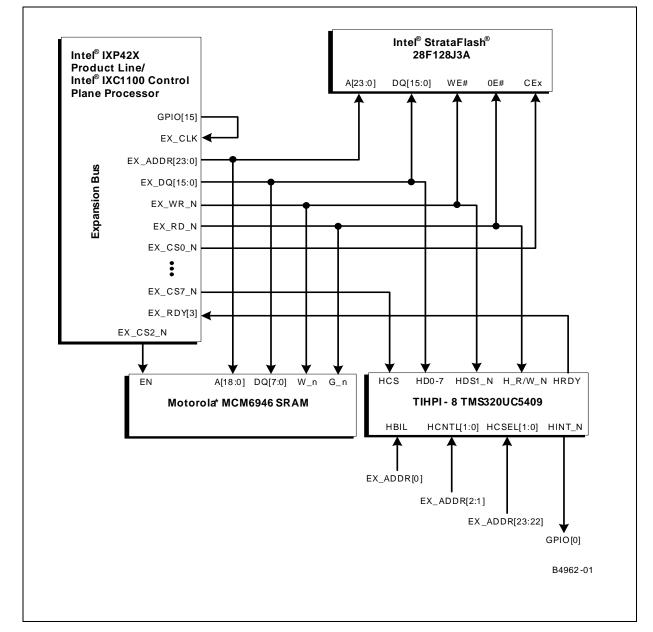

|    | 8.4   | Expans         | sion Bus Connections                                                                                                                                                |            |

|    | 8.5   |                | sion Bus Interface Configuration                                                                                                                                    |            |

|    | 8.6   |                | I/O Wait                                                                                                                                                            |            |

|    | 8.7   |                | I Design Knowledge for Using HPI mode                                                                                                                               |            |

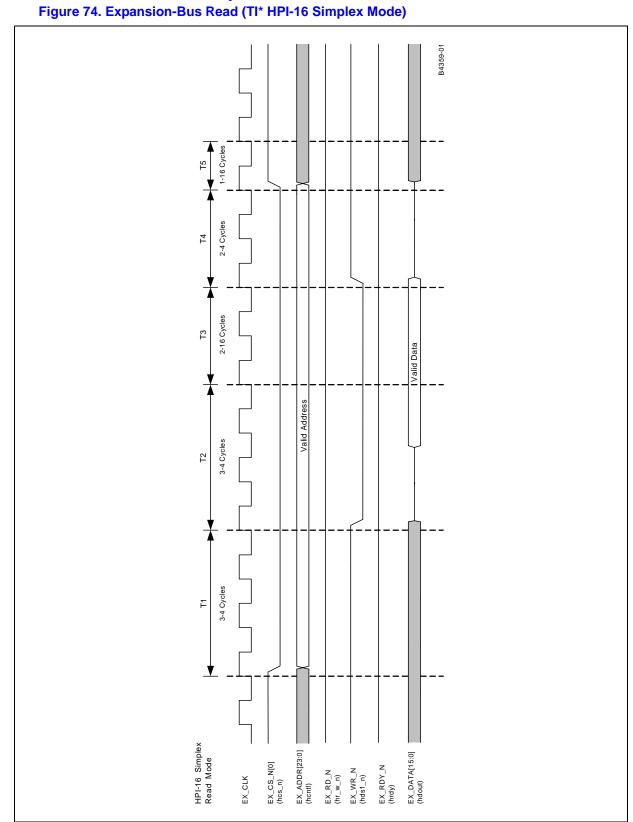

|    | 8.8   |                | sion Bus Interface Access Timing Diagrams                                                                                                                           |            |

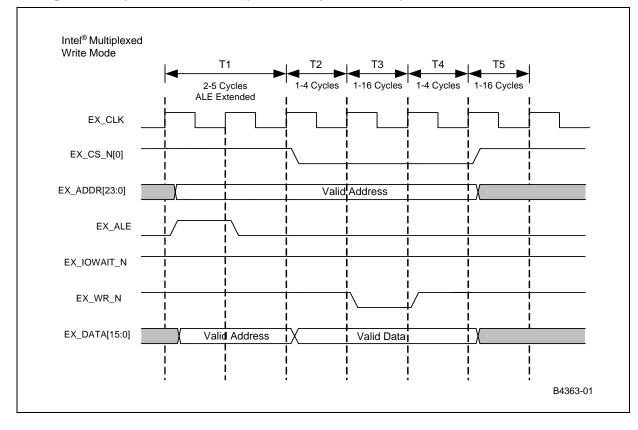

|    |       | 8.8.1          | Intel <sup>®</sup> Multiplexed-Mode Write Access                                                                                                                    |            |

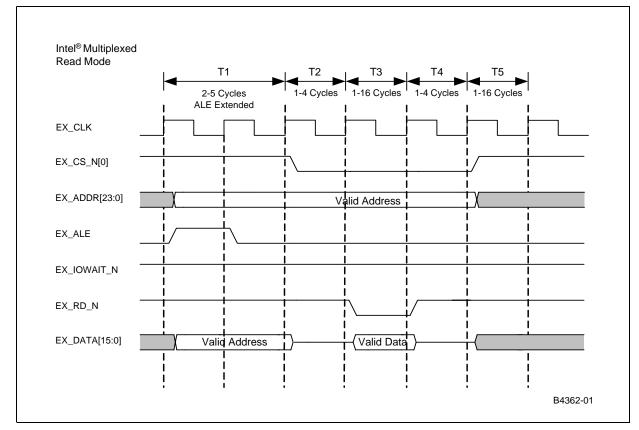

|    |       | 8.8.2          | Intel <sup>®</sup> Multiplexed-Mode Read Access                                                                                                                     |            |

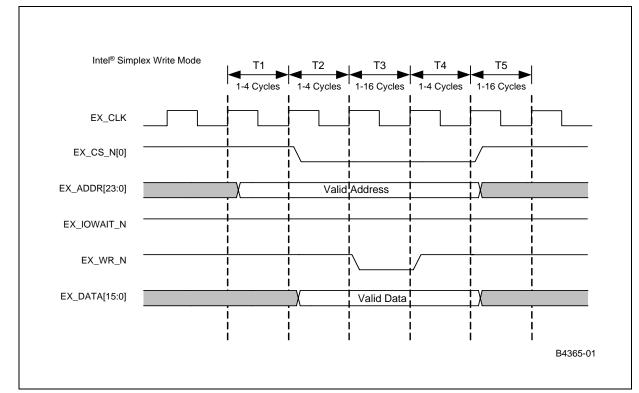

|    |       | 8.8.3          | Intel <sup>®</sup> Simplex-Mode Write Access                                                                                                                        |            |

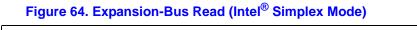

|    |       | 8.8.4          | Intel <sup>®</sup> Simplex-Mode Read Access                                                                                                                         |            |

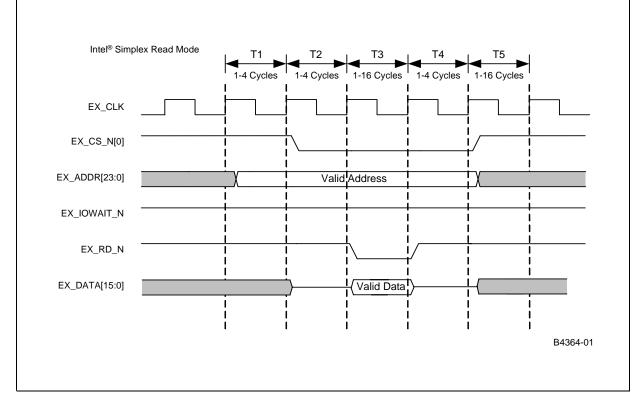

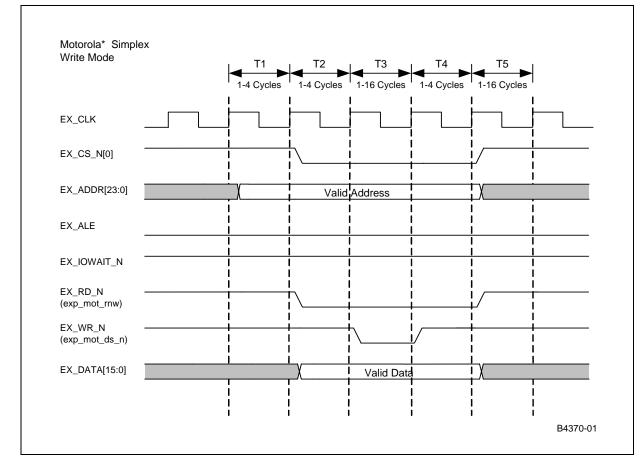

|    |       | 8.8.5          | Motorola* Multiplexed-Mode Write Access                                                                                                                             |            |

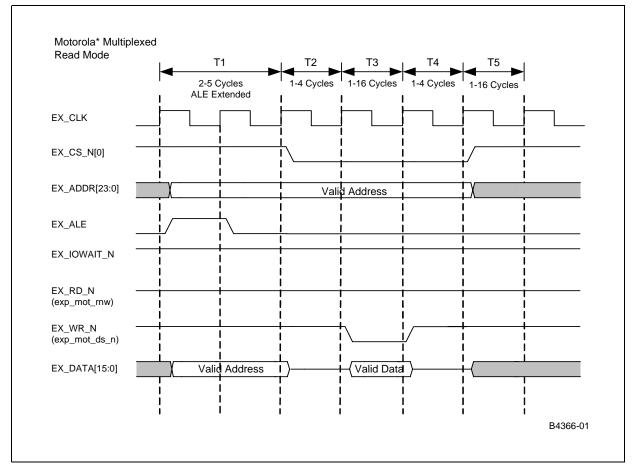

|    |       | 8.8.6<br>8.8.7 | Motorola* Multiplexed-Mode Read Access                                                                                                                              |            |

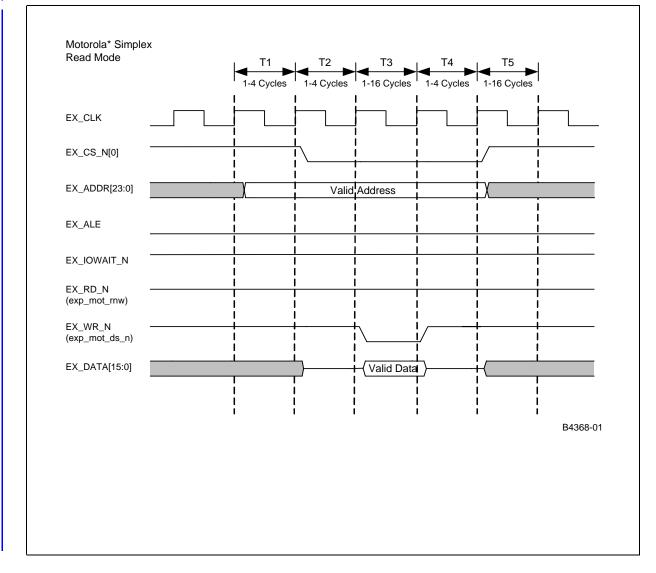

|    |       | 8.8.8          | Motorola* Simplex-Mode Write Access<br>Motorola* Simplex-Mode Read Access                                                                                           |            |

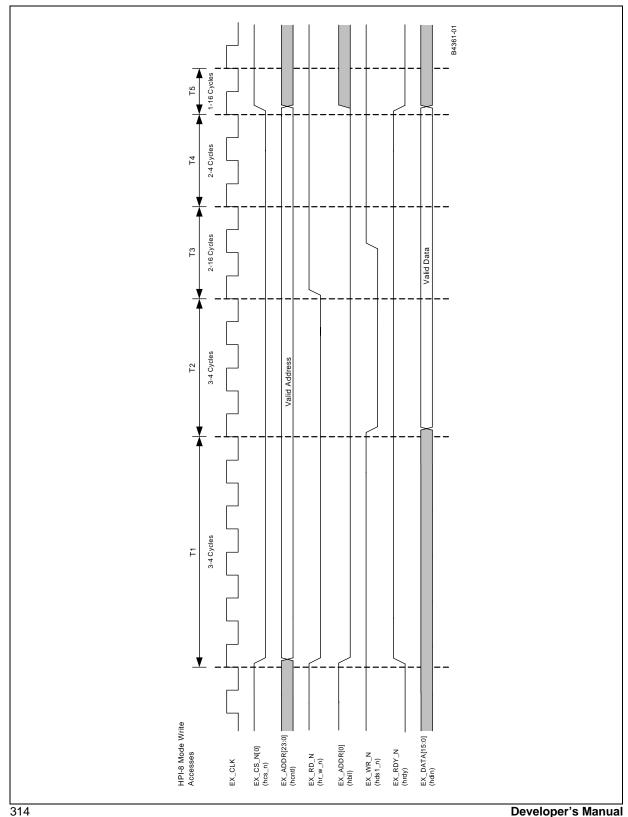

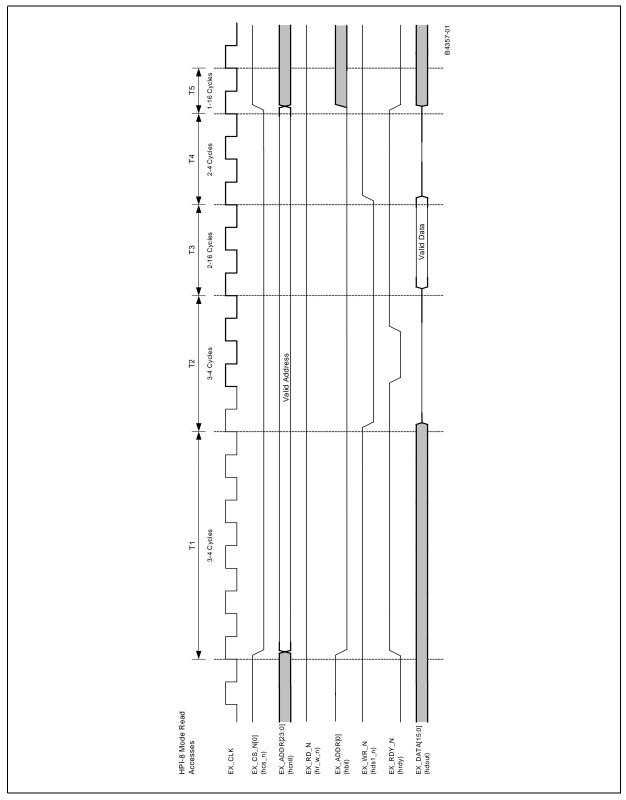

|    |       | 8.8.9          | TI* HPI-8 Write Access                                                                                                                                              |            |

|    |       | 8.8.10         | TI* HPI-8 Read Access                                                                                                                                               |            |

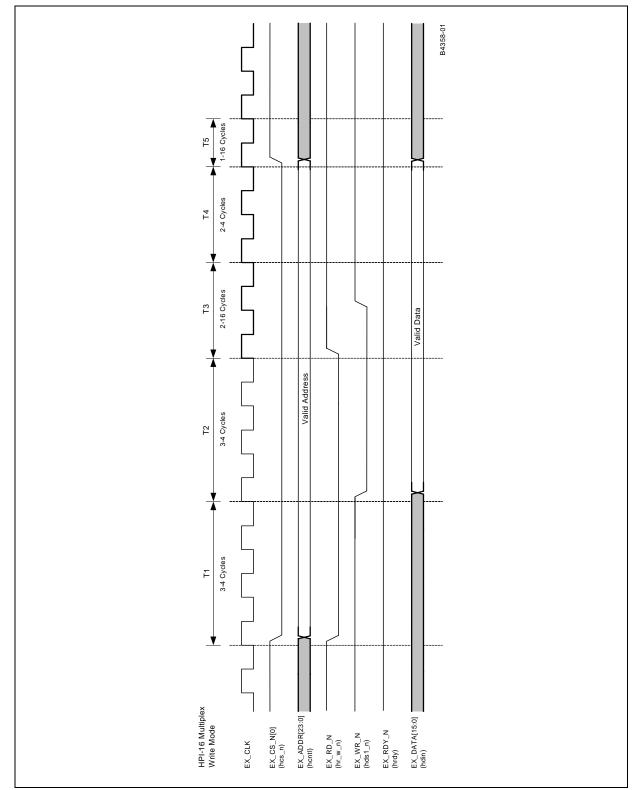

|    |       | 8.8.11         | TI* HPI-16, Multiplexed-Mode Write Access                                                                                                                           |            |

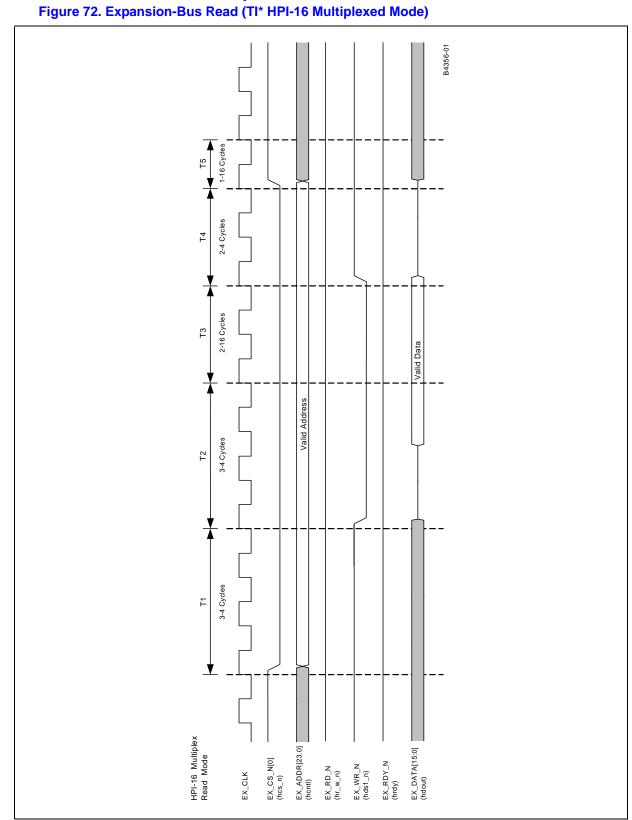

|    |       |                | TI* HPI-16, Multiplexed-Mode Read Access                                                                                                                            |            |

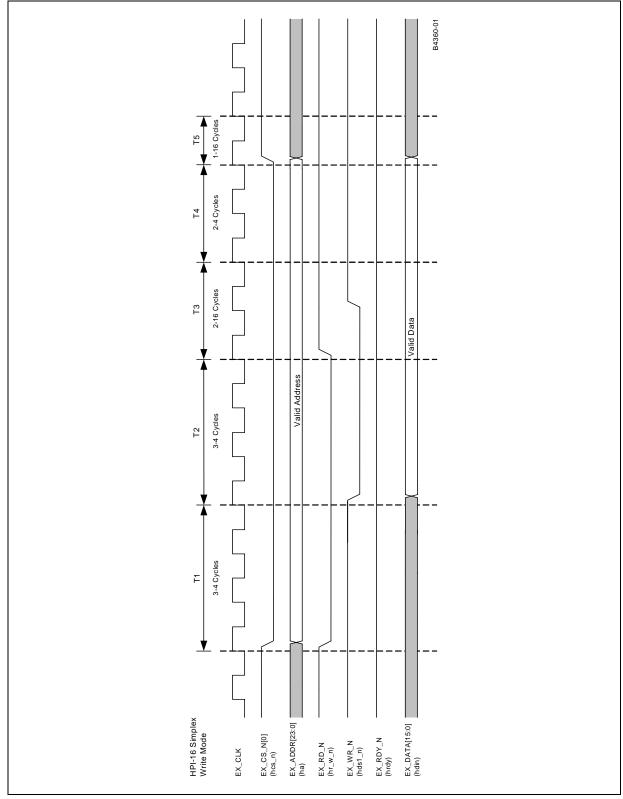

|    |       | 8.8.13         | TI* HPI-16 Simplex-Mode Write Access                                                                                                                                |            |

|    |       | 8.8.14         | •                                                                                                                                                                   |            |

|    | 8.9   |                | er Descriptions                                                                                                                                                     |            |

|    |       | 8.9.1          | Timing and Control Registers for Chip Select 0                                                                                                                      |            |

|    |       | 8.9.2          | Timing and Control Registers for Chip Select 1                                                                                                                      |            |

|    |       | 8.9.3          | Timing and Control Registers for Chip Select 2                                                                                                                      |            |

|    |       | 8.9.4          | Timing and Control Registers for Chip Select 3                                                                                                                      |            |

|    |       | 8.9.5          | Timing and Control Registers for Chip Select 4                                                                                                                      |            |

|    |       | 8.9.6          | Timing and Control Registers for Chip Select 5                                                                                                                      |            |

|    |       | 8.9.7          | Timing and Control Registers for Chip Select 6                                                                                                                      |            |

|    |       | 8.9.8          | Timing and Control Registers for Chip Select 7                                                                                                                      |            |

|    |       | 8.9.9          | Configuration Register 0                                                                                                                                            |            |

|    |       |                | 8.9.9.1 User-Configurable Field                                                                                                                                     |            |

|    |       |                | Configuration Register 1                                                                                                                                            |            |

|    | 8.10  | Expans         | sion Bus Controller Performance                                                                                                                                     |            |

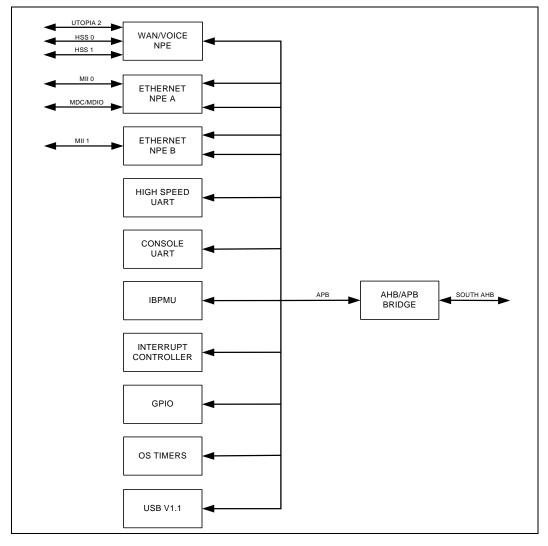

| 9  | AHB/  | APB Bri        | idge                                                                                                                                                                |            |

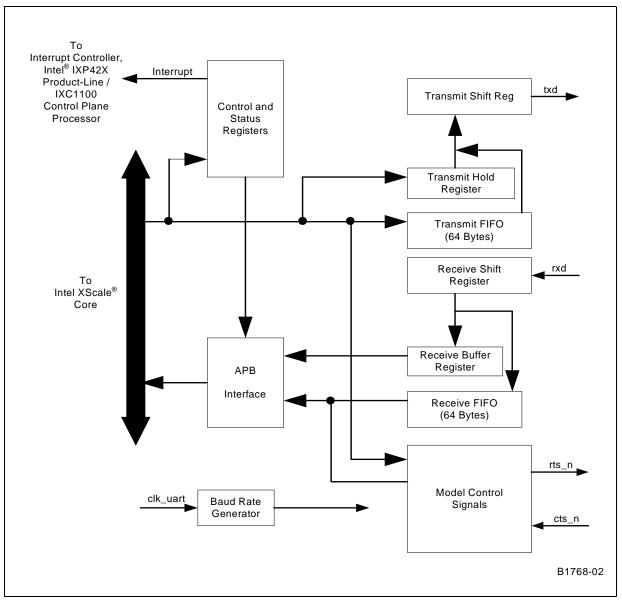

| 10 | Unive | ersal As       | ynchronous Receiver Transceiver (UART)                                                                                                                              | 331        |

|    | 10.1  | High S         | peed UART                                                                                                                                                           |            |

|    | 10.2  |                | uring the UART                                                                                                                                                      |            |

|    |        | 10.2.1 Setting the Baud Rate                                           | 334 |

|----|--------|------------------------------------------------------------------------|-----|

|    |        | 10.2.2 Setting Data Bits/Stop Bits/Parity                              |     |

|    |        | 10.2.3 Using the Modem Control Signals                                 | 337 |

|    |        | 10.2.4 UART Interrupts                                                 | 338 |

|    | 10.3   | Transmitting and Receiving UART Data                                   |     |

|    | 10.4   | Register Descriptions                                                  |     |

|    |        | 10.4.1 Receive Buffer Register                                         |     |

|    |        | 10.4.2 Transmit Holding Register                                       |     |

|    |        | 10.4.3 Divisor Latch Low Register                                      |     |

|    |        | 10.4.4 Divisor Latch High Register                                     |     |

|    |        | 10.4.5 Interrupt Enable Register                                       |     |

|    |        | 10.4.6 Interrupt Identification Register                               |     |

|    |        | 10.4.7 FIFO Control Register                                           |     |

|    |        | 10.4.8 Line Control Register                                           |     |

|    |        | 10.4.9 Modem Control Register                                          |     |

|    |        | 10.4.10 Line Status Register                                           |     |

|    |        | 10.4.11 Modem Status Register                                          |     |

|    |        | 10.4.12 Scratch-Pad Register                                           |     |

|    |        | 10.4.12 Octation and Register                                          |     |

|    | 10.5   | Console UART                                                           |     |

|    | 10.5   | 10.5.1 Register Description                                            |     |

|    |        | 6 1                                                                    |     |

|    |        | 10.5.1.1 Receive Buffer Register<br>10.5.1.2 Transmit Holding Register |     |

|    |        | 10.5.1.3 Divisor Latch Low Register                                    |     |

|    |        | 10.5.1.4 Divisor Latch High Register                                   |     |

|    |        | 10.5.1.5 Interrupt Enable Register                                     |     |

|    |        | 10.5.1.6 Interrupt Identification Register                             |     |

|    |        | 10.5.1.7 FIFO Control Register                                         |     |

|    |        | 10.5.1.8 Line Control Register                                         |     |

|    |        | 10.5.1.9 Modem Control Register                                        |     |

|    |        | 10.5.1.10 Line Status Register                                         |     |

|    |        | 10.5.1.11 Modem Status Register                                        |     |

|    |        | 10.5.1.12 Scratch-Pad Register                                         |     |

|    |        | 10.5.1.13 Infrared Selection Register                                  |     |

| 11 | Intern | nal Bus Performance Monitoring Unit (IBPMU)                            |     |

|    | 11.1   | Initializing the IBPMU                                                 |     |

|    | 11.2   | •                                                                      |     |

|    | 11.2   | 11.2.1 Monitored Events South AHB and North AHB                        |     |

|    |        |                                                                        |     |

|    |        | 11.2.2 Monitored SDRAM Events                                          |     |

|    | 44.0   | 11.2.3 Cycle Count                                                     |     |

|    | 11.3   | Register Descriptions                                                  |     |

|    |        | 11.3.1 Event Select Register                                           |     |

|    |        | 11.3.2 PMU Status Register (PSR)                                       |     |

|    |        | 11.3.3 Programmable Event Counters (PEC1)                              |     |

|    |        | 11.3.4 Programmable Event Counters (PEC2)                              |     |

|    |        | 11.3.5 Programmable Event Counters (PEC3)                              |     |

|    |        | 11.3.6 Programmable Event Counters (PEC4)                              |     |

|    |        | 11.3.7 Programmable Event Counters (PEC5)                              |     |

|    |        | 11.3.8 Programmable Event Counters (PEC6)                              |     |

|    |        | 11.3.9 Programmable Event Counters (PEC7)                              | 386 |

|    |        | 11.3.10  | ) Previous Master/Slave Register (PSMR)          |     |  |  |  |  |  |

|----|--------|----------|--------------------------------------------------|-----|--|--|--|--|--|

| 12 | GPIO   | GPIO     |                                                  |     |  |  |  |  |  |

|    | 12.1   | 5 1 1    |                                                  |     |  |  |  |  |  |

|    | 12.2   |          | GPIO as Interrupt Inputs                         |     |  |  |  |  |  |

|    |        |          | GPIO 14 and GPIO 15 as Clocks                    |     |  |  |  |  |  |

|    | 12.4   | Registe  | er Description                                   |     |  |  |  |  |  |

|    |        | 12.4.1   | GPIO Output Register                             |     |  |  |  |  |  |

|    |        | 12.4.2   | GPIO Output Enable Register                      |     |  |  |  |  |  |

|    |        | 12.4.3   | GPIO Input Register                              |     |  |  |  |  |  |

|    |        | 12.4.4   | GPIO Interrupt Status Register                   |     |  |  |  |  |  |

|    |        | 12.4.5   | GP Interrupt Type Register 1                     |     |  |  |  |  |  |

|    |        | 12.4.6   | GPIO Interrupt Type Register 2                   |     |  |  |  |  |  |

|    |        | 12.4.7   | GPIO Clock Register                              |     |  |  |  |  |  |

| 13 | Interr | upt Con  | troller                                          | 401 |  |  |  |  |  |

|    | 13.1   | Interrup | ot Priority                                      |     |  |  |  |  |  |

|    | 13.2   |          | ng FIQ or IRQ Interrupts                         |     |  |  |  |  |  |

|    | 13.3   |          | g and Disabling Interrupts                       |     |  |  |  |  |  |

|    | 13.4   |          | g Interrupt Status                               |     |  |  |  |  |  |

|    | 13.5   |          | ot Controller Register Description               |     |  |  |  |  |  |

|    |        |          | Interrupt Status Register                        |     |  |  |  |  |  |

|    |        |          | Interrupt-Enable Register                        |     |  |  |  |  |  |

|    |        | 13.5.3   | Interrupt Select Register                        |     |  |  |  |  |  |

|    |        | 13.5.4   | IRQ Status Register                              |     |  |  |  |  |  |

|    |        | 13.5.5   | FIQ Status Register                              |     |  |  |  |  |  |

|    |        | 13.5.6   | Interrupt Priority Register                      |     |  |  |  |  |  |

|    |        | 13.5.7   | IRQ Highest-Priority Register                    | 409 |  |  |  |  |  |

|    |        | 13.5.8   | FIQ Highest-Priority Register                    |     |  |  |  |  |  |

| 14 | Timer  | rs       |                                                  | 411 |  |  |  |  |  |

|    | 14.1   | Watch-   | Dog Timer                                        |     |  |  |  |  |  |

|    | 14.2   |          | tamp Timer                                       |     |  |  |  |  |  |

|    | 14.3   |          | II-Purpose Timers                                |     |  |  |  |  |  |

|    | 14.4   |          | Register Definition                              |     |  |  |  |  |  |

|    |        |          | Time-Stamp Timer                                 |     |  |  |  |  |  |

|    |        | 14.4.2   | General-Purpose Timer 0                          | 414 |  |  |  |  |  |

|    |        | 14.4.3   | General-Purpose Timer 0 Reload                   |     |  |  |  |  |  |

|    |        | 14.4.4   | General-Purpose Timer 1                          | 415 |  |  |  |  |  |

|    |        | 14.4.5   | General-Purpose Timer 1 Reload                   |     |  |  |  |  |  |

|    |        | 14.4.6   | Watch-Dog Timer                                  |     |  |  |  |  |  |

|    |        | 14.4.7   | Watch-Dog Enable Register                        | 417 |  |  |  |  |  |

|    |        | 14.4.8   | Watch-Dog Key Register                           | 417 |  |  |  |  |  |

|    |        | 14.4.9   | Timer Status                                     | 418 |  |  |  |  |  |

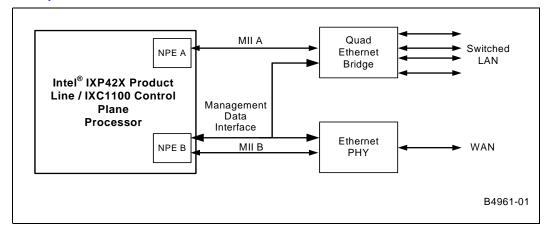

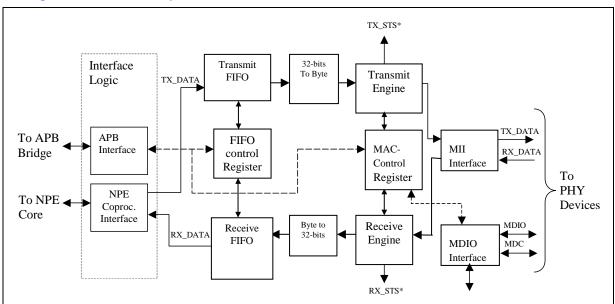

| 15 | Ether  | net MAC  | C A                                              | 419 |  |  |  |  |  |

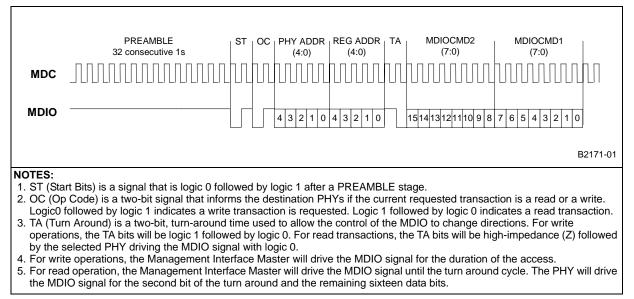

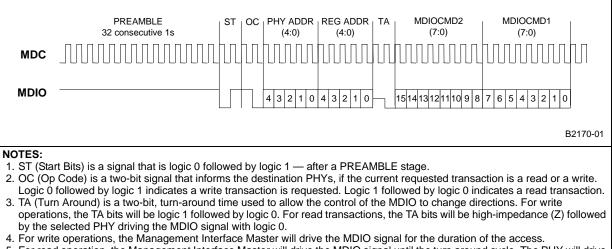

|    | 15.1   |          | et Coprocessor                                   |     |  |  |  |  |  |

|    |        |          | Ethernet Coprocessor APB Interface               |     |  |  |  |  |  |

|    |        |          | Ethernet Coprocessor NPE Interface               |     |  |  |  |  |  |

|    |        |          | Ethernet Coprocessor MDIO Interface              |     |  |  |  |  |  |

|    |        | 15.1.4   | Transmitting Ethernet Frames with MII Interfaces |     |  |  |  |  |  |

|      | 15.1.5  | Receiving Ethernet Frames with MII Interfaces | .426  |

|------|---------|-----------------------------------------------|-------|

|      | 15.1.6  | General Ethernet Coprocessor Configuration    | .428  |

| 15.2 | Registe | er Descriptions                               | .430  |

|      | 15.2.1  | Transmit Control 1                            | .431  |