These downloads are due to the work of many students and post doctoral associates who have worked over several years to create these items and make them available. Kindly refer to the papers linked here for more details.

Security

SHORE: Hardware/Software Method for Memory Safety Acceleration on RISC-V Dow, Hsu-Kang, Tuo Li, William Miles, and Sri Parameswaran In 2021 58th ACM/IEEE Design Automation Conference (DAC), pp. 289-294. IEEE, 2021.

Link to paper: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9586293

Link to Github: https://github.com/Lycheus/SHORE

2. RISC-V Rocket chip with flushx instruction (single instruction multiple flush)

Artifact: https://github.com/li3tuo4/rocket-chip/tree/flushxv3_0_1 (private, shared with DSTG and UNSW Lab)

Document (public version): Tuo Li, Bradley Hopkins, Sri Parameswaran: SIMF: Single-Instruction Multiple-Flush Mechanism for Processor Temporal Isolation. Online https://arxiv.org/abs/2011.10249

3. Smallest on-board power sensor for FPGAs (replacements for TDL's to perform power based attacks)

"VITI: A Tiny Self-Calibrating Sensor for Power-Variation Measurement in FPGAs" in IACR Transactions on Cryptographic Hardware and Embedded Systems

Paper: https://tches.iacr.org/index.php/TCHES/article/view/9311/8876

Link for download: Artifacts.zip

4. FPGA Countermeasure for softprocessor system - Based on changing clock frequencies - Dowlaod designs etc.

"SCRIP: Secure Random Clock Execution on Soft Processor Systems to Mitigate Power-based Side Channel Attacks" in IEEE/ACM International Conference on Computer-Aided Design (ICCAD).

Paper: https://ieeexplore.ieee.org/document/8942112

Link for Download: https://github.com/dnjayasinghe/scrip

5. FPGA Countermeasure - Download designs etc.

"RFTC: Runtime Frequency Tuning Countermeasure Using FPGA Dynamic Reconfiguration to Mitigate Power Analysis Attacks" in DAC '19

Paper: https://dl.acm.org/doi/10.1145/3316781.3317899

Link for Download: https://github.com/dnjayasinghe/RFTC

6. FPGA Countermeasure - Download Designs etc.

"UCloD: Small Clock Delays to Mitigate Remote Power Analysis Attacks", in IEEE Access

Paper: https://ieeexplore.ieee.org/abstract/document/9499089

Link for Download: https://github.com/dnjayasinghe/UCloD

BioInformatics

1. High speed Analysis for nanapore signal analysis

"GPU accelerated adaptive banded event alignment for rapid comparative nanopore signal analysis" in BMC Bioinformatics

https://bmcbioinformatics.biomedcentral.com/articles/10.1186/s12859-020-03697-x

https://github.com/hasindu2008/f5c/

"The speeds appear mind-boggling to me. Like science fiction. I had no idea these things have progressed so fast." - Dr Thomas A. Hall (Chief Scientific Officer at Janus-I Science, USA) who executed f5c on an embedded computer

Dr Johnny Debebe (researcher from the University of Nottingham) who executed f5c on a cluster node stated "I have to say the speed has left me speechless and in shock. I was expecting a speed improvement, but this is something much more than an "improvement".

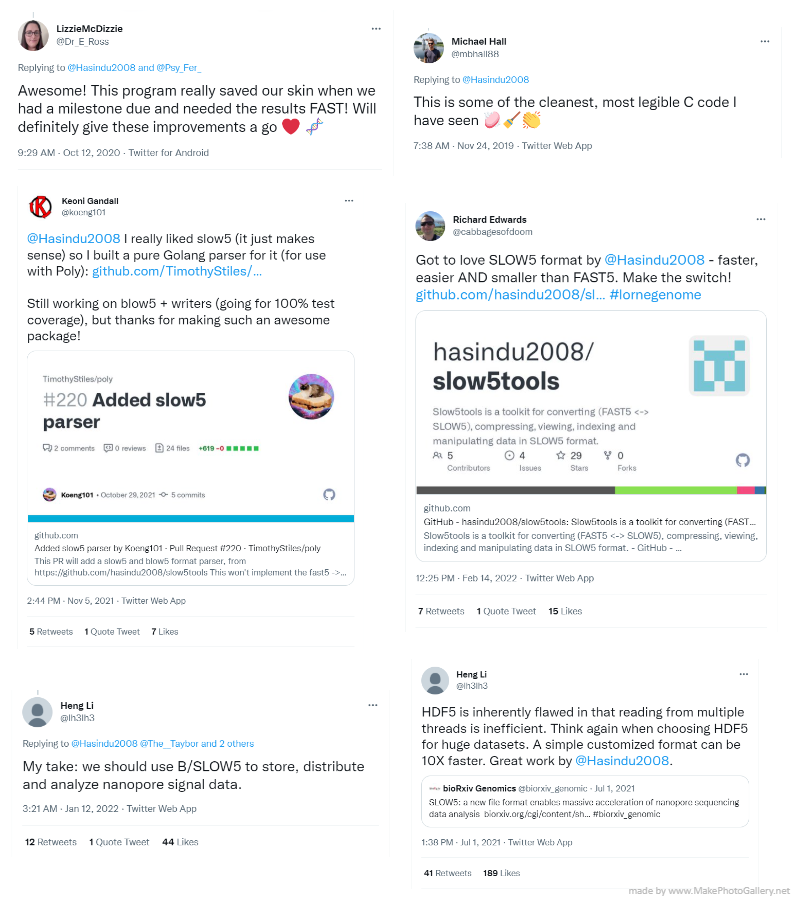

2. SLOW5 software: replacement for FAST5 file format - 30 times faster and requires 40% less diskspace

"Fast nanopore sequencing data analysis with SLOW5" in nature biotechnology

https://www.nature.com/articles/s41587-021-01147-4

https://github.com/hasindu2008/slow5tools

General Downloads

ZCU102 FPGA port of RISC-V Rocket chip

Artifact: https://github.com/li3tuo4/rc-fpga-zcu.git

Document: Quick tutorial https://github.com/li3tuo4/rc-zcu102-tutorial/blob/master/quickstart.pdf

created with

Website Builder Software .